一、概述

静态时序分析(简称STA)是用来验证数字设计时序的技术之一,另外一种验证时序的方法是时序仿真,时序仿真可以同时验证功能和时序。“时序分析”这个术语就是用来指代“静态时序分析“或”时序仿真“这两种方法之一,简单来说,时序分析的目的就是为了解决设计中的各种时序问题。

时序分析=动态时序分析+静态时序分析。

动态时序分析简单讲就是gate-level simulation,仿真对象是netlist+sdf,通过SDF反标,得到gate跟net的delay,通过输入大量的激励来验证电路的功能。动态时序分析通常覆盖以下几方面:典型应用场景的功能验证、频率的动态切换、跨时钟域信号是否正确同步、PMU上电及断电的顺序是否正确并满足相应的时序要求、multi-cycle等特别逻辑的功能是否正确。但动态时序分析不是『完备』的分析方法,如果要得到100%的仿真覆盖率基本是天方夜谭。此外,基于逻辑仿真的验证是无法处理由串扰、噪声以及片上变化(on-chip variations)所带来的的影响的。

STA被称为静态的原因是其对于设计的分析是静态地执行的,并不依赖于施加在输入端口上的激励。给定了一个设计、输入时钟以及外部环境,STA的目的就是验证这个设计是否能够运行在预期的速度,即这个设计可以安全地运行在给定的时钟频率下且没有时序违例。

1、STA基本流程

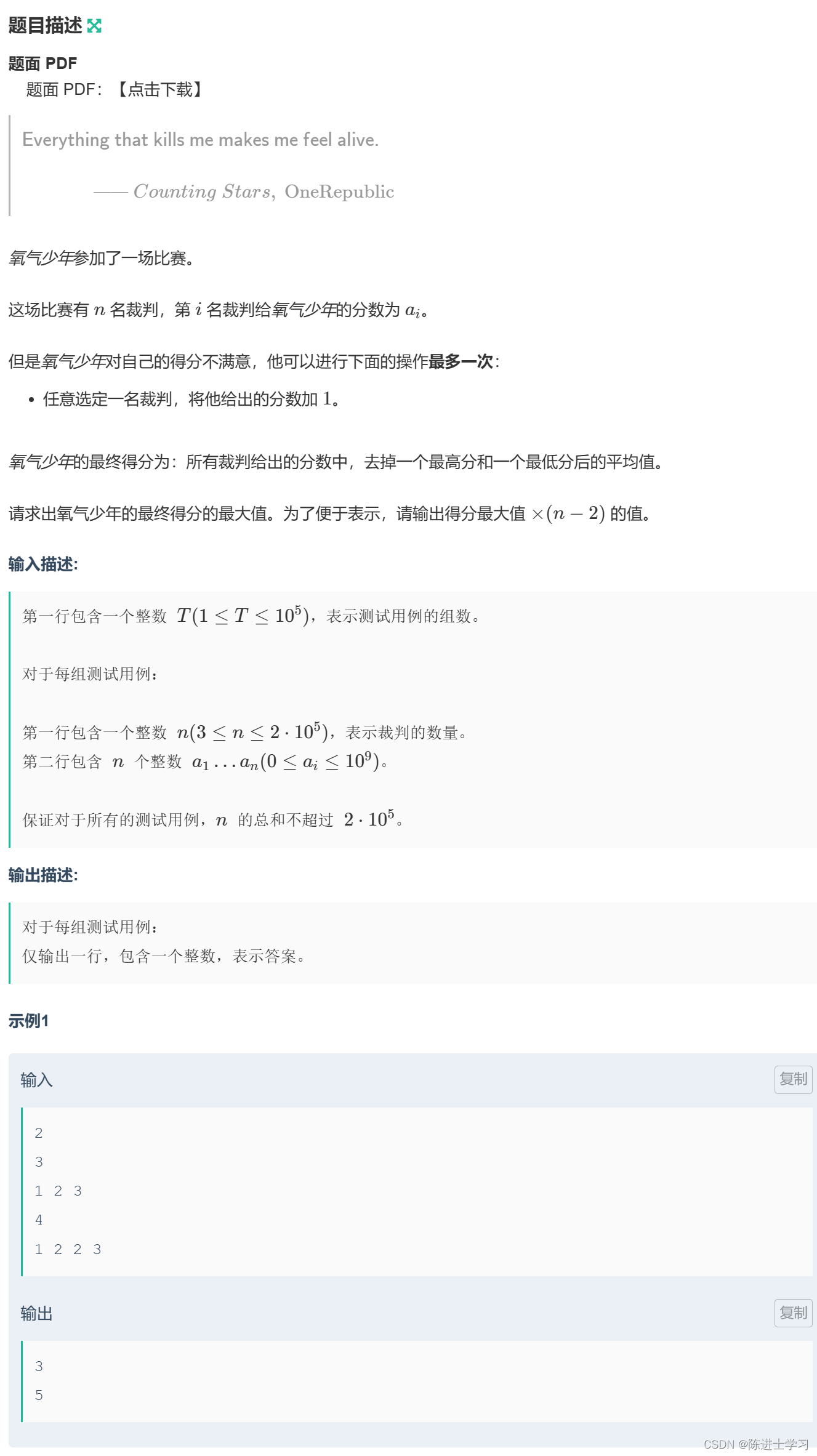

在CMOS数字设计流程中,STA会在实现的各个阶段里被使用到。下图展示了基本的流程:

可以看到,STA是在综合、逻辑优化和物理设计步骤中的每个步骤之后完成的。 实际上,这些步骤中的每一个都在其功能范围内集成有STA。将RTL级的设计综合到门级后,可以根据以下条件在门级网表上执行静态时序分析:

- 互连线的建模方式:理想互连线,线负载模型,具有近似RC值的全局布线以及具有精确RC值的实际布线。

- 时钟的建模方式:理想时钟(零延迟)或是传播时钟(实际延迟)。

- 是否考虑信号之间的耦合效应以及是否分析串扰噪声。

大致做法为:用startpoint跟endpiont将电路切割成不可计数条timing path——静态时序分析的基本对象。每条timingpath都有一个start point、一个end piont、若干个基本逻辑门单元(cell)、若干条连线(net),STA要做的就是:根据cell的输入transition跟输出load,从对应的工艺库(library)里直接读取cell的延时(delay)跟输出的transition或从工艺库里读取相应的参数依据CCS模型计算cell的delay跟输出的transition;根据读入的SPEF将R/C值反标到net上,并根据net delay计算模型计算net的delay;得到整条timingpath的delay后跟用户通过SDC设置的目标delay进行比对,以确定该条timing path是否满足需求。

在在逻辑级(未进行物理设计的门级),STA采用模型为:1. 理想的互连线或者基于线负载模型的互连线;2. 带有延迟和抖动估计值的理想时钟。在物理设计阶段,除了上述模型,STA还可采用以下模型:1. 具有近似估计值的全局布线的互连线、具有近似寄生参数提取值的实际布线的互连线、具有可以签收(signoff)精度寄生参数提取值的实际布线的互连线;2. 实际的时钟树;3. 包括串扰的影响或者不包括串扰的影响。

2、STA局限性

虽然时序分析和噪声分析在所有可能的情况下都可以很好地分析设计中的时序问题,但在最新的技术中仍然无法完全使用STA替代仿真, 这是因为时序验证的某些方面还无法完全被STA捕获并得到验证。

静态时序分析的局限性包括以下几点:

- 复位顺序:检查所有触发器在异步或同步复位后是否都复位为所需的逻辑值,这是无法使用静态时序分析来检查的。 芯片可能不会退出复位状态。 这是因为某些声明(例如信号的初始值)没有被综合,仅在仿真过程中被验证。

- 未知态X的处理:设计中的未知态X导致不确定的值在整个设计中传播,是无法使用STA进行检查。 即使STA内的噪声分析可以分析整个设计中的毛刺,但作为纳米级设计中基于仿真的时序验证的一部分,毛刺分析和传播的范围也与对未知态X的处理大为不同。

- PLL设置:PLL的配置可能未被正确加载或设置。

- 跨异步时钟域:STA不检查是否使用了正确的时钟同步器,需要其他工具来确保在任何跨异步时钟域的地方都有正确的时钟同步器。

- IO接口时序:可能仅根据STA约束无法规定IO接口要求。。

- 模拟模块和数字模块之间的接口:由于STA不处理模拟模块,因此验证方法需要确保这两种类型的模块之间的连接正确。

- 伪路径(false path):逻辑可能永远无法传播通过的路径称为false path,这种时序路径实际上不会被执行。当在设计中指定了正确的时序约束(包括伪路径和多周期路径约束)时,STA结果的质量会更好。 在大多数情况下,设计人员可以利用设计的固有知识并指定约束条件,以便在STA期间消除伪路径。

- FIFO指针不同步:当两个预期要同步的有限状态机实际上不同步时,STA无法检测到该问题。

- 时钟同步逻辑:STA无法检测到时钟生成逻辑与时钟定义不匹配的问题。 STA会假设时钟生成器将提供时钟定义中指定的波形。 对时钟生成器逻辑的优化可能很糟糕,比如会导致在未适当约束的路径之一上插入较大的延迟,又或者,添加的逻辑改变了时钟的占空比。而STA无法检测到这些潜在情况中的任何一个。

- 跨时钟周期的功能行为:STA无法建模或仿真跨时钟周期变化的功能行为。尽管存在诸如此类的问题,STA依然适合被广泛用于验证设计的时序,而时序仿真可作为备用方法来检查极端情况,并且能够更简单地验证设计的功能正确。

在大多数实际设计中,功耗和时序通常是密不可分的。设计人员希望使用更快(或更高速度)的单元来满足速度方面的考虑,但可能会受到功耗的限制。 在选择工艺技术和单元库时,功耗是一个重要的考虑因素。

二、概念

1、CMOS单元建模

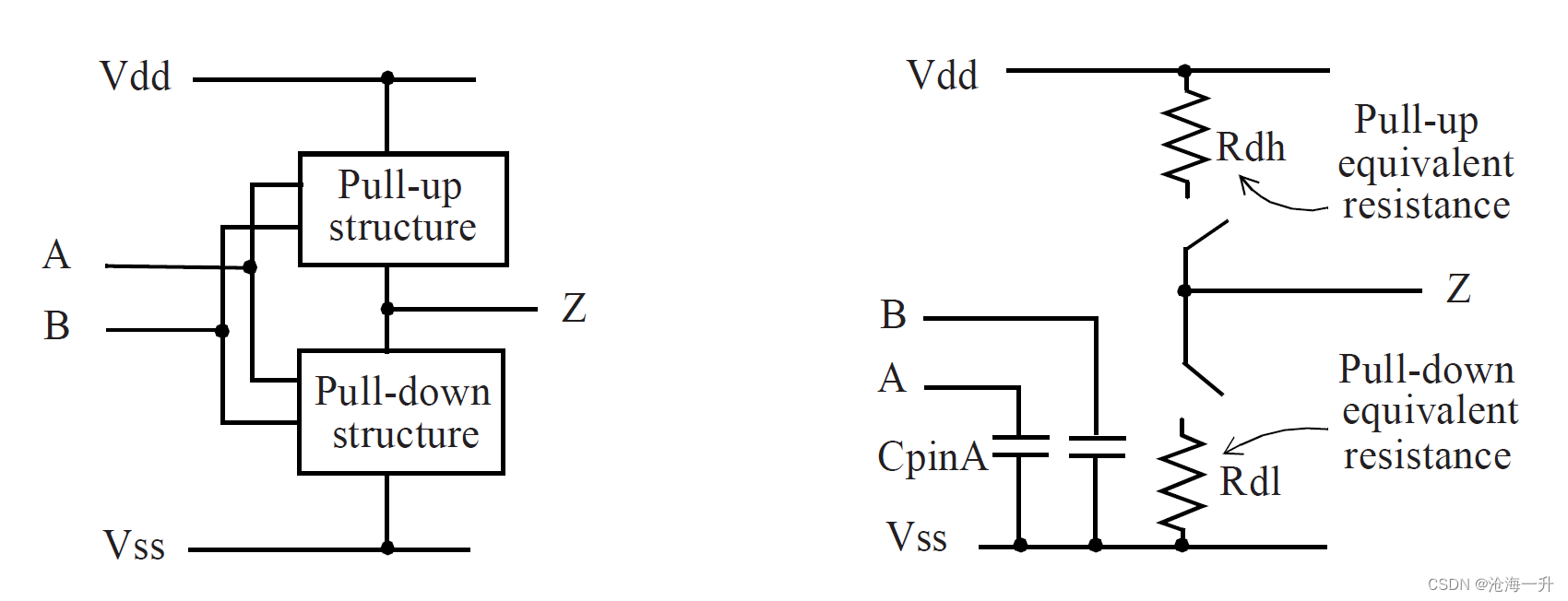

STA的主要工作是计算电路网络的延时,如今的电路网络还是由CMOS cell和net组成的,所以STA所要计算的延时仍是电容的充放电时间。所以要搞STA,首先需要明白如何计算CMOS cell delay跟net delay。

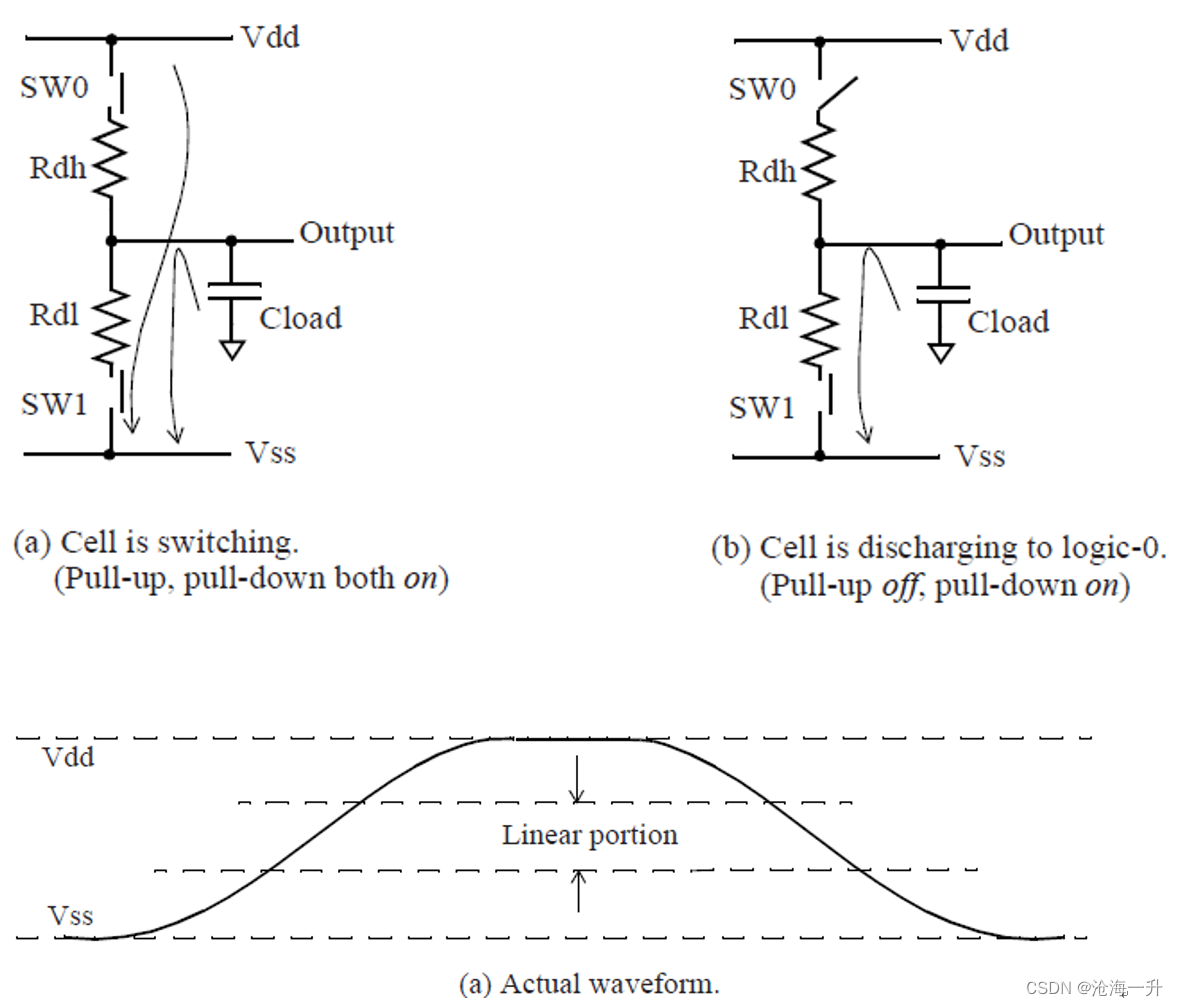

STA所有的行为都可以概括为建模和解方程,在STA眼里电路网络就是一张RC网络。cell被模拟成输入电容、输出电容、上拉电阻和下拉电阻。输入电容为前一级驱动的负载,输出电容为自身的负载,上拉电阻/下拉电阻决定了该cell对负载电容充/放电电流的大小,从而决定了该cell的负载能力,即驱动能力。

一个cell的负载,除了自身的输出电容,还包括所驱动cell的输入电容和所有相关连线的电容电阻,所谓的延时就是给负载电容充/放电的时间,根据电容充放电公式:Vout=Vdd * [1-e(-t/RC)],乘积(Rdh * Cload)称为RC时间常数(RC time constant)。显然,在工作电压一定的情况下,充放电时间完全由RC决定,所以如何构建RC模型成了STA的核心。

1)传播延时 (propagation delay)

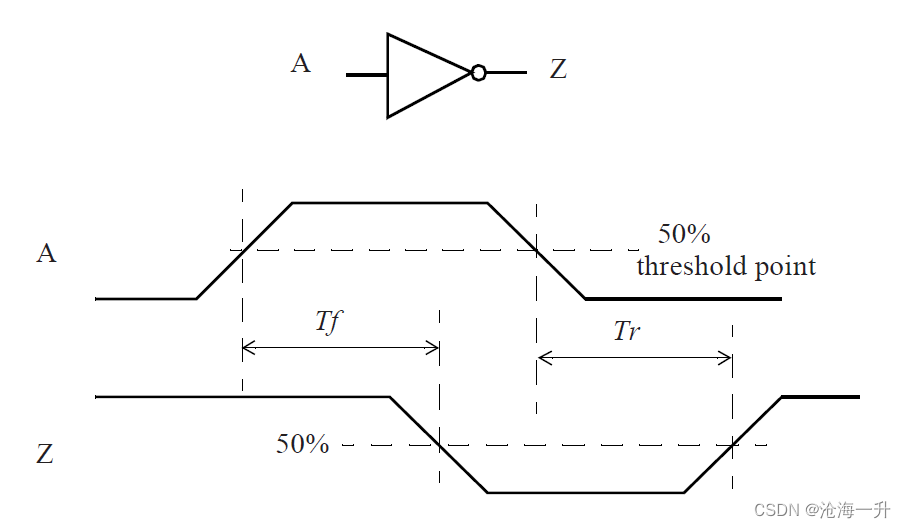

如今所用的STA方法学会分别计算cell delay跟net delay,而cell delay是由电平切换波形上的某些测量点定义的。

#输入端口下降沿的阈值点

input_threshold_pct_fall:50.0;

#输入端口上升沿的阈值点

input_threshold_pct_rise:50.0;

#输出端口下降沿的阈值点

output_threshold_pct_fall:50.0;

#输出端口上升沿的阈值点

output_threshold_pct_rise:50.0;这四个attribute决定了cell delay是如何衡量的,通常这四个值都是50%,所表述的意思是:从输入信号电压上升/下降到工作电压的50%到对应的输出信号电压翻转为工作电压的50%之间的时间为cell delay。

在实际STA中,会根据cell的输入transition和输出load通过查表从library中得到cell delay和输出transition,cell delay的计算分为三部分:library的生成、输入transition的计算、输出load的计算。library不论是来自Foundary厂还是各大厂自己定制,都是经过一系列的类似于SPICE仿真流程生成的。

2)压摆率 (slew rate)

Transition的计算是逐级递进的,port的transition由硅农在SDC中指定,如set_driving_cell,第一级Port的transition来自driving cell的output transition,经由net的RC网络到达下一级cell的input pin,再从library中查得该级cell的output transition依次类推。

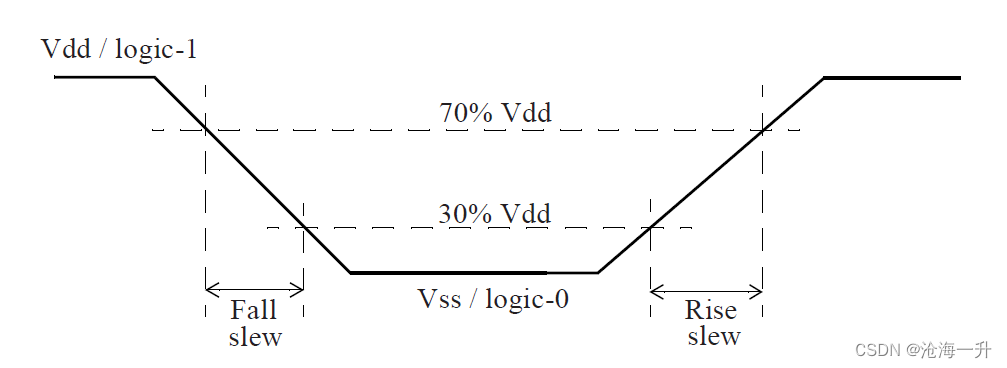

在这里就得提到压摆率了,压摆率(slew rate)的定义是电压转换速率。在STA中,通常会根据电平转换的快慢来衡量上升波形或下降波形。 压摆(slew)通常是根据转换时间(transition time)来定义的,转换时间是指信号在两个特定电平之间转换所需要的时间。转换时间实际上就是压摆率的倒数,因此转换时间越大,压摆率就越低,反之亦然。

根据CMOS单元输出端典型波形:靠近Vdd和Vss两端的波形是渐近的,很难确定过渡时间的确切起点和终点。因此,一般使用指定的阈值电压来规定过渡时间计算的起点和终点。例如,压摆阈值设置可以如下所示:

#下降沿的阈值点

slew_lower_threshold_pct_fall:30.0;

slew_upper_threshold_pct_fall:70.0;

#上升沿的阈值点

slew_lower_threshold_pct_rise:30.0;

slew_upper_threshold_pct_rise:70.0;同样在library的表头有这4个attribute,用以标示如何衡量rise/fall transition time。上面指从工作电压的30%上升到工作电压的70%为rise transtion time,从工作电压的70%下降到工作电压的30%为fall transition time。

输出load包括cell自身的输出电容、连线电阻电容及其所驱动cell的输入电容,输出load的计算,关键在于如何建模,如今最常用的是elmore模型,这里不做细谈。

2、时钟相关

1)信号偏斜(skew)

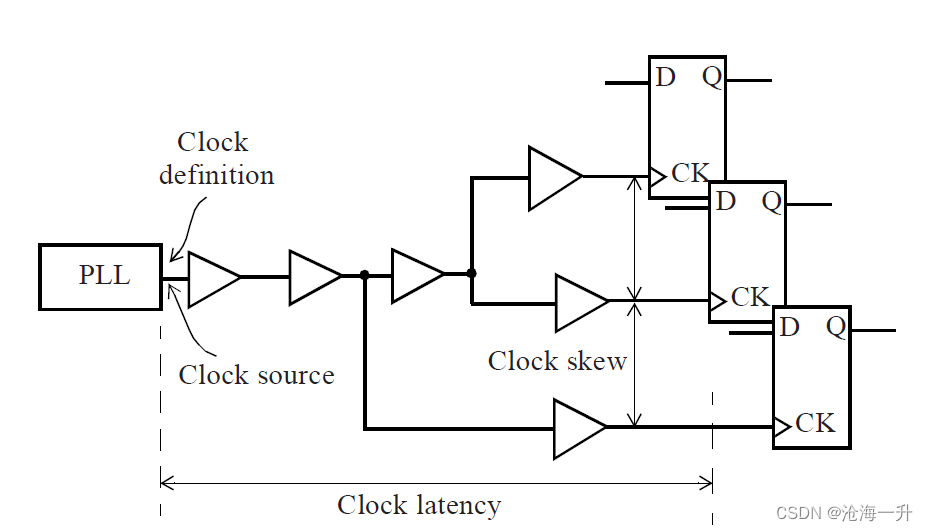

偏斜(skew)是指两个或多个信号(数据或者时钟)之间的时序之差。。时钟延迟(clock latency)是指从时钟源到终点所花费的总时间,时钟偏斜(clock skew)是指到达不同时钟树终点的时间差。

可以使用set_clock_latency命令显式地指定时钟树的延迟:

set_clock_latency 2.2 [get_clocks BZCLK]上述命令规定了时钟树BZCLK的上升沿延迟(rise latency)和下降沿延迟(fall latency)均为2.2ns。注意,如果两个延时值不同,可以使用选项-rise和-fall来分别指定延时值。

时钟树的时钟偏斜可以借助set_clock_uncertainty命令显式指定时钟不确定度的值来描述:

set_clock_uncertainty 0.250 -setup [get_clocks BZCLK]

set_clock_uncertainty 0.100 -hold [get_clocks BZCLK] set_clock_uncertainty命令为时钟沿的出现指定了一个窗口。时钟边沿时序的不确定性将考虑多个因素,例如时钟周期抖动(jitter)和用于时序验证的额外裕量(slack)。每个实际的时钟源都有一定的抖动量,即一个时间窗口,在该窗口内都可能会出现时钟沿。时钟周期抖动取决于所使用的时钟发生器的类型。实际上是不存在理想时钟的,也就是说,所有时钟都具有一定的抖动

量,并且在指定时钟不确定度(clock uncertainty)时应包括时钟周期抖动。

在时钟树被实现(implement)之前,时钟不确定度还必须包括预期的时钟偏斜。

可以为建立时间(setup time)检查和保持时间(hold time)检查指定不同的时钟不确定度。保持时间检查不需要将时钟抖动包括在内,因此通常为保持时间检查指定较小的时钟不确定度。

2)时序弧(timing arc)

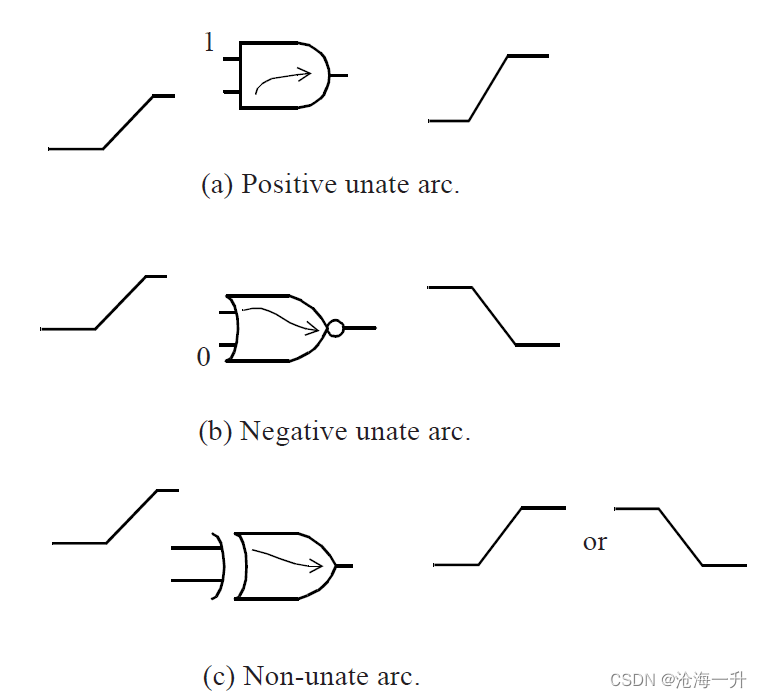

每个逻辑单元都有多个时序弧(timing arc)。像触发器之类的时序逻辑单元除了有从时钟引脚到输出引脚的时序弧,还有相对于时钟引脚的数据引脚时序约束(timing constraint)。每个时序弧都具有特定的时序敏感(timing sense),即输出如何针对输入的不同跳变类型而变化。

在非单边(non-unate)时序弧中,仅仅从一个输入引脚的跳变方向是无法确定输出引脚电平将如何跳变的,还要取决于其他输入引脚的状态 。单边性(unateness)对于时序很重要,因为它指定了输入引脚上电平跳变沿将如何通过逻辑单元传播以及将如何出现在逻辑单元的输出引脚上。

3)最小与最大时序路径

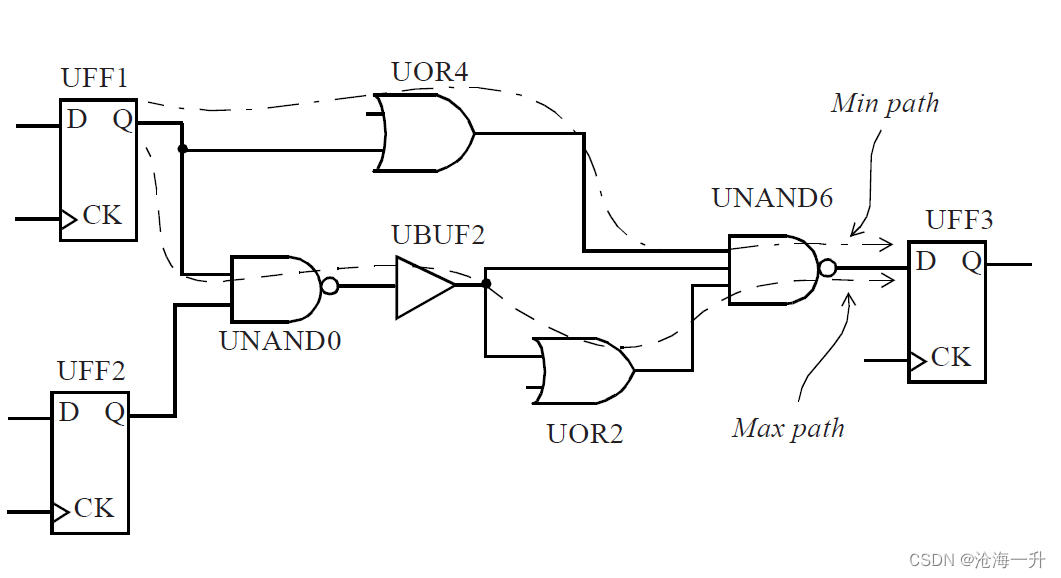

逻辑通过逻辑路径传播的总延迟称为路径延迟(path delay),包括了逻辑路径中经过各个逻辑单元(cell)和网络走线(net)的延迟。通常,逻辑想要传递到一个终点可能有不止一条逻辑路径可走,所经过的实际路径取决于逻辑路径上其他输入的状态。

由于有多个到达逻辑终点的路径,因此可以得出到达逻辑终点的最大时序和最小时序,对应于最大时序和最小时序的路径分别称为最大路径(late path)和最小路径(early path)。

从触发器到触发器的路径时,其中一个触发器发起(launch)数据,另一个触发器捕获

(capture)数据。在这种情况下,发起数据被称为发起触发器(launch flip-flop),捕获数据,因被称为捕获触发器(capture flip-flop)。

3、工作环境

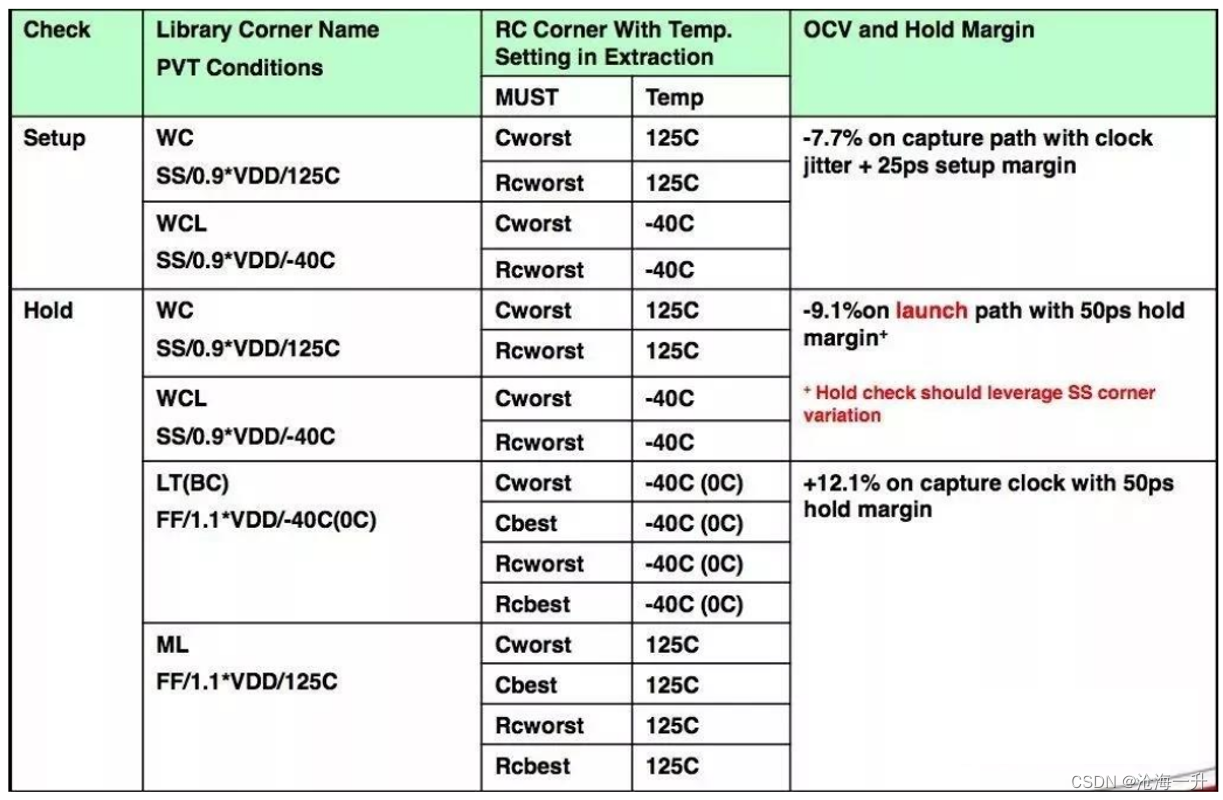

一颗健壮的IC芯片需要适应于他所在应用范围内变化的温度、电压,他需要承受制造工艺的偏差,这就需要在设计实现过程中考虑这些变化的温度、电压和工艺偏差。在STA中,用library PVT、RC corner跟OCV来模拟这些不可控的随机因素。在每个工艺结点,通过大量的建模跟实测,针对每个具体的工艺,foundary厂都会提供一张推荐的timingsignoff表格, 建议需要signoff的corner及各个corner需要设置的ocv跟margin。这些corner能保证大部分芯片可以承受温度、电压跟工艺偏差,一个corner=libraryPVT+ RC corner + OCV,本节主要说明library PVT。

PVT,也即是工作条件(operating condition)定义为工艺(process)、电压(voltage)和温度(temperature)的组合。逻辑单元延迟和互连线的走线延迟是根据特定的工作条件计算的。半导体代工厂(foundry)为数字设计提供了3种加工工艺模型:慢速(slow)工艺模型,典型(typical)工艺模型和快速(fast)工艺模型

实际实现过程中,在library的表头会有operating condition的定义,比如『ss0p81vm40c』是这个operating condition的名字,通常这个名字是有意义的,它会标示出该lib对应的电压跟温度,如0p81对应于voltage:0.81,m40c对应于temperature:-40度。

接下来详细说说三个方面:

P-process:IC制造工艺本身的不完美,使得制造偏差不可避免,在library中会用一个百分比来表示工艺偏差,如process:1表示没偏差。在沉积或参杂过程中,杂质浓度密度、氧化层厚度、扩散深度都可能发生偏差,从而导致管子的电阻跟阈值电压发生偏差;光刻过程中由于分辨率的偏差会导致管子的宽长比产生偏差。而这些偏差,都会导致管子性能的差异。

V-voltage:管子的延时取决于饱和电流,而饱和电流取决于供电电压。且不论多电压域芯片,就单电压芯片而言,电池的供电电压本身就在一个范围内变化,再加上片外或片上voltage regulator的误差、再加上IR,一个芯片上的每个管子都可能工作在不同电压下,从而性能也有所差别。

T-temperature:在日常操作中,IC芯片必须适应温度不恒定的环境,当芯片运行时,由于开关功耗、短路功耗和漏电功耗会使芯片内部的温度发生变化。温度波动对性能的影响通常被认为是线性的,但在深亚微米温度对性能的影响是非线性的。对于一个管子,当温度升高,空穴/电子的移动速度会变慢,使延时增加,而同时温度的升高也会使管子的阈值电压降低,较低的阈值电压意味着更高的电流,因此管子的延时减小。而通常温度升高对空穴/电子移动速度的影响会大于对阈值电压的影响,所以温度升高管子的延时呈增加趋势。但是并不是温度越低管子的延时就越小,晶体管有温度翻转效应,当温度低到某个值之后,随着温度的降低,管子的延时会增加,至于温度翻转点跟具体的工艺相关。

在做STA分析时,operating condition通常通过lib读入,如果多个library中的operating condition不同,通常用第一个读入的library中定义的operating condition。可以使用set_operating_conditions命令明确指定设计的工作条件。

set_operating_conditions “WCCOM” -library mychip

#使用了在单元库mychip中定义的名为WCCOM的工作条件