逻辑综合

定义

逻辑综合就是将前端设计工程师编写的RTL代码,映射到特定的工艺库上,通过添加约束信息,对RTL代码进行逻辑优化,形成门级网表。约束信息包括时序约束,线载模型约束,面积约束,功耗约束等。

逻辑综合的转换过程

逻辑综合主要包含以下三个方面:翻译,门级映射,逻辑优化。

Synthesis = Translation + Gate Mapping+ Logic Optimization

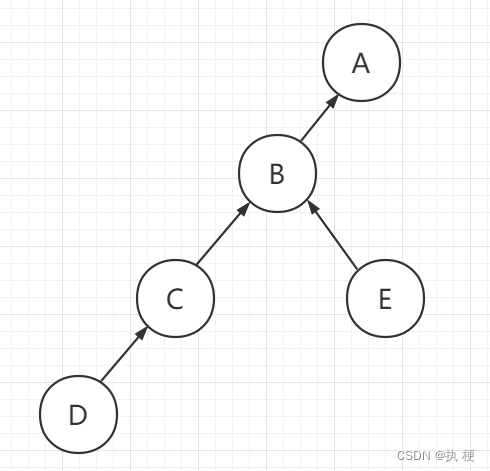

Translation:将Verilog或者VHDL代码转换成GTECH网表(通用的网表格式,与工艺库没关系),然后会转换成和工艺库相关的网表设计文件。

Gate Mapping:将GTECH网表文件进行实际门级电路的映射,映射到标准单元的目标库中,此时映射的网表是没有优化的。

Logic Optimization:根据添加的约束信息,对设计进行力所能及的优化。

逻辑综合流程

首先要加载逻辑工艺库和RTL设计文件,然后要定义相关时序约束和设计规则的约束,然后进行综合设计,并分析综合后的结果,(时序报告,面积报告,功耗报告),通过分析报告检查当前设计是否符合设计要求,如果不符合需求,则修改RTL代码或者约束使得设计满足设计需求,然后写出设计数据,导出ddc文件交给后端进行设计。

Step 1:启动DC工具

GUI界面方式

在终端中输入以下指令可以启动界面化的DC工具:

design_vision

终端方式

在终端中使用下面的命令可以在终端中使用DC工具:

dc_shell

在终端模式下可以使用tcl脚本优化工具使用的效率,例如:

dc_shell -f syn.tcl | tee -i syn.log

使用-f打开脚本文件,然后将中间过程中的相关信息保存到syn.log文件中。

Step 2:设置工作环境

设置search_path

为了缩短综合过程中使用的文件的路径,DC在search_path目录下查找指定的设计和库文件,通常包括Verilog、库和脚本的目录,用户可以将目录添加到默认列表中。

例如:

set_app_var search_path "$search_path ./rtl ./scripts ./libs"

设置library

library主要包含两个库target library和link library。

target library:一般就是std cell db;放的是标准单元工艺库; 是综合目的库,存放的是需要映射的逻辑单元。一般为standard cell library & io cell library 的type;是DC在mapping时将设计映射到特定工艺所使用的库,就是使用目标库中的元件综合成设计的门级网表。用于综合过程中生成门级网表使用的,DC优化时可选择的最小门级电路(满足当前DRC,时序和逻辑功能需求),使用的是由硅供应商提供的*.db文件。

例如:

set_app_var target_library 90nm_typical.db

link library:link_library是链接库,用于“解析”网表或 RTL 中的实例化参考,它是DC在解释综合后网表时用来参考的库。一般情况下,它和目标库相同;当使用综合库时,需要将该综合库加入链接库列表中。

set_app_var target_library 90nm_typical.db

set_app_var link_library "$target_library"

Step 3:加载设计文件、设计约束

read verilog

加载默认GTECH库和用户指定的链接库,DC工具将Verilog RTL转换为Getch Netlist,当DC工具把Verilog设计文件加载进来时,已经实现了Getch 网表转换的转换。

例如:

read_verilog "TOP.v A.v B.v"

current design

使用current design可以指定当前设计的顶层,让DC工具知道哪个模块是分层设计的顶级设计,设计中除去顶层可能有多个模块。

current_design TOP

timing constrain

完成上述步骤的指定后,可以向当前设计中加入时序约束,时钟约束的目的是为了调整时钟树。

clock period

可以通过约束调整设计的期望时钟频率,例如,如果想指定时钟信号的工作频率为500MHz,使用如下约束(以下约束的时间单位均为ns):

create_clock -period 2 [get_ports CLK]

clock skew

可以通过约束进行调整时钟偏移的时间,例如,设置时钟的上升沿的偏移时间为0.3ns可以使用以下约束:

set_clock_uncertainty -setup 0.3 [get_clocks CLK]#时钟偏移时间

clock transition

在实际电路中,信号反转时都不是直上直下的,都需要反转时间,这里可以通过约束设置时钟反转的时间,例如,设置时钟信号反转时的最大时间为0.15ns可以使用以下约束:

set_ clock_transition -max 0.15 [get_clocks CLK]#信号反转时间

clock latency

添加关于latency的约束,约束latency的命令是set_clock_latency。该约束设置的延迟时间是芯片引脚到芯片驱动的器件(例如flip-flop)的clock输入的delay:

set_clock_latency -max 0.7 [get_clocks CLK]

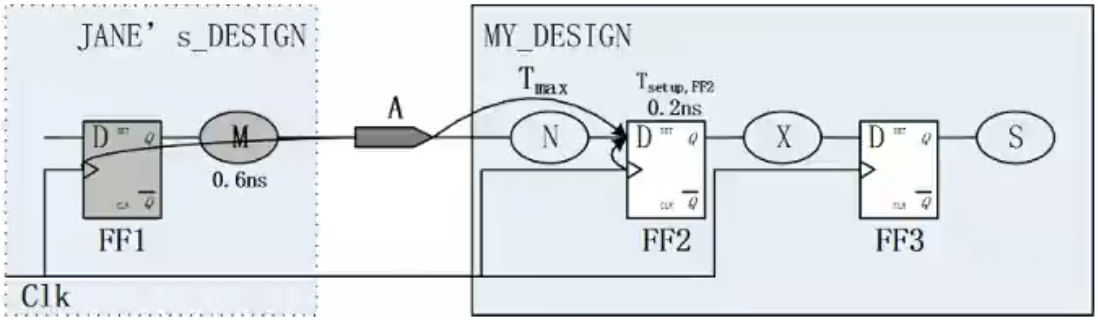

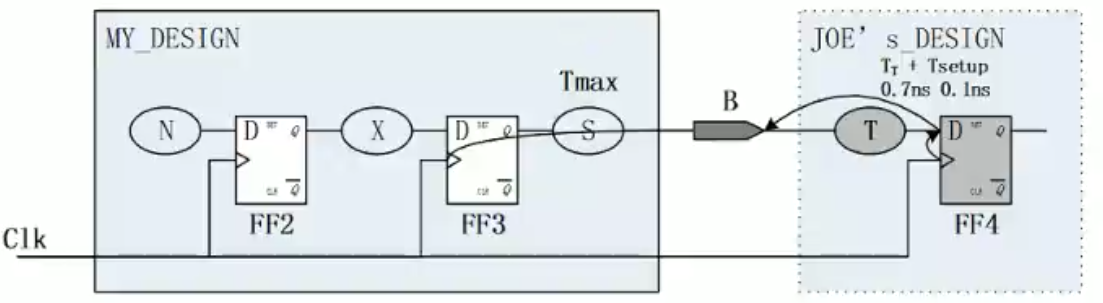

input delay

前级其他

set_input_delay -max 0.6 -clock Clk [get _ports A]

output delay

set_output_delay -max 0.8-clock Clk [get_ports B]

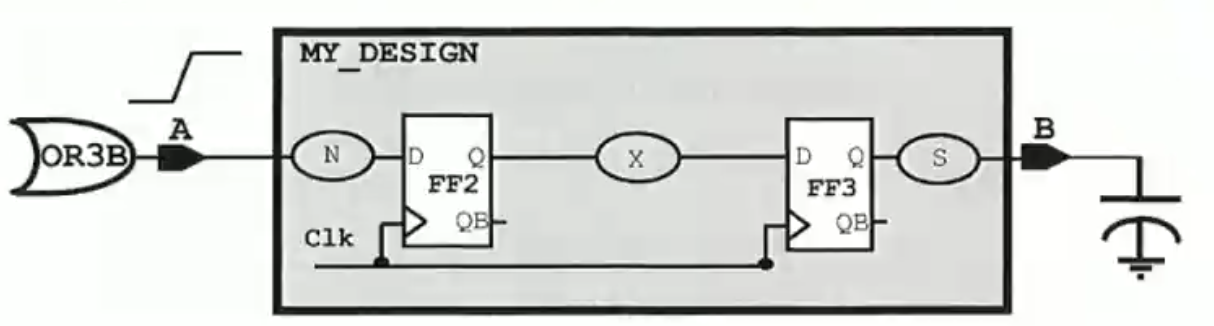

environmental constrain

环境约束主要包括线载和容载的相关约束。

输入端口上的上升和下降转换时间会影响输入门的单元延迟。

set_input_transition 0.12 [get_ports A]

输出端口上的电容加载会影响输出驱动器的转换时间,从而影响单元延迟。

set_load [expr {30.0/1000}] [get_ports B]

Step 4:启动编译

完成约束设计后,可以使用compile/compile_ultra对当前设计进行编译,compile_ultra指令会进最大程度去编译。

在DC工具进行编译时,会从以下三个方面对当前设计进行相关优化。

- 结构层综合优化,也可以叫架构层面的优化

- 逻辑层级优化,也可以叫做网表层级的优化

- 门级优化,或者叫做mapping优化

在综合优化的时,会在满足时序的前提下尽可能做到面积最小。

Step 5:分析报告

report_qor

完成综合后,会生成一个报告quality of result(qor),可以通过报告查看综合的结果,报告中会报告时序,标准单元的使用数量,以及单元占用面积大小,这里有点类似FPGA开发时的综合与布局布线后生成的资源消耗和功耗的图表。

report_timing

时序分析报告将报告DC静态时序分析工具的结果,将设计分解为单独的时钟路径,并分析每条时钟路径的最大延时。

Step 6:输出设计

完成对当前设计的结果,即可导出相关设计文件。*.sdc文件是在设计时候编写的相关约束文件,*.ddc文件是约束文件加上设计文件得到门级网表,*.gv文件是.v文件的网表,通常在综合后还会生成*.sdf文件,时延文件,*.gv文件和*.sdf文件一起使用可以做后仿真设计。

write_sdc my_design.sdc

write -f ddc -hier -output my ddc.ddc

write f verilog -hier -outout my_design.gv

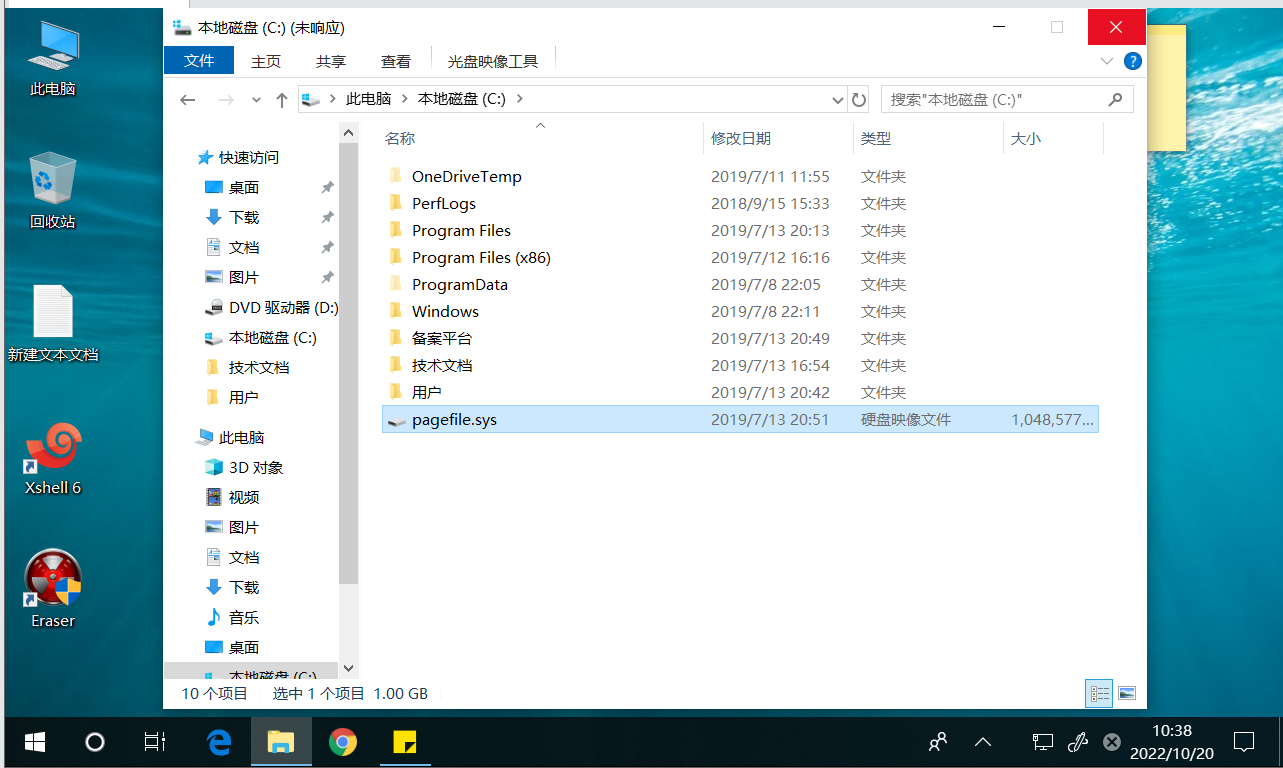

图形化方式使用DC工具

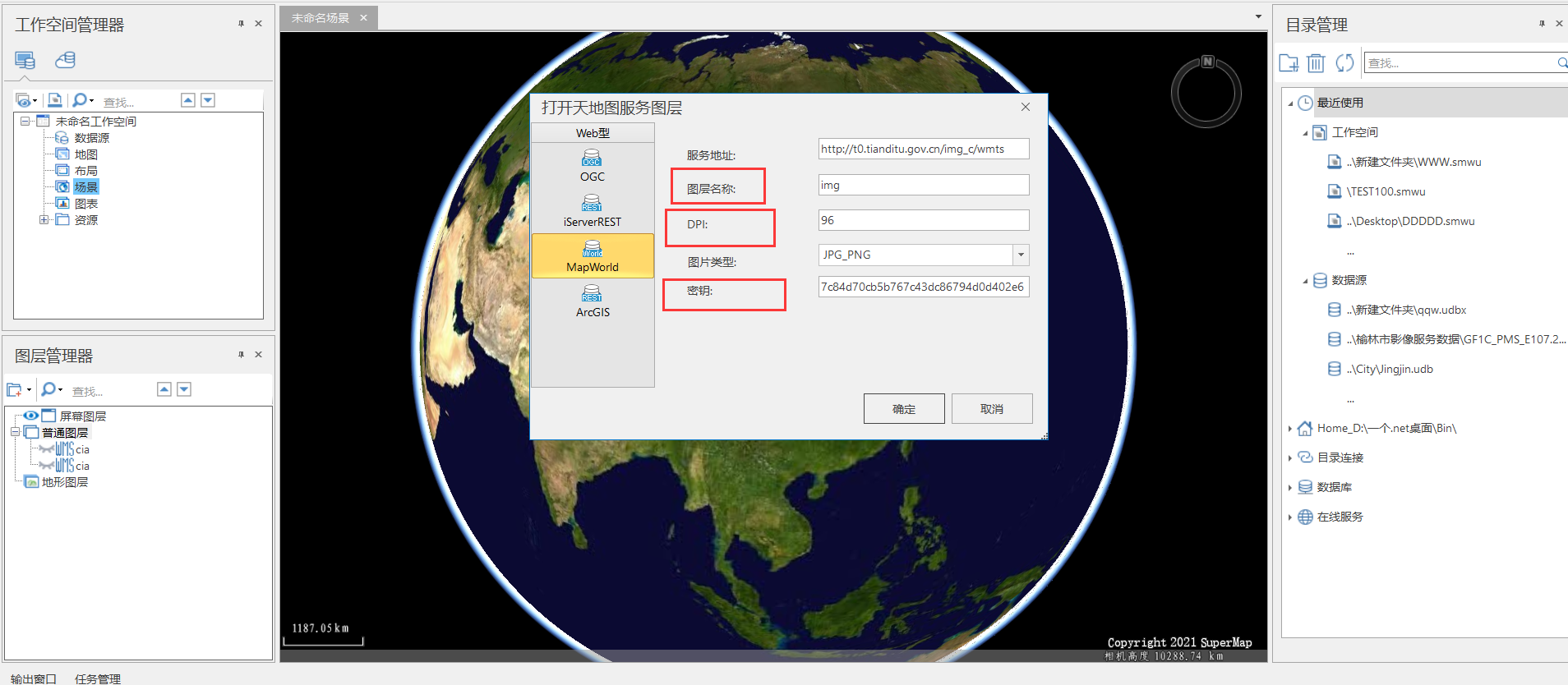

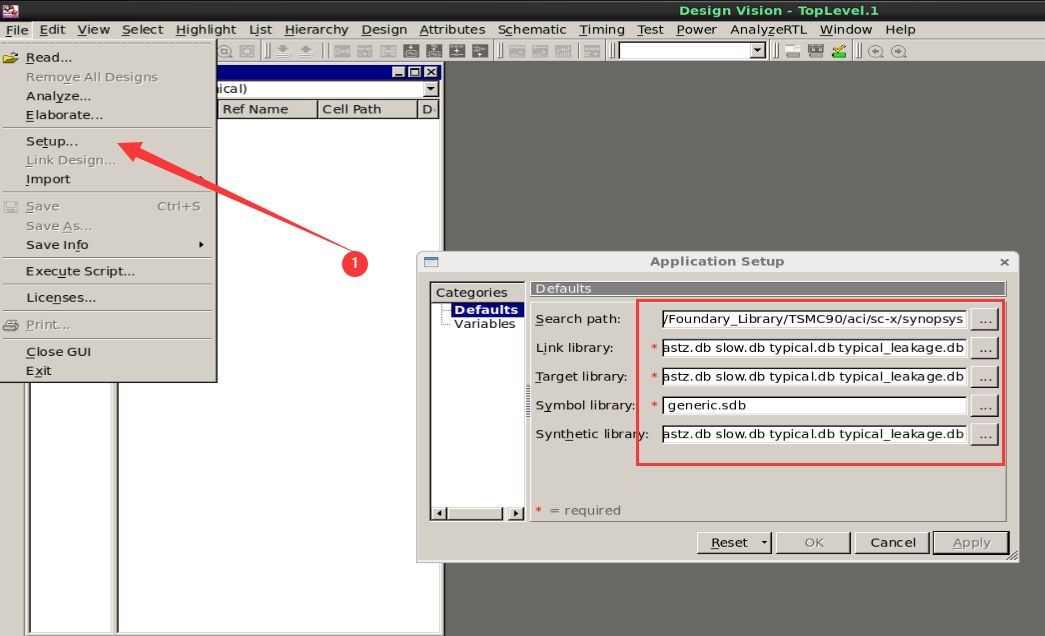

设置工作环境

输入design_vision打开DC界面后,可以对软件的相关环境进行配置,这里点击file下拉菜单中的setup,即在界面中可以对search_path和library setup进行相关设置,这里可以找到自己已有的工艺库的路径和文件进行添加链接。

相比之前介绍的library,这里多了Symbol library和Synthetic library,下面对这两个library进行简要介绍。

Symbol library 提供 Design Vision GUI 中设计实现的图形符号,如果使用脚本模式而不使用 GUI,此库可不指定 Symbol library。

Synthetic library:即为 Designware library ,名字上翻译是综合库,但却常称之为IP库,而不是直译。特殊的 Designware library 是需要授权的(比如使用多级流水线的乘法器),默认的标准 Designware 由 DC 软件商提供,无需指定。

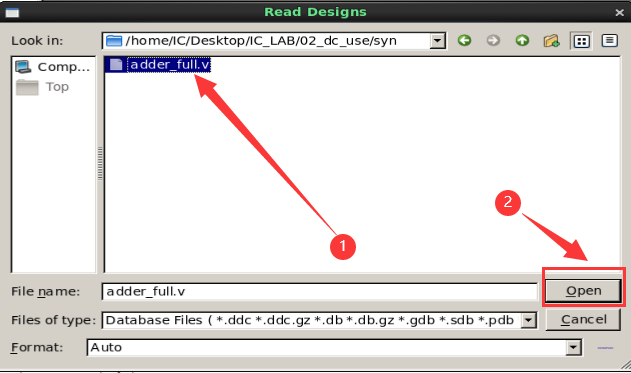

加载设计文件

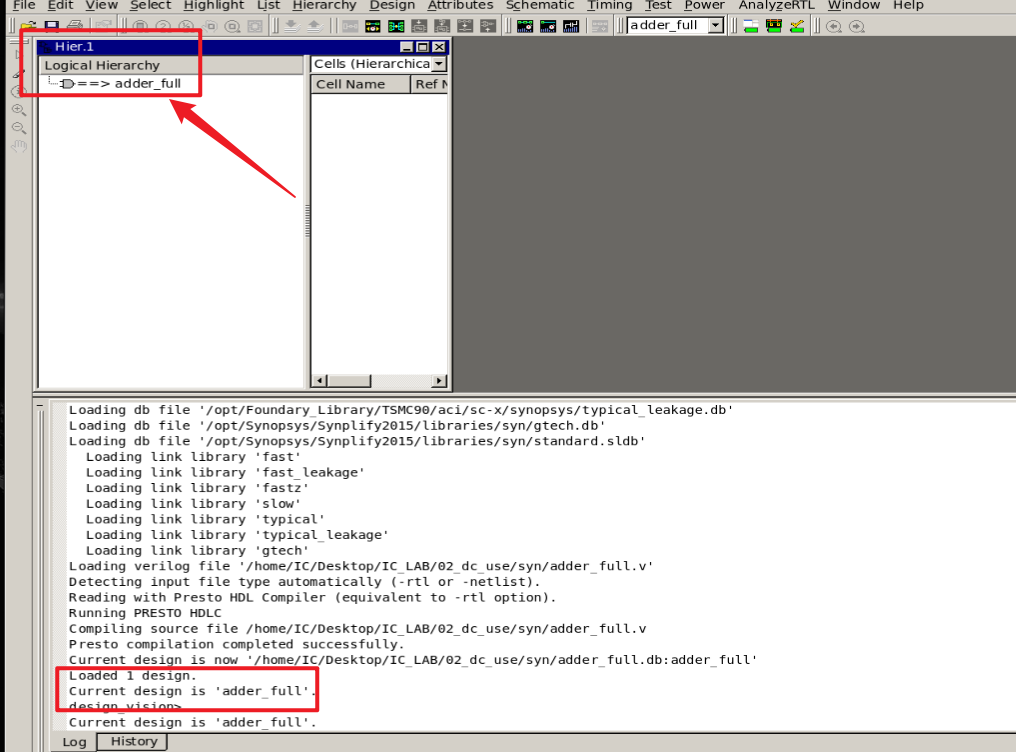

这里点击file下拉菜单中的setup,点击read,选中添加之前的全加器代码进行打开。

添加后可看到这里的结构层级中已经存在了全加器的文件,因为这里只添加了一个文件,所以当前设计的顶层也即为该文件。

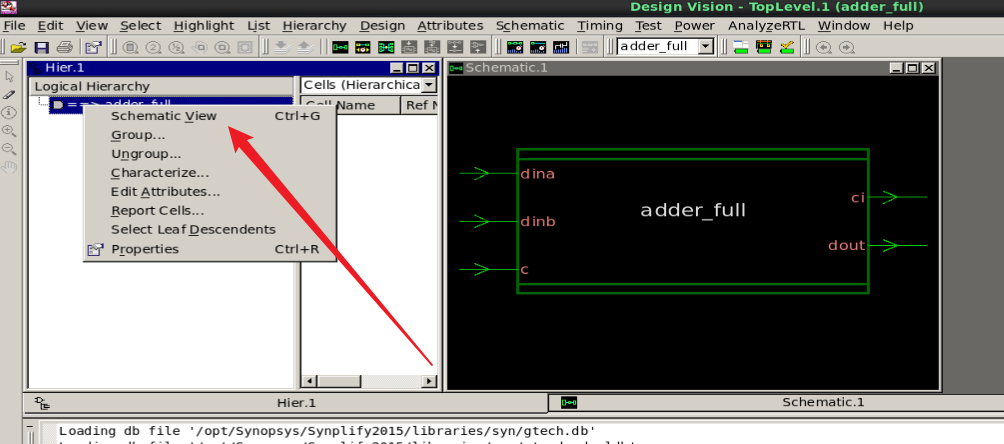

选中全加器文件右键点击schematic view可查看代码对应的原理图,这里对应FPGA开发设计中的RTL view,

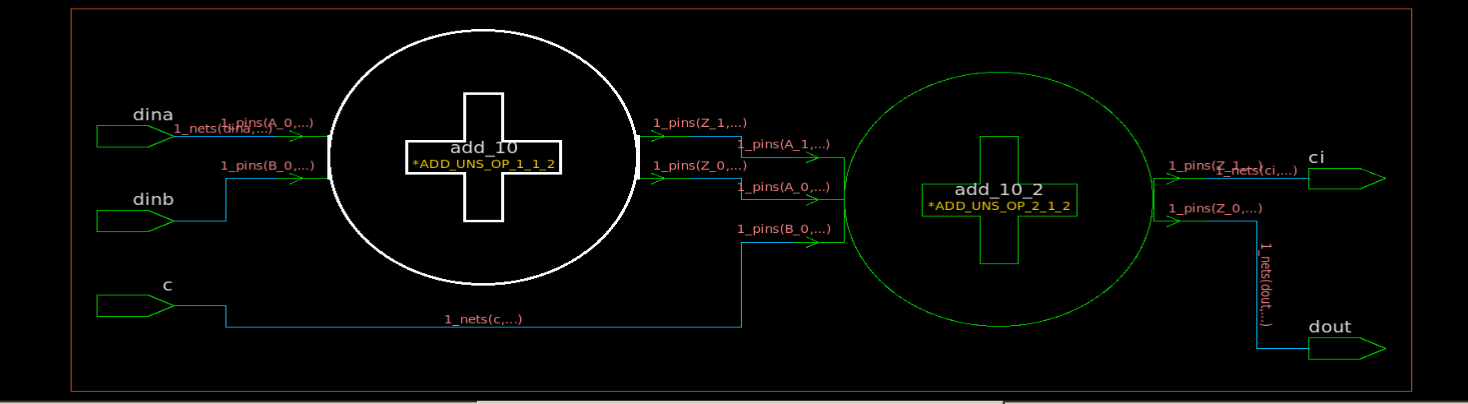

双击后可查看内部的具体的结构,

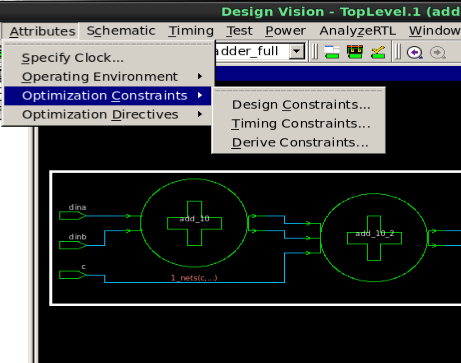

设置约束

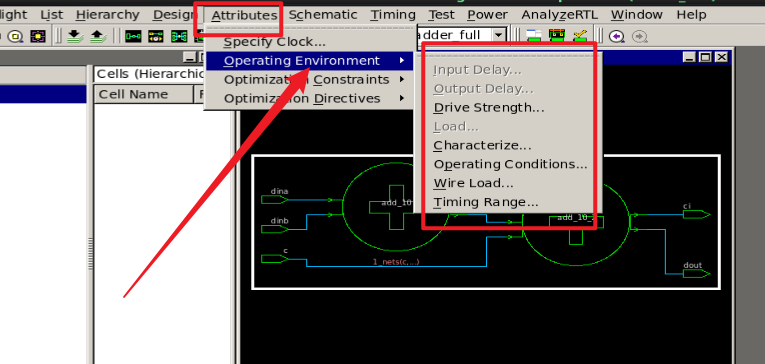

在attribute下拉菜单中有设置约束的相关选项,可以在此设置环境约束以及设计相关的时钟约束等。

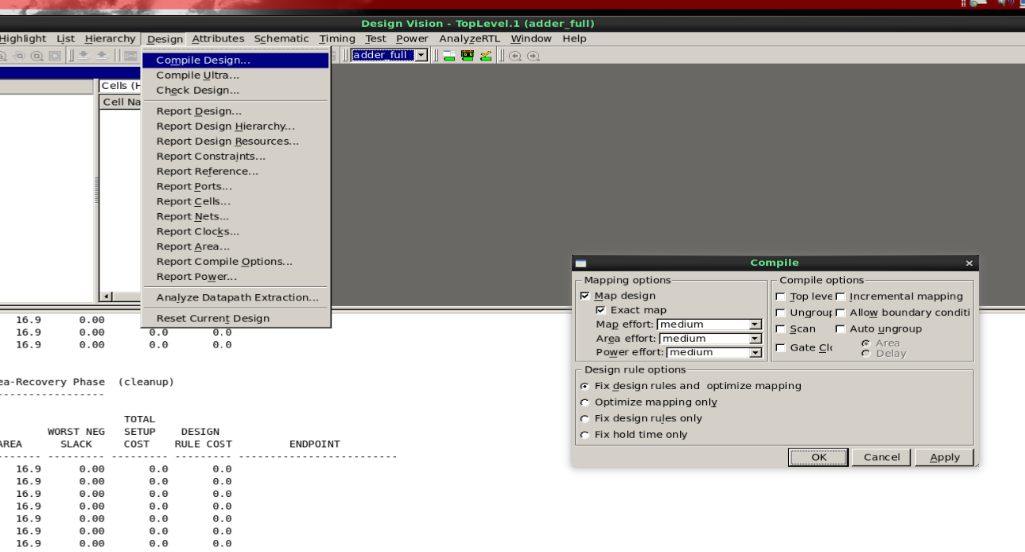

编译以及查看报告

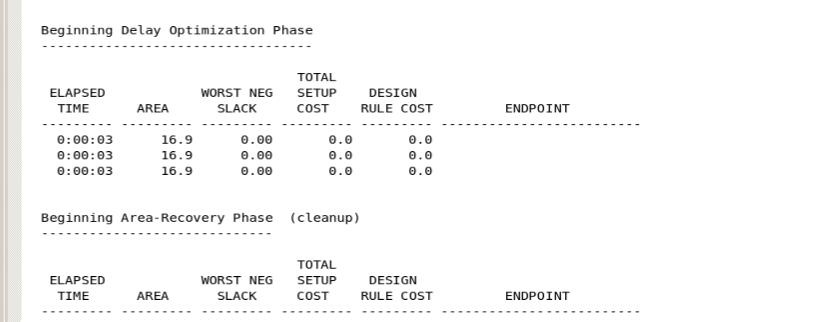

正常工作流程中,设置完相关约束信息后即可启动编译,在design下拉菜单中可以点击compile Design,弹出编译窗口后这里保持默认设置运行编译。同时,design菜单中可以打开相关设计的分析报告进行分析设计的性能。

在log界面中将会打印相关编译信息,这里仅仅是组合逻辑的加法器所以对于编译过程来说并不需要太多既可完成运行。、

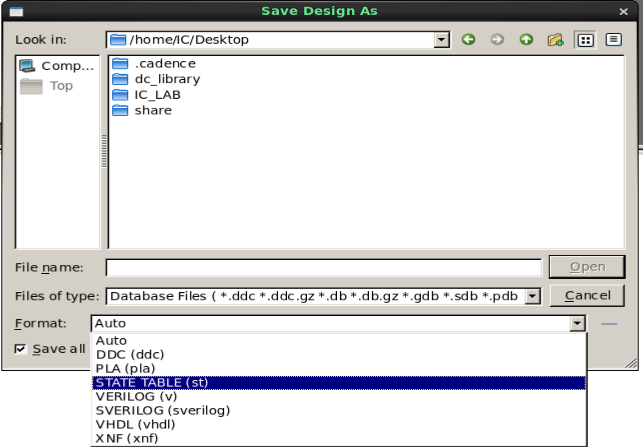

导出设计文件

在界面化的方式下使用DC可以在File下拉菜单中,选择save as 保存设计的相关文件。

至此,界面操作的方式使用DC的大致流程讲解完毕。

reference

- link library 、target library、symbol library、synthetic library对照分析