一、概述

封装的作用

1.3 封装类型

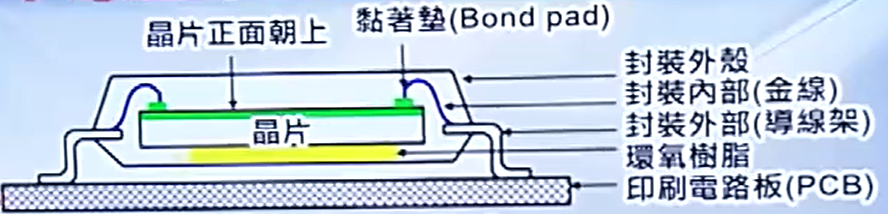

1.3.1 打线封装(Wire Bonding)

打线封装是传统的封装方式,具体过程是将晶圆切割为晶粒(Die)后,使晶粒贴合到相应的基板架的小岛(LeadframePad)上,再利用导线将晶片的接合焊盘(Bond pad)与基板的引脚相连(WireBond),实现电气连接,最后用外壳加以保护(Mold,或Encapsulation)。典型封装方式有DIP、SOP、TSOP、QFP等。

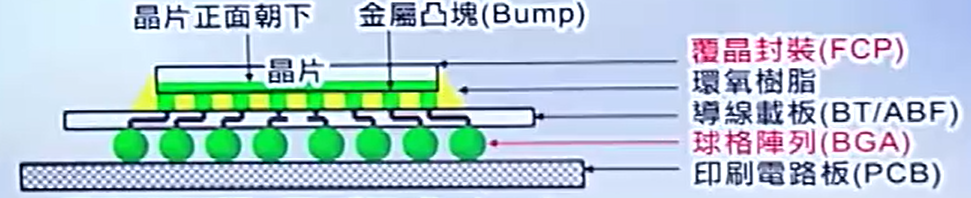

1.3.2 覆晶封装(Flip chip packege)

根据封装的层次又大致可分为标准封装和先进封装。标准封装包括2D封装等,先进封装包括2.5D封装、3D封装等。

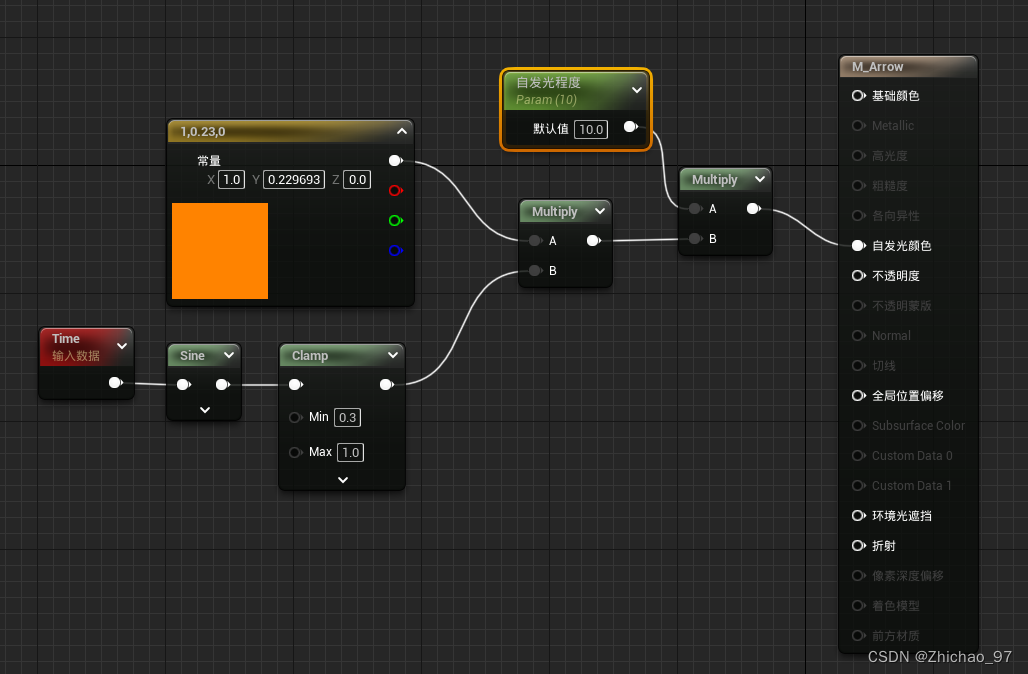

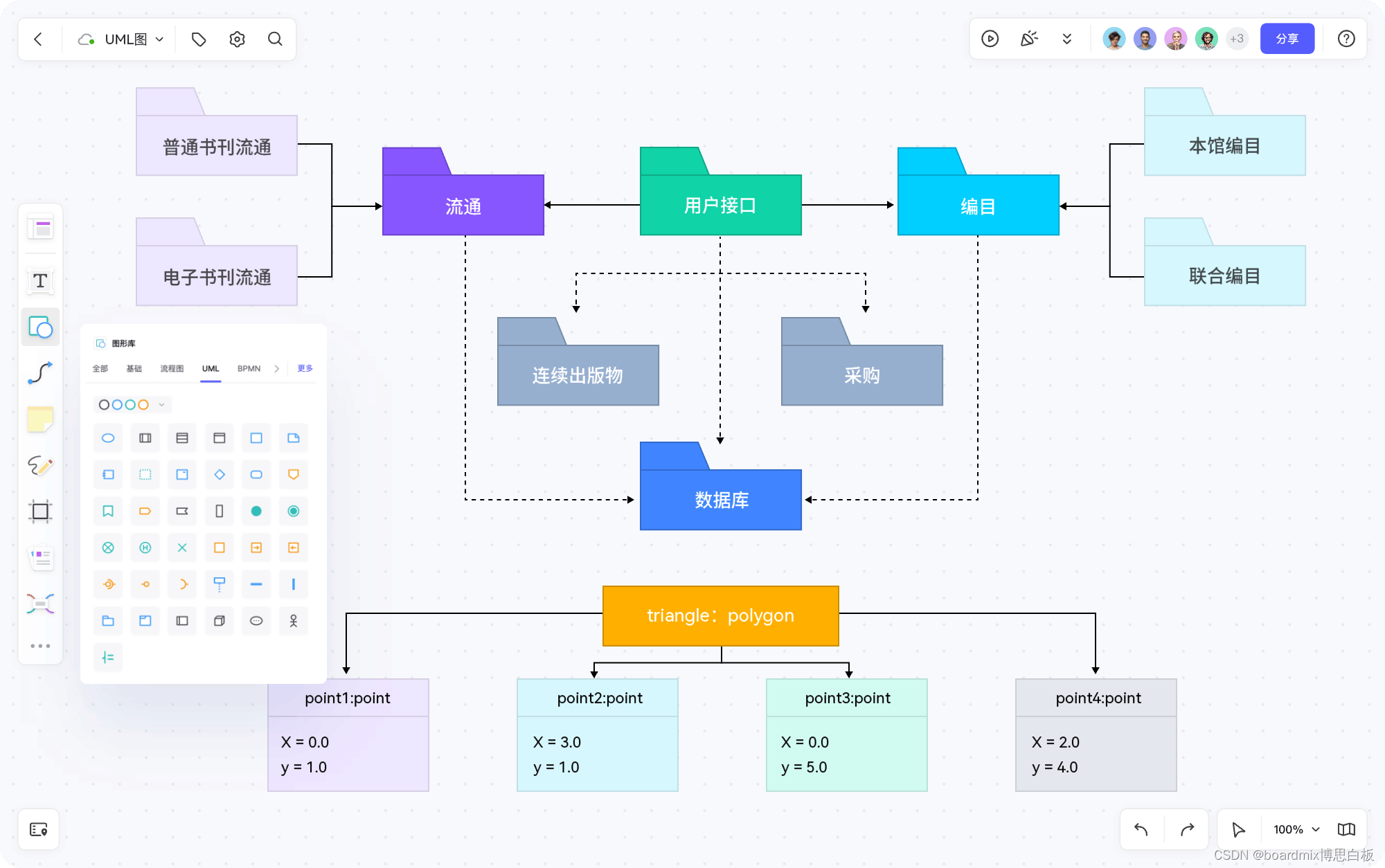

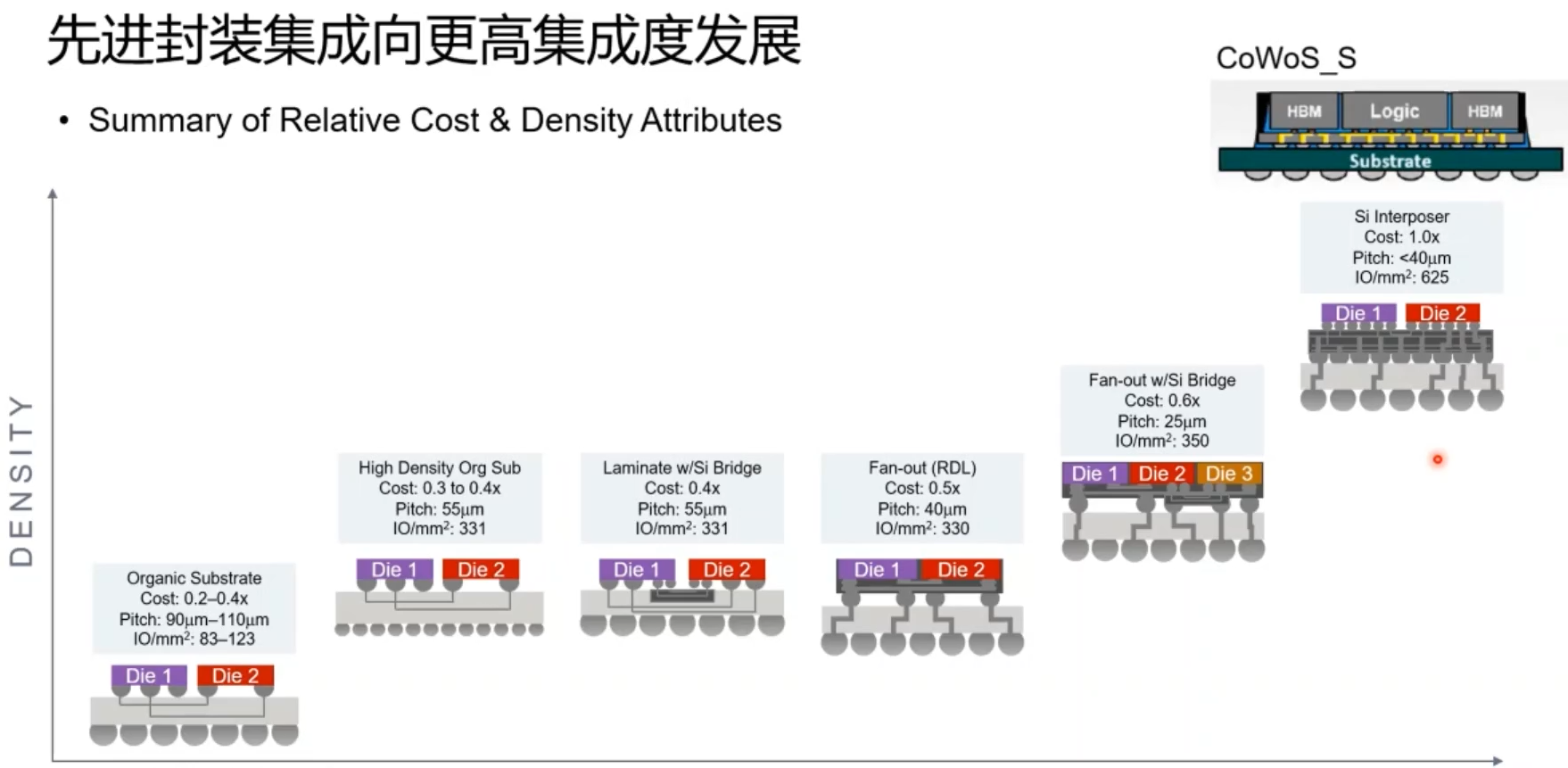

覆晶封装根据封装密度又可分为如下封装形式,如图所示为封装密度和成本关系示意图:

- Laminate w/Si Bridge

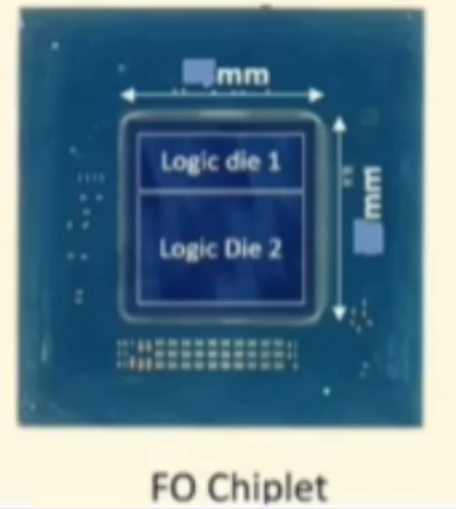

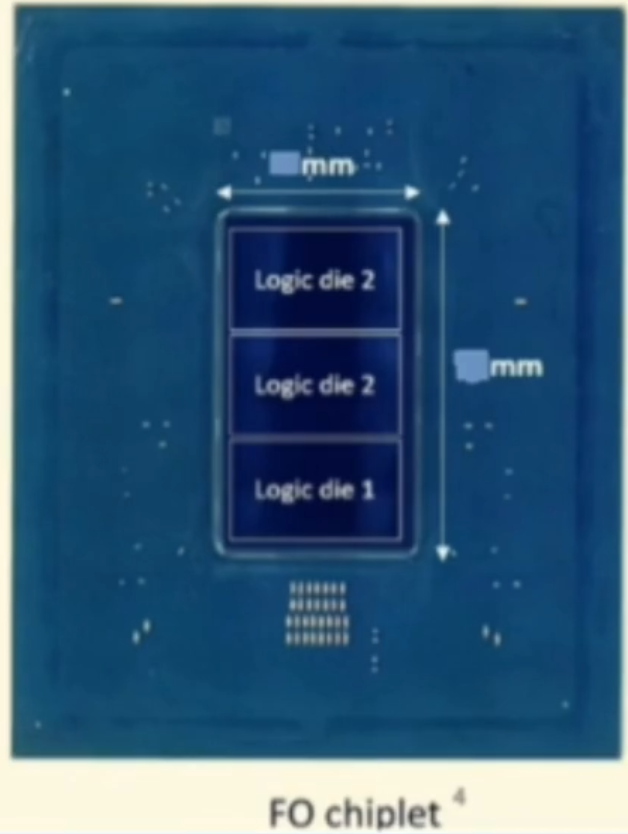

嵌入式桥接技术(EMIB),由Intel提出并积极应用 - Fan-out(RDL)

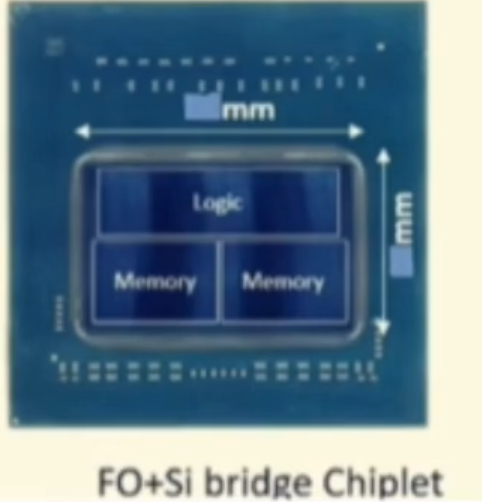

通过RDL层来实现信号的传输,典型工艺为台积电InFo工艺,应用于智能手机 - Fan-out w/Si Bridge

硅中阶层传输信号,RDL层传输电源和地,典型工艺为台积电CoWoS_L工艺 - Si interposer

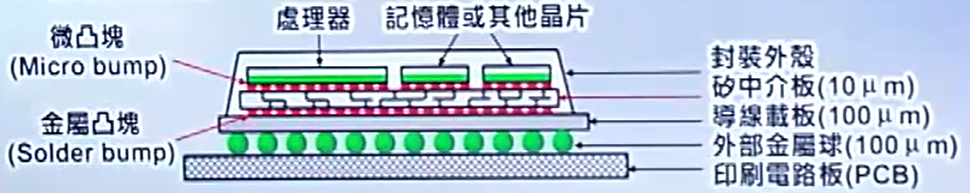

2.5D封装技术,在基板和die之间放置了额外的硅中介层,die之间的通信通过硅中介层中的连线进行。典型工艺为台积电CoWoS_S工艺,针对于高性能计算市场,主要集成logic层和HBM颗粒。

二、2 D封装

比较成熟的制造工艺,各家工艺厂商的定义基本类似

三、2.5D 封装

相比较早的2D芯片设计验证,2.5D芯片封装设计需要新的设计验证方法学。2.5D封装技术更加各家工艺厂商定义不同有不同的实现方式。

- 2.5D 封装的挑战

- die间信号/电源完整性分析

- 跨die的静态时序分析

- 高速通路的跨芯片跨尺寸的die间联合仿真

CoWoS

增加了硅/矽中介层(interposer),用于承载CPU、IO、GPU 等芯粒,并进行芯粒间的导线连接。

四、3D封装

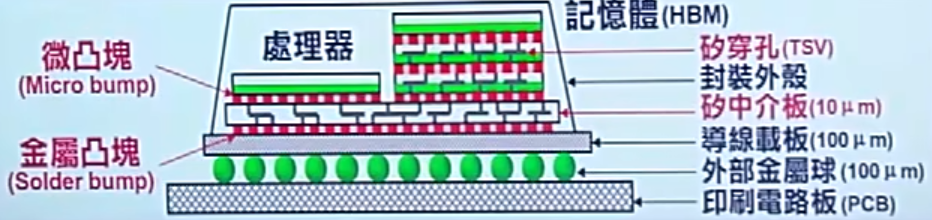

TSV(Through-siliconvia,硅通孔)

3D堆叠技术(WoW:wafer on wafer)

与2.5D封装不同的是,3D封装时通过硅穿孔将芯粒堆叠起来,上下芯粒间通过硅穿孔中的导线连接。

由于考虑到芯片的散热,该封装技术通常用于DDR芯粒的堆叠。

根据台积电2020年技术数据,芯粒堆叠最多可叠致8片。

3D封装的优势

- 相比2D封装,减少的Die连接线长和die占地面积,进而导致耕地的连接延迟和功耗

- 由于TSV的存在,获得更高的互连密度,缓解了2D封装下IO pin数量的限制

- 较小的footprint也使得芯片良率更高ao