萌新的FPGA学习之分频器的介绍

分频器的介绍

分频就是生成一个新时钟,该新时钟的频率是原有时钟频率的整数分之一倍,新周期是原有周期的整数倍。再简单来说,让你手撕一个四分频电路,就是写代码生成一个周期是原来四倍的时钟,如果手撕一个三分频电路,就是写代码生成一个周期是原来三倍的时钟。但是奇数分频会比偶数分频复杂一些。

实现分频一般有两种方法,一种方法是直接使用 PLL 进行分频,比如在 FPGA 或者 ASIC 设计中,都

可以直接使用 PLL 进行分频。但是这种分频有时候受限于 PLL 本身的特性,比如输入 100Mhz 时钟,很多

PLL 都实现不了 1Mhz 的时钟分频,这个就是 PLL 本身特性限制的。另外一种方法是直接使用代码来实现

分频,本节就是带领大家使用 Verilog 代码进行分频器电路的设计。

根据分频器的分频比例(分频前的频率和分频后的频率比值)是偶数还是奇数,将分频器分为偶数分

频器和奇数分频器。接下来,我们先看下偶数分频设计。

偶数分频,顾名思义就是分频前的频率和分频后的频率比值是偶数,比如一个 50Mhz 的晶振时钟,进

行二分频后,就是 50Mhz/2=25Mhz。

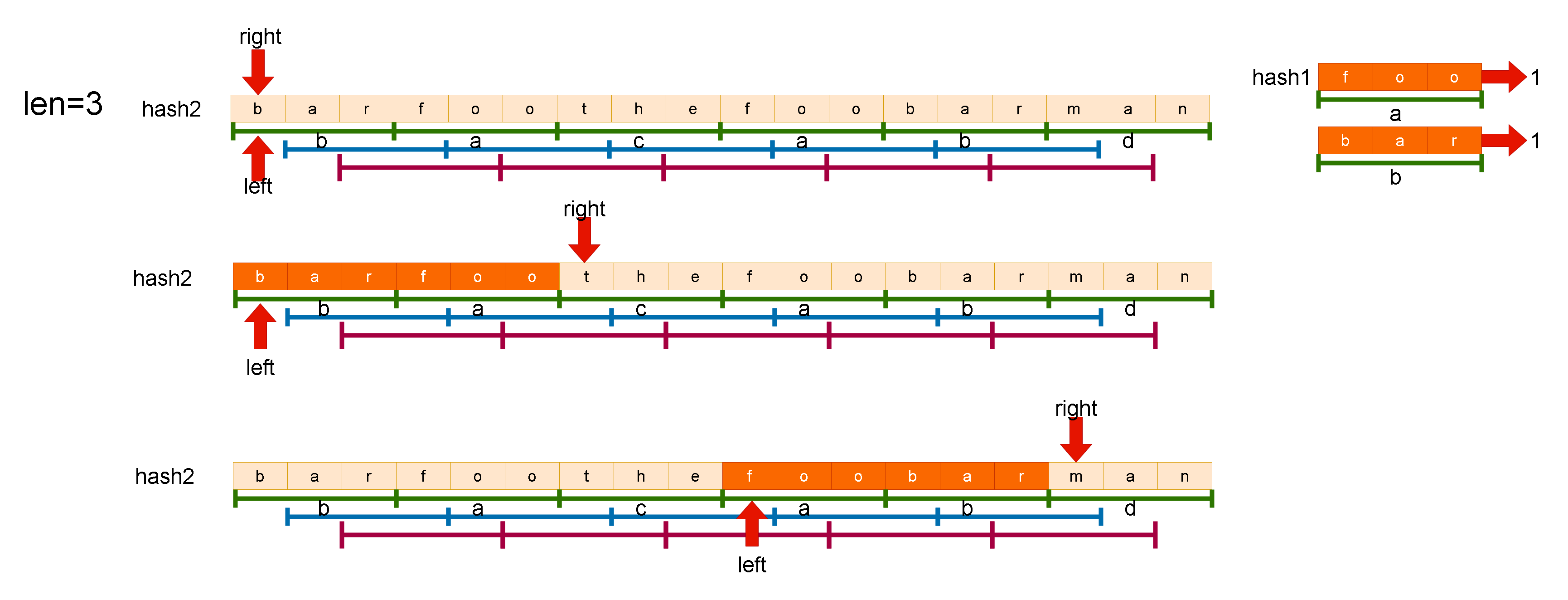

下面我们先来看一下偶数分频实现原理,假设为 N(偶数)分频,只需计数到 N/2-1,然后时钟翻

转、计数器清零,如此循环就可以得到 N(偶)分频。举个例子,比如晶振时钟是 100Mhz 时钟,想得到

一个 25Mhz 的时钟,那么这个是一个 100/25=4 的四分频设计,按照我们刚说的计数到 4/2-1=1,然后时钟

翻转、计数器清零,就可以得到一个 25Mhz 的时钟。根据偶数分频的原理,可以绘制出偶数分频的波形

图:

下面我们再来看下奇数分频,奇数分频顾名思义就是分配前的频率和分频后的频率比值是奇数。比如一个 50Mhz 的晶振时钟,进行三分频后,就是 50Mhz/3=16.667Mhz。实现偶数分频可通过一个简单计数器实现,而如果需要进行三分频、五分频以及七分频等奇数分频而言,一个寄存器肯定时不够的,接下来我们再来看一下奇数分频的原理。同样假设我们需要分频的倍数为 N(奇数)分频,就需要定义一个个数为 N 的 cnt。当 cnt=0 时out_clk1 在 sys_clk 的上升沿拉低,当 cnt 计数到 N/2-1 时 out_clk1 在 sys_clk 的上升沿进行翻转;而out_clk2 则在 cnt=0 时的 sys_clk 下降沿进行拉低,当 cnt 计数到 N/2-1 时,out_clk2 在 sys_clk 下降沿进行翻转。最后将 out_clk1 和 out_clk2 的波形相与,就得到了我们分频后输出的 out_clk。这样我们只需要通过修改 N 的值和计数器的位宽就可以实现其他奇数分频,根据这一原理同样可以绘制出奇数分频器的波形图:

这个是5分频 除一下 每个各占原来的2.5

我们交错一下 取上升沿 下降沿 就能完成如此实验

偶数分频 相对于 奇数分频较为简单

下面先介绍 4分频

module divider_4(

input sys_clk ,

input sys_rst_n ,

output reg out_clk

);

reg [1:0] cnt;

always@(posedge sys_clk or negedge sys_rst_n) begin

if(!sys_rst_n)

cnt <= 2'd0;

else if(cnt == 2'd1)

cnt <= 2'd0;

else

cnt <= cnt + 2'd1;

end

always@(posedge sys_clk or negedge sys_rst_n) begin

if(!sys_rst_n)

out_clk <= 1'b0;

else if(cnt == 2'd1)

out_clk <= ~out_clk;

end

下面编写 tb文件

`timescale 1ns / 1ns

module tb_divider_4();

reg sys_clk ;

reg sys_rst_n ;

wire out_clk ;

initial begin

sys_clk = 1'b1;

sys_rst_n <= 1'b0;

#201

sys_rst_n <= 1'b1;

end

always #10 sys_clk <= ~sys_clk;

divider_4 divider_4_inst(

.sys_clk (sys_clk ),

.sys_rst_n (sys_rst_n ),

.out_clk (out_clk )

);

endmodule

我觉得计数应该技术到 (n-1)/2 -1

但是他们写的都是 N/2-1

算了照着写吧

我知道了 奇数除2会向下取整

下面介绍 七分频

module divider_7(

input sys_clk , //系统时钟

input sys_rst_n , //系统复位

output out_clk //输出时钟

);

parameter N = 7; //分频系数

parameter EDGE = N/2-1; //取沿数

reg [2:0] cnt ; //3 位计数器

reg out_clk1;

reg out_clk2;

//计数器模块

always@(posedge sys_clk or negedge sys_rst_n) begin

if(!sys_rst_n)

cnt <= 3'd0;

else if(cnt == N - 1'b1)

cnt <= 3'd0;

else

cnt <= cnt + 'd1;

end

//out_clk1 在上升沿进行翻转

always@(posedge sys_clk or negedge sys_rst_n) begin

if(!sys_rst_n)

out_clk1 <= 1'b0;

else if(cnt <= EDGE)

out_clk1 <= 1'b0;

else

out_clk1 <= 1'b1;

end

//out_clk2 在下降沿进行翻转

always@(negedge sys_clk or negedge sys_rst_n) begin

if(!sys_rst_n)

out_clk2 <= 1'b0;

else if(cnt <= EDGE)

out_clk2 <= 1'b0;

else

out_clk2 <= 1'b1;

end

assign out_clk = out_clk1 & out_clk2;

endmodule

![[AUTOSAR][诊断管理][$11] 复位服务](https://img-blog.csdnimg.cn/eed7d9bbfd96429d83b557a40378c172.png)