(六)锁相环(PLL)

- 1.模拟锁相环

- 2.数字锁相环

- 3.PLL隔离技术

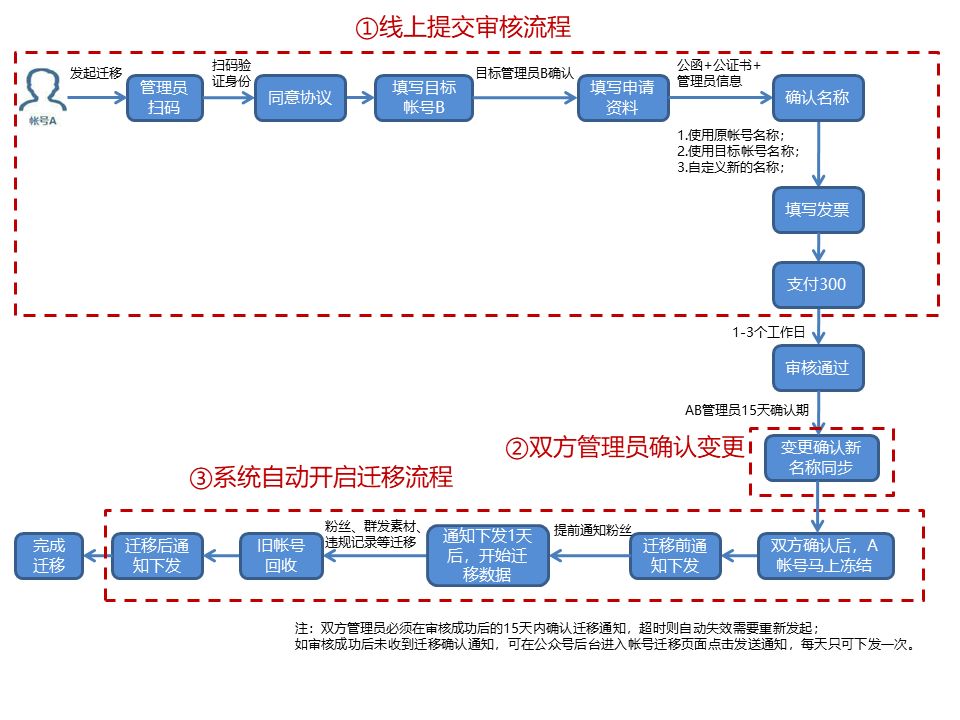

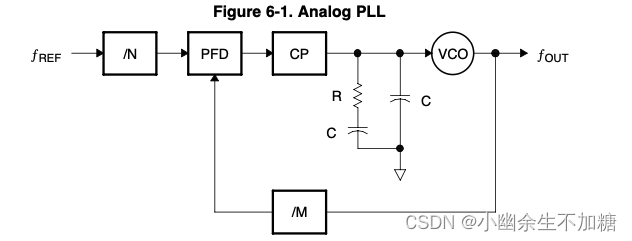

系统设计人员需要隔离PLL,使其免受内部和外部噪声的影响。PLL通常用作频率合成器,将输入时钟乘以一个整数。该整数是反馈计数器M除以输入计数器N的比值,如所示Figure 6-1。

两种主要的PLL架构是模拟PLL (APLL)和数字PLL (DPLL)。了解这些差异有助于进行设计权衡,从而最大限度地降低电源和其它高噪声开关器件等外部电路引起的噪声和抖动。

1.模拟锁相环

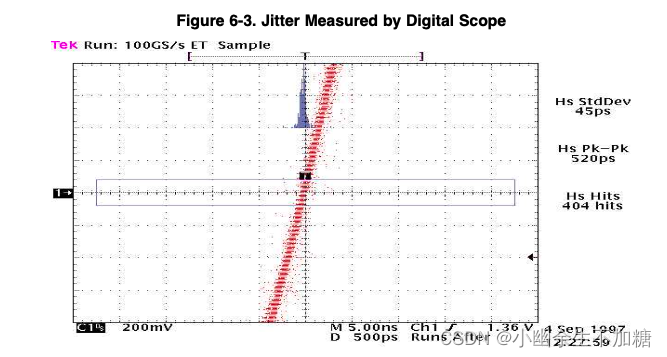

下表提供了所示每个模块的简要描述Figure 6-1 对于APLL来说。

下文概述了PLL如何用作频率合成器。

1.参考时钟连接到PFD输入。N分频计数器会降低输入频率。

2.PFD将M分频计数器的输出与参考时钟进行比较,并产生一个误差信号。

3.根据误差信号,CP对环路滤波器(图52所示的RC滤波器)上存储的电流进行充电或放电。这会提高或降低VCO控制电压。对于某些PLL架构,提高VCO控制电压会提高时钟频率,降低电压会降低时钟输出频率。

4.相位校正继续进行,直到来自M分频计数器的反馈信号和参考时钟同步。此时,误差电压应该为零。

5.输出时钟频率等于M分频计数器和N分频计数器的比值乘以输入时钟频率。根据经验,较高的乘数比会产生较高的抖动,因此在使用PLL进行设计时,M与N之比应尽可能低。对于给定输入频率fin,PLL输出频率fout为:

其中M是PLL反馈计数器,N是输入计数器。

PLL抖动

模拟锁相环PLL设计中的抖动定义为信号时序相对于参考时钟的偏移。DSP PLL抖动的三个主要来源是参考时钟本身产生的抖动、电源噪声以及来自外部和内部电路的噪声耦合。下面列出了设计人员将DSP PLL抖动降至最低的重要技巧。

1.选择抖动规格尽可能低的参考时钟振荡器。

2.对时钟电路进行大量滤波,以降低噪声对输出抖动的影响。

3.在参考时钟的输出端使用一个串联端接电阻来控制边沿速率。

4.如果可能,差分分配时钟。差分信号抑制共模噪声和串扰。

5.将乘法器设置得尽可能低,以实现最大DSP工作频率。请记住,较高的乘法比会产生较高的输出抖动。

在所有情况下,抖动都可以最小化,但无法消除。对频率合成器和DSP性能非常重要的三种确定性抖动是长期抖动、逐周期抖动和周期抖动。

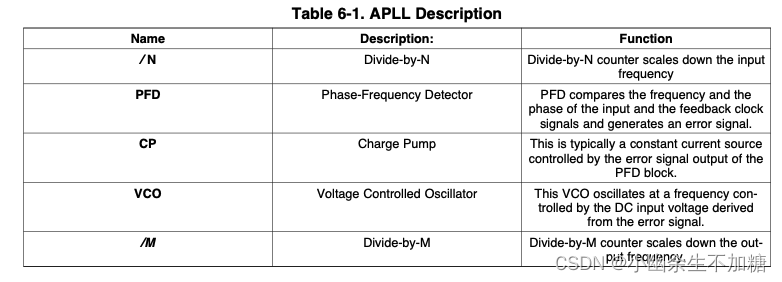

长期抖动:

看见Figure 6-2 其中,长期抖动定义为经过大量转换后与理想参考时钟输入的时间偏移。长期抖动测量第一个上升沿之后大量周期(N)内上升沿的偏差。

峰峰值抖动=最大周期(N个周期)–最小周期(N个周期)

长期抖动测量:

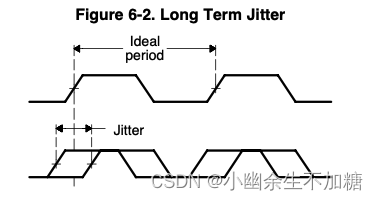

1.使用高速10GHz采样示波器,例如Agilent 54855A。

2.使用输入时钟触发示波器,并将示波器设置为无限持续模式。

3.偏差是从第一个上升沿到第n个周期测量的。中范围上显示的“模糊”Figure 6-3 是长期抖动。

周期间抖动:

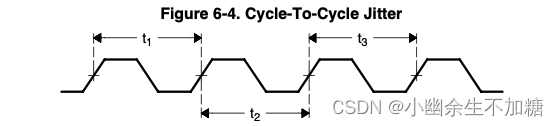

看见Figure 6-4 其中周期到周期定义为两个连续时钟周期之间的时钟周期偏差。

在这里Figure 6-4,则通过从t1中减去t2,从t2中减去t3,以此类推。

周期间抖动测量:

这是一个很难用高速采样范围精确测量的参数。最好的方法是使用定时间隔分析器(TIA),它一次捕获一个周期,并比较两个连续周期之间的定时差异。

另一种方法是使用带有周期到周期抖动测量选项的示波器。该方法概述如下。

1.使用具有周期间抖动选项的高速10GHz采样示波器,例如Agilent 54855A。

2.触发PLL输出时钟并测量周期间抖动。使用开窗法测量从一个周期到另一个周期的变化。

周期抖动:

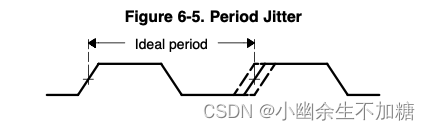

看见Figure 6-5 其中,周期抖动定义为时钟跃迁与其理想位置的最大偏差。这些时期是不连续的。

周期抖动测量:

使用高速10GHz采样示波器,例如Agilent 54855A。

数字锁相环将示波器设置为无限持续模式,并在上升沿触发PLL时钟输出。

在下一次时钟上升时测量屏幕上显示的“模糊度”。

总之,抖动测量可以使用高速数字采样示波器、时序间隔分析仪(TIA)或波峰抖动测量系统来完成。

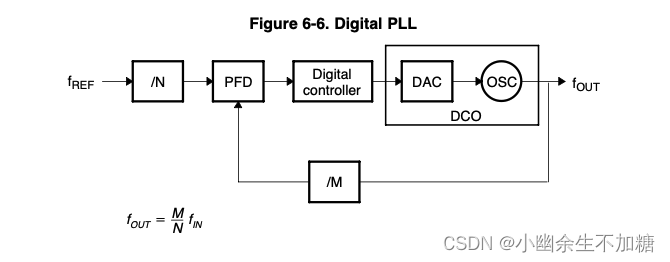

2.数字锁相环

数字锁相环

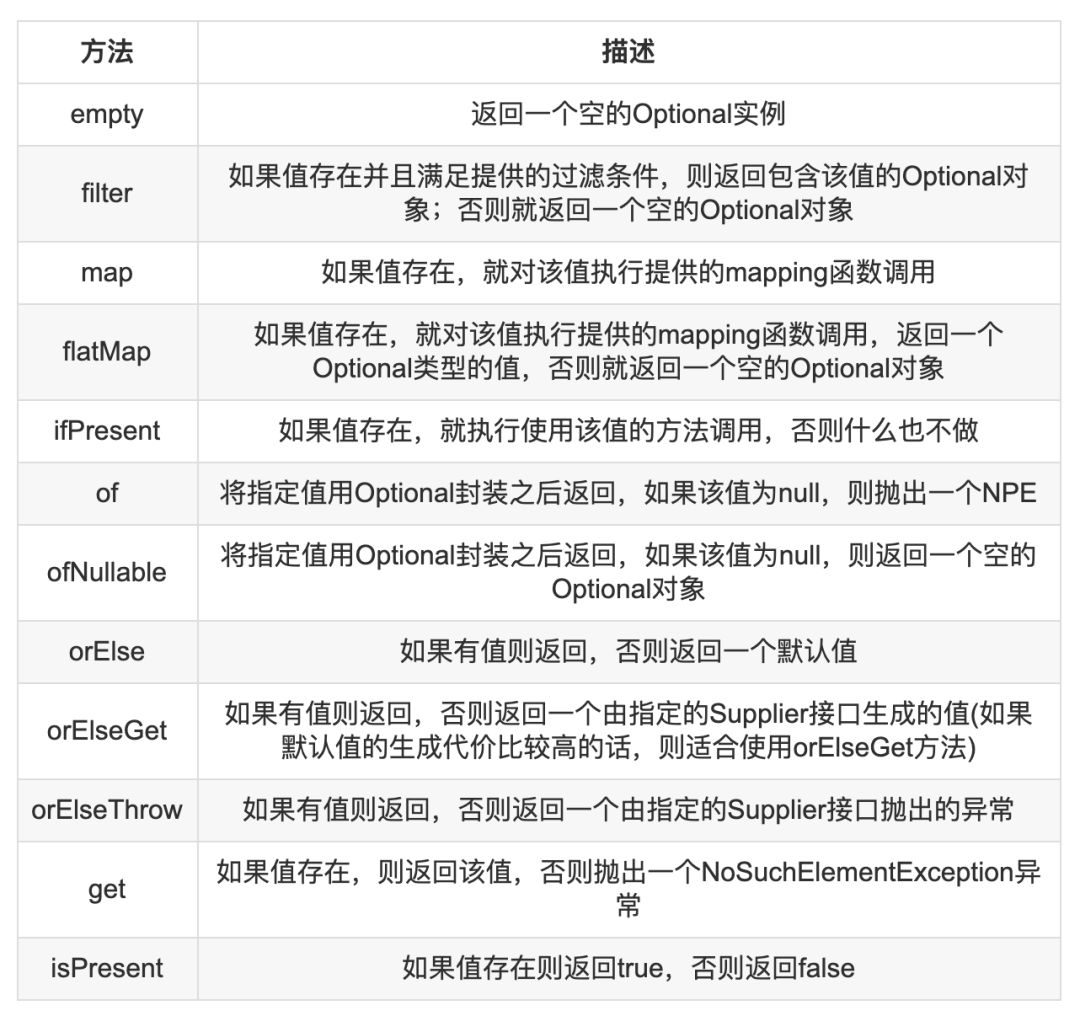

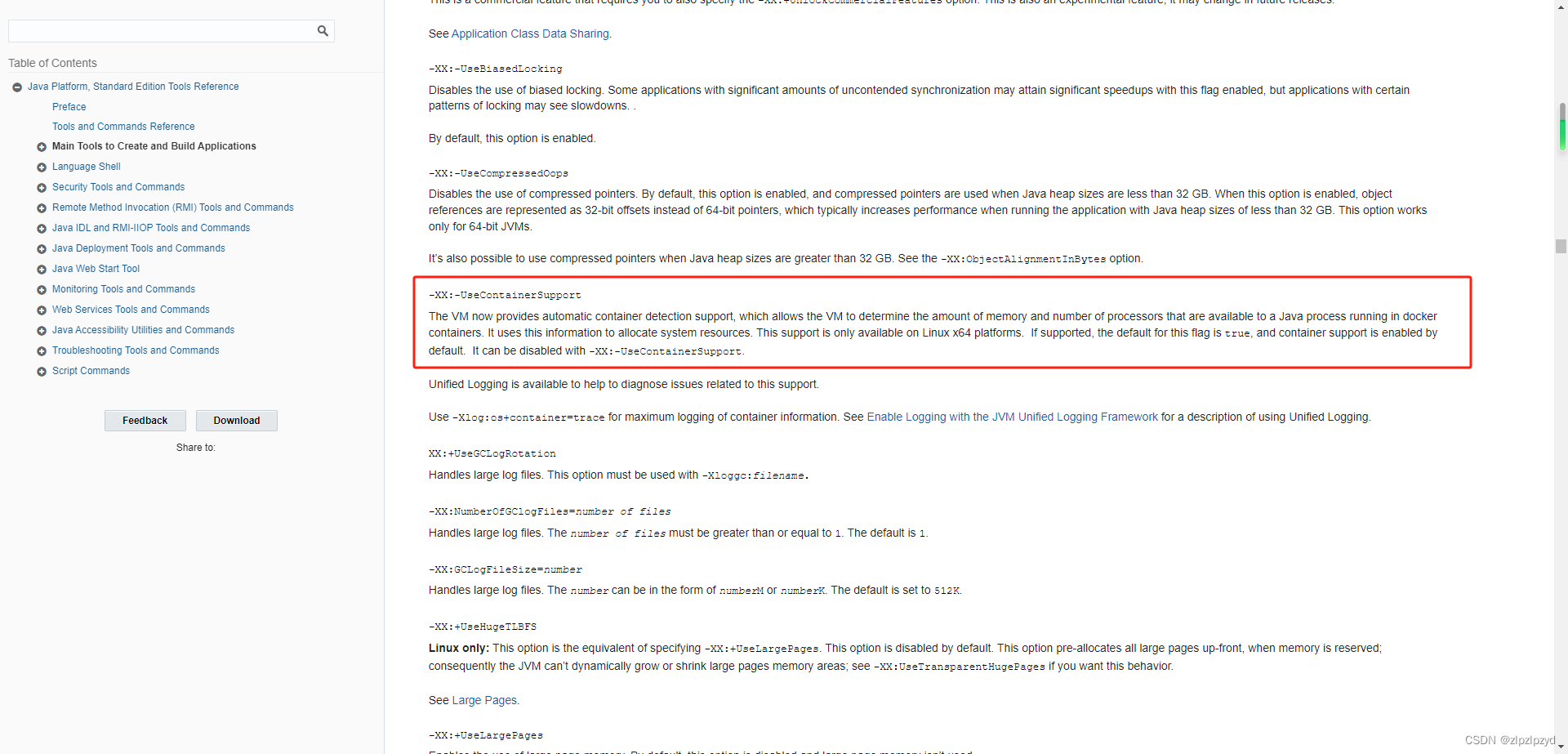

APLL和DPLL的主要区别在于,DPLL用数字控制器模块取代模拟滤波器,在数字域中过滤相位误差,并用数字控制器振荡器取代VCO(DCO)。DPLL的优点是:

1.DPLL支持30KHz到65MHz的宽范围输入频率。

2.与APLL相比,DPLL模块需要更小的硅面积来实现,并且消耗更少的功率。

3.DPLL没有模拟滤波器组件,如电容器,这可能会导致泄漏电流。

4.DPLL块是可扩展和可移植的。相同的设计可以在不同的工艺技术节点上实现。

5.DPLL设计可以针对低抖动进行优化。但对于USB、音频和视频时钟等对抖动敏感的设计来说,这可能是不可接受的。

DPLL的缺点是:

1.它对外部和内部电源噪声非常敏感。建议使用线性调节器将电源与DPLL隔离。

2.低电源抑制比。

3.除电源灵敏度外,量化噪声和鉴相器死区也是输出抖动的主要来源。

4.需要DAC模块来控制振荡器。这使得DPLL对噪音更加敏感。

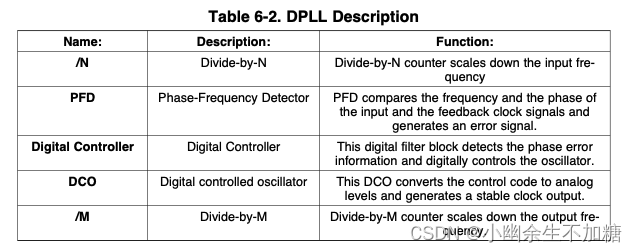

Figure 6-6 展示了典型的DPLL建筑Table 6-2 描述体系结构中每个模块的功能。

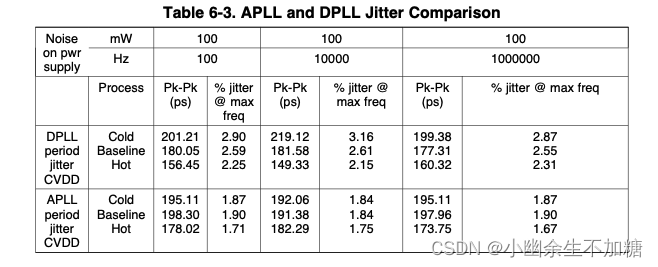

APLL和DPLL抖动表征:

Table 6-3 显示了模拟PLL和数字PLL之间的抖动比较,显示了过程变化的影响,其中热为快,冷为慢,基线为典型。在这种DSP设计中,DPLL电源由内部低压差调节器(LDO)隔离,而APLL直接连接到公共电源层。为了测试噪声灵敏度,将100mV从100Hz到1MHz的噪声调制注入电源轨。结果表明,峰峰值周期抖动对于DPLL小于3%,对于APLL小于2%。采用LDO时,电源噪声最高可达50mV,DPLL抖动小于4%。

设计人员在电源上注入信号进行抖动测量时需要小心。用于模拟高噪声电源条件的信号性质会对PLL抖动产生重大影响。频率低于PLL带宽的方波信号是PLL抖动的最差情况。就噪声幅度而言,峰峰值电压必须在电源限值范围内。例如,对于1.6V +/-3%内核,最大可接受的峰峰值噪声为96mV(-48mV最小值和+48mV最大值)。

3.PLL隔离技术

如前所述,APLL和DPLL都对噪声敏感,尤其是PLL带宽内的噪声频率。为了防止高频PLL信号传播出PLL部分并影响其它电路,需要PLL隔离。PLL隔离还可以衰减传播到PLL电路的外部噪声,这种噪声会导致过度抖动。许多情况下,外部电源噪声会导致PLL不稳定,DSP随机锁定。

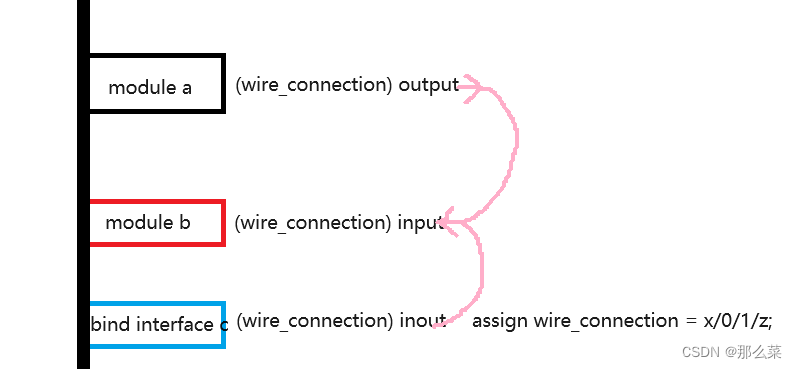

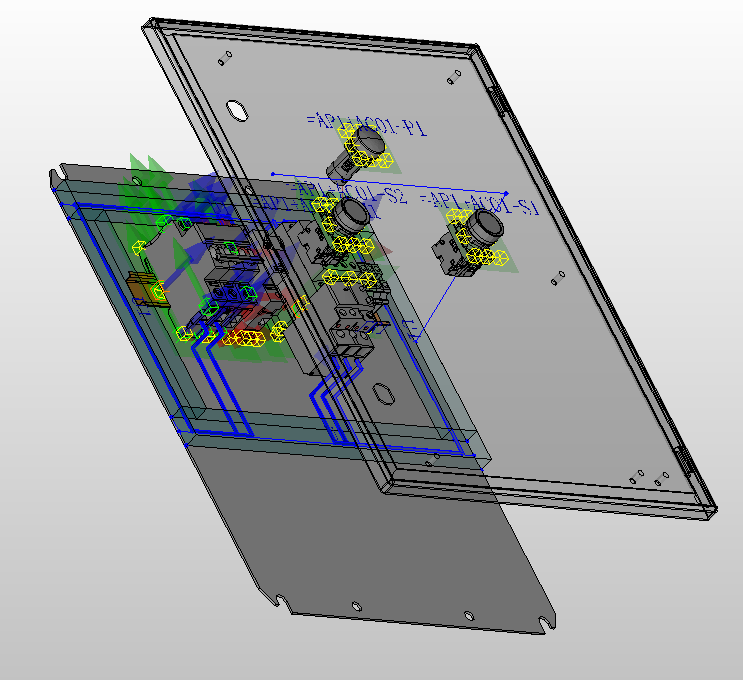

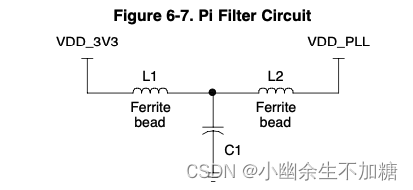

后面讨论的隔离PLL的两种重要滤波器方案是低频滤波和高频滤波。对于高频滤波,可以使用Pi或T网络滤波器,如所示Figure 6-7:

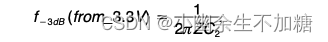

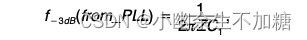

Pi滤波器电路由一个铁氧体磁珠L和两个电容C1和C2组成。该电路提供输入和输出隔离,来自3.3V电源的噪声由铁氧体磁珠和C2电容衰减,PLL电路产生的噪声由铁氧体磁珠和C1电容隔离。由Pi滤波器形成的低通滤波器的转折频率计算如下。

其中Z是噪声频率下铁氧体磁珠的电阻。

其中Z是噪声频率下铁氧体磁珠的电阻。

选择尽可能大的电容值来过滤低频噪声,并将Pi滤波器元件尽可能靠近PLL电源引脚放置。此外,选择具有最小DC导通电阻但在30MHz时具有大电阻的铁氧体磁珠。

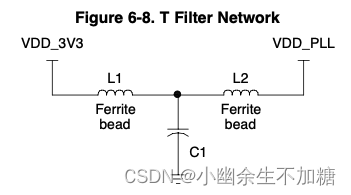

测试滤波器由两个铁氧体磁珠和一个电容组成,如所示Figure 6-8。就像Pi滤波器一样,3.3V电源噪声由L1铁氧体磁珠和C1电容衰减,PLL噪声由L2铁氧体磁珠和C1电容隔离。方程如下。

其中Z1是铁氧体磁珠L1的电阻。

其中Z2是铁氧体磁珠L2的电阻。

选择尽可能大的电容值来过滤低频噪声,并将Pi滤波器元件尽可能靠近PLL电源引脚放置。此外,选择具有最小DC导通电阻但在30MHz时具有大电阻的铁氧体磁珠。

Pi和T电路都有利于滤除高频噪声。然而,Pi电路具有优势,因为这种拓扑结构可以将电容放置在更靠近PLL电压引脚的位置,从而确保低接地阻抗和最小的电流环路面积,从而降低EMI。

对于低频隔离,有两种常见的技术,带大容量电容的Pi滤波器和线性稳压器。

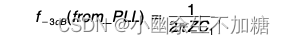

低频滤波的一种方法如所示Figure 6-10 其中电阻R代替铁氧体磁珠,大容量电容C3 (10uF至33uF)添加到电路中。电阻R和大容量电容C3会衰减低频噪声。需要选择电阻,使得电阻上的电压降可以忽略不计。PLL电源电压必须在最差情况下PLL功耗的额定限值范围内。

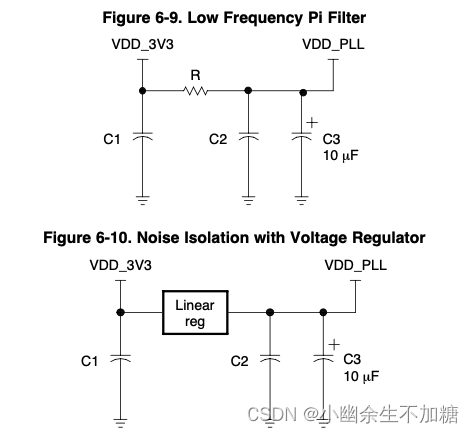

低频滤波的另一种方法是使用线性稳压器。这种方法对PLL性能的影响最小。线性调节器通常具有良好的线路调节和电源抑制特性,可防止低频瞬变和高频噪声进入PLL电路。中所示的方法Figure 6-9 实施起来比前面描述的其它方法更昂贵,但在保持PLL电压尽可能干净以保证最低PLL抖动方面极其有效。