SVA可以在序列每次成功匹配时调用子程序。同一序列中定义的局部变量可以作为参数传给这些子程序。对于序列的每次匹配,子程序调用的执行与它们在序列定义中的顺序相同。

module sub;

logic a, b, clk;

initial $vcdpluson();

initial begin

clk = 1'b0; a=1'b0; b=1'b0;

repeat(2) @(posedge clk);

a=1'b1;

repeat(1) @(posedge clk);

a=1'b0;

repeat(2) @(posedge clk);

b=1'b1;

repeat(1) @(posedge clk);

b=1'b0;

repeat(2) @(posedge clk);

a=1'b1;

repeat(1) @(posedge clk);

a=1'b0;

repeat(6) @(posedge clk);

b=1'b1;

repeat(1) @(posedge clk);

b=1'b0;

repeat(2) @(posedge clk);

$finish;

end

initial forever clk = #25 ~ clk;

sequence s_display1;

@(posedge clk) ($rose(a), $display("Signal a arrived at %t\n", $time));

endsequence

sequence s_display2;

@(posedge clk) ($rose(b), $display("Signal b arrived at %t\n", $time));

endsequence

property p_display_window;

@(posedge clk) s_display1 |-> ##[2:5] s_display2;

endproperty

a_display_window : assert property(p_display_window);

endmodule

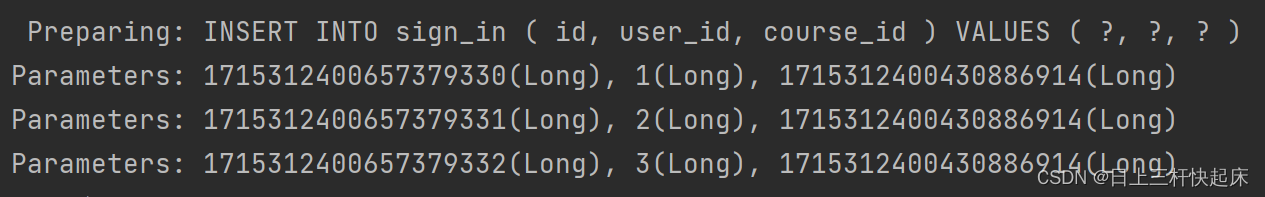

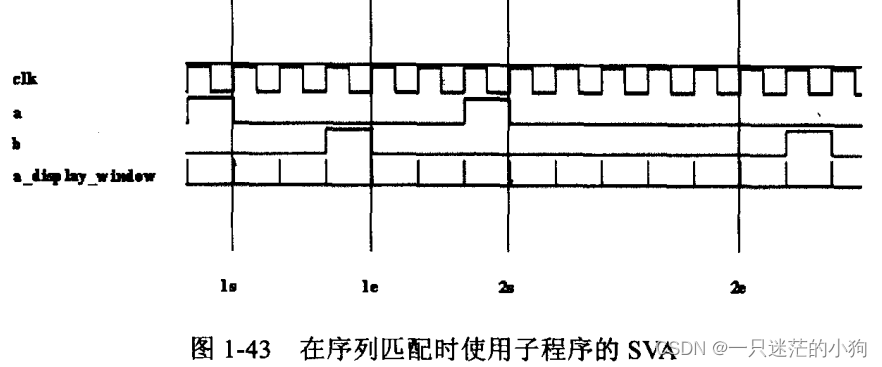

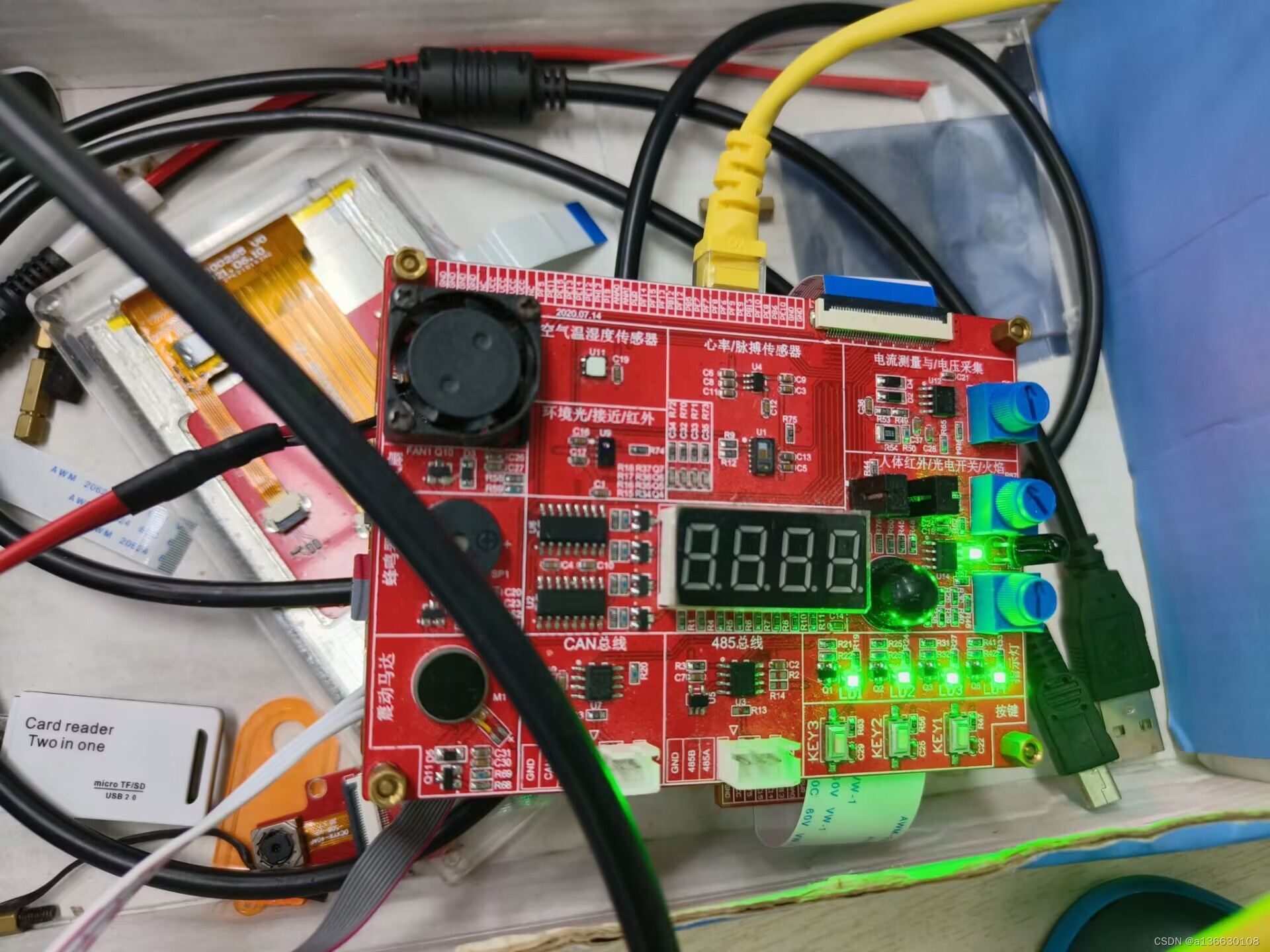

序列 s_display1查找信号“a”的上升沿。如果匹配,就执行display语句。序列 s_display2对信号“b”作类似的检查。属性p_display_window检验如果序列 s_display1出现,那么序列s_display2必须在2~5个时钟周期之间的某个时刻出现。使用display语句,用户可以得到精确的信息,了解后续序列经过多少个时钟周期完成。图1-43显示了检验在模拟中的响应。

标记1s显示了由于检测到信号“a”的上升沿而得到的一个检验器的有效开始。在这一点,SVA执行序列 s_display1的 display语句。标记1e显示了信号“b”出现上升沿的点。因为它出现在3个时钟周期后,所以检验成功。在这个点上,执行序列 s_display2的 display语句。

标记2s显示了由于检测到信号“a”的上升沿而得到的检验器的另一个有效开始。在这一点,SVA执行序列 s_display1的display语句。标记2e显示了检验器的结束点。信号“b”的有效上升沿没能在2~5个时钟周期内出现,因此检验失败。由于第个序列没有匹配,序列相关的 display语句没有执行。SⅤA发出一个默认的出错信息。

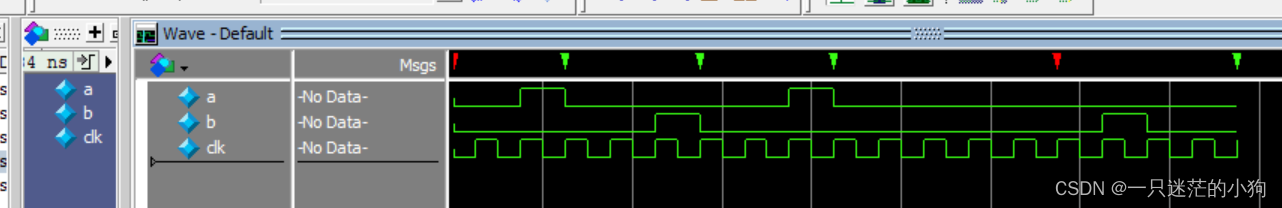

在波形窗口显示的断言结果如下所示:

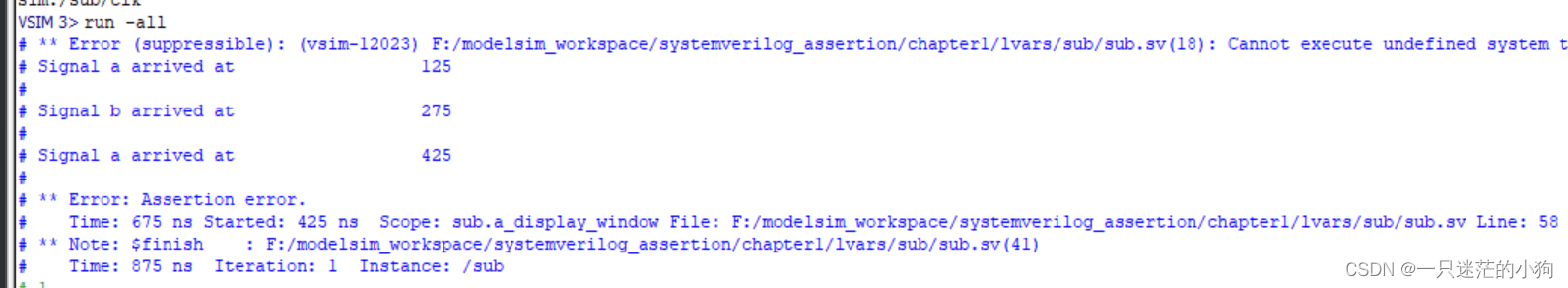

一个模拟日志的实例如下所示。

![2023年全球及中国溶瘤病毒治疗药物行业现状及发展趋势分析[图]](https://img-blog.csdnimg.cn/img_convert/763f6522342b7de3d215a85f8727cc2e.png)