平台:Vivado2021.1

芯片:xcku115-flva1517-2-i (active)

语言:VerilogHDL

参考文件:pg150.下载地址

pg150-ultrascale-memory-ip.pdf • 查看器 • AMD 自适应计算文档门户 (xilinx.com)

DDR4介绍

DDR4,即第四代双倍数据率同步动态随机存储器SDRAM。前面我们学习过DDR3,DDR2。那么DDR4相比他们又提升在哪里呢?

新建BD工程:此部分为搭建PCIE控制DDR4的工程。

关于xilinx的DDR4的IP核,我们用户可以使用两种方式建立,第一种就是使用XILINX提供的标准的用户侧接口,也就是我们所熟悉的User interface。如下所示。

还有一种就是直接使用AXI接口的DDR控制器,使用AXI模式下的DDR4接口,我们不需要熟悉复杂的DDR4协议。也不需要使用用户侧接口来自己搭建。在 XILINX提供的BD原理图中我们可以直接调用IP核,然后选择一键连接就可以将整个系统搭建完毕。

如上图所示,我们使用一个标准的PCIE+DDR的存储模式。我们知道PCIE的XDMAIP核拥有三个接口,分别是AXI_MM,AXI_LITE,AXI_STREAM模式。其每一个接口也代表了不同的使用方法,比如我们AXI_MM接口,他拥有完整的AXI4协议。AXI协议包含读地址,读数据,写地址,写数据,写响应这几种。所以往往我们使用该接口来区分数据通道或者带有数据存储如BRAM,DDR等。而AXI_LITE就是AXI协议的基础版,对于PCIE来说我们一般用它来实现点到点的读写功能。而AXI_STREAM模式就是只包含数据流的AXI总线,由于该总线不含地址,所以速度上也是会快一点,我们往往用该总线传说不包含地址的数据流。例如FIFO等。

上图中我们在AXI_MM分别连接了DDR4的IP核,与内部存储的BRAM。而AXI_LITE上可以忽略掉。

本文章主要介绍DDR4IP核的配置和PCIE加DDR4的功能验证。

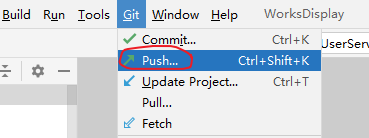

关于PCIE的设置。

这里选择GEN3*8模式,采用100mhz的参考时钟,使用AXI_MM接口,AXI数据位宽为256bit。

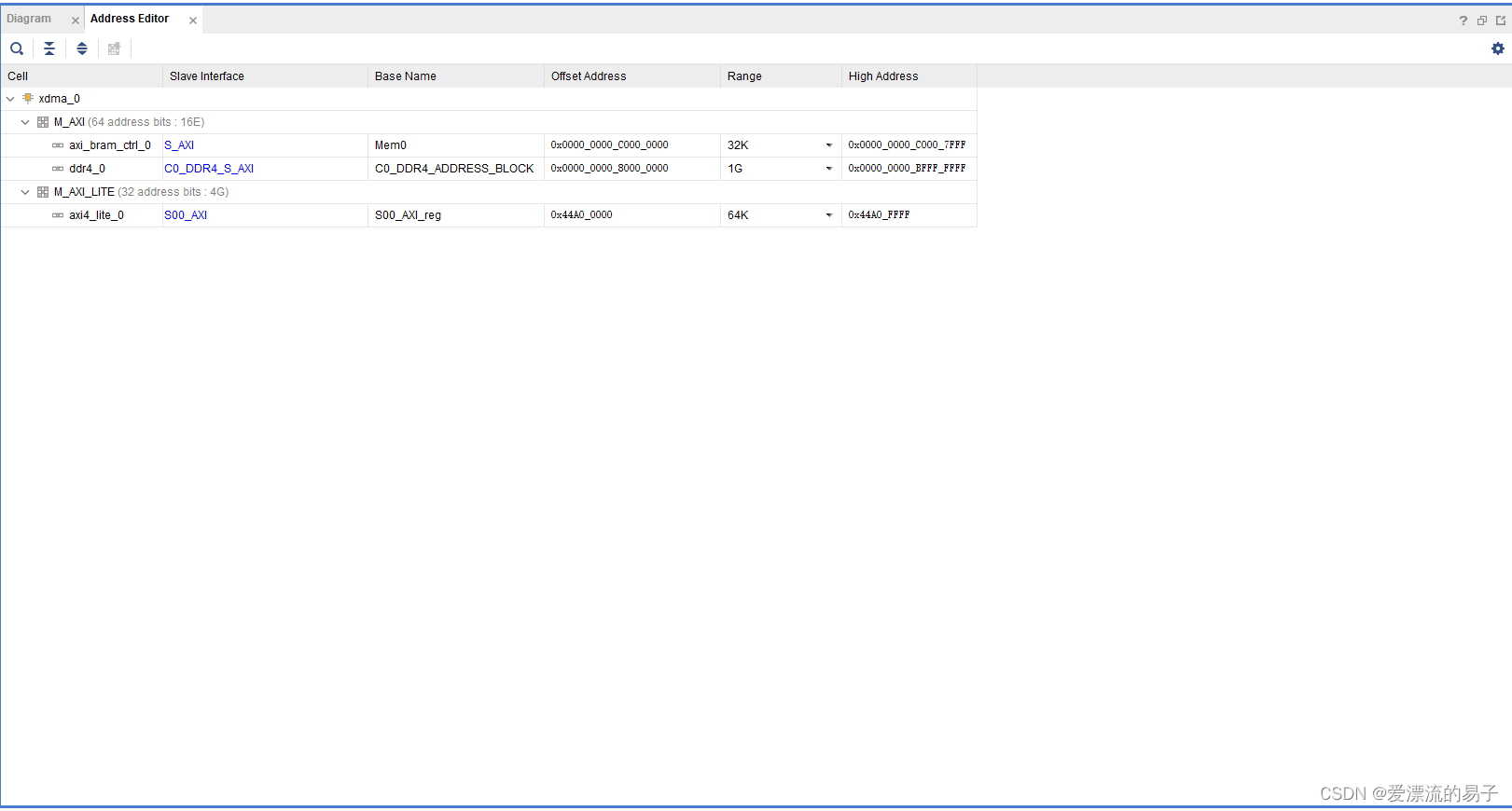

关于地址分配。

使用64位AXI地址。

C000_0000上挂BRAM。

8000_0000上挂DDR4。

测试的过程也很简单通过DMA模式向DDR4IP上写入数据和读出数据。

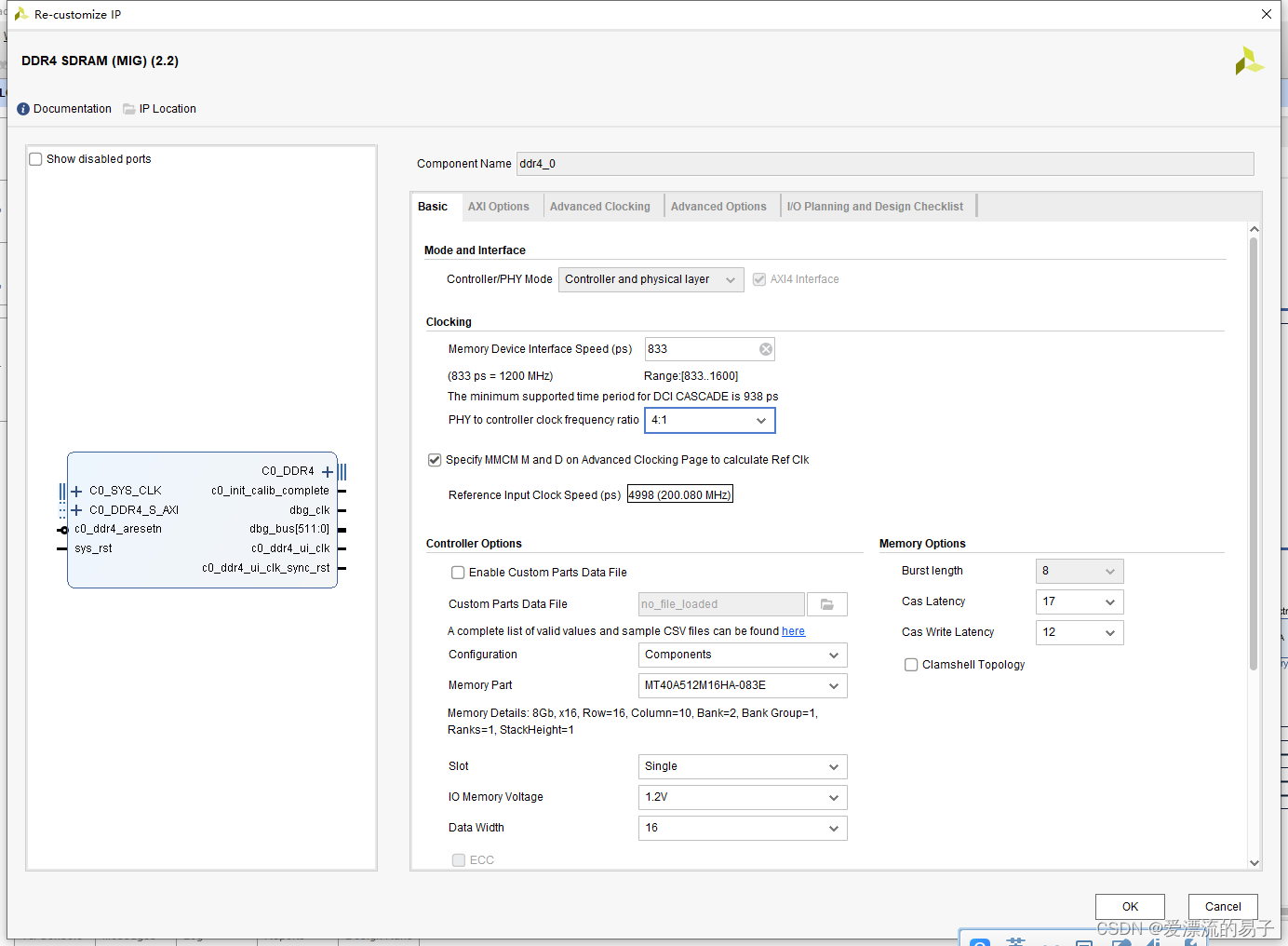

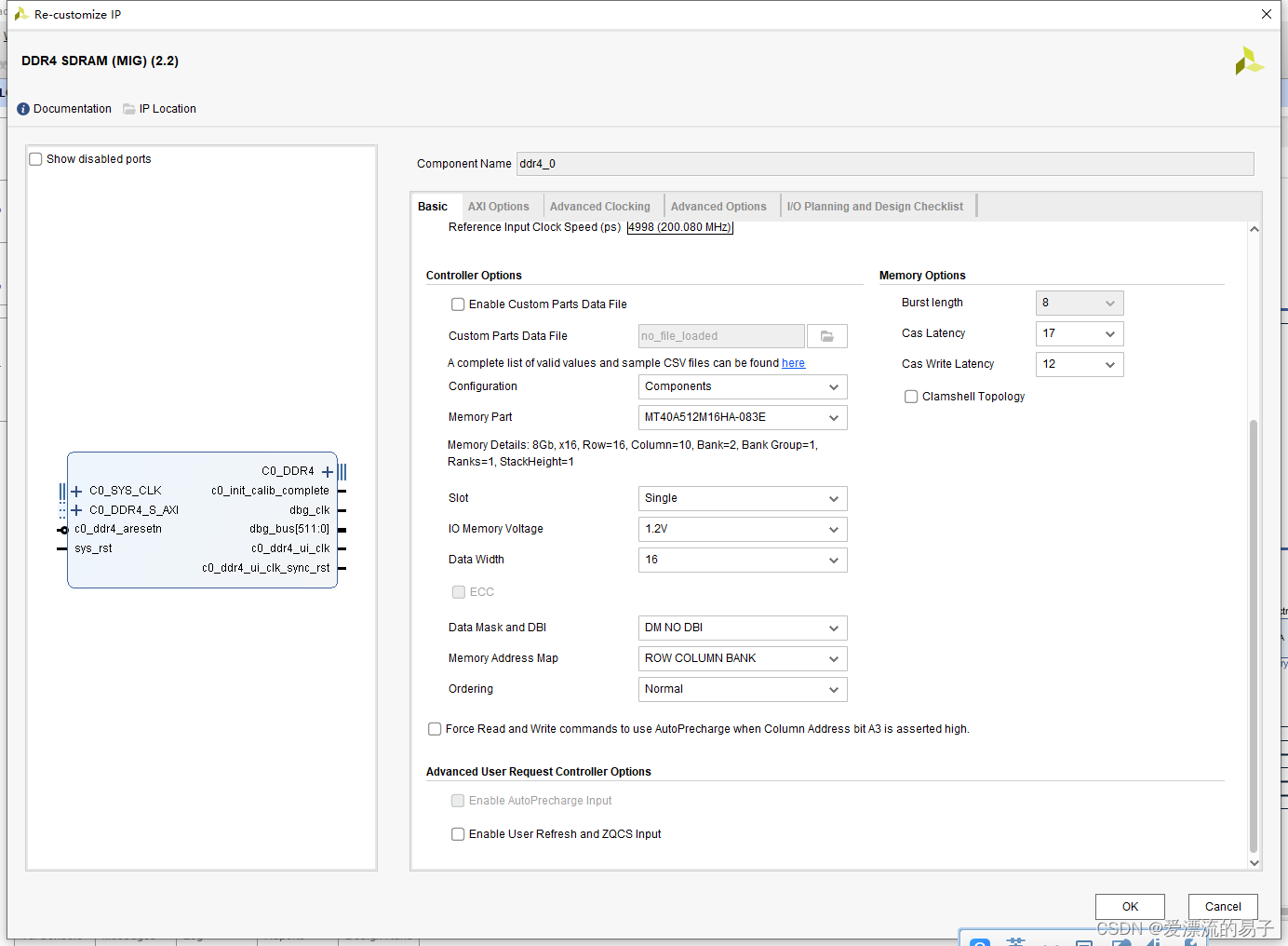

关于DDR4的IP核,在Ultra系列上DDR4的IP核与以往的DDR3DDR2的配置有一定的差异。

关于我们使用的这款DDR4内存条,根据其数据手册,DDR4支持的最高频率为1200MHZ,使用上下边沿传输数据也就是2400MHZ。这里我们来简单算一算DDR4的速率,这里我们使用一片,即数据位宽为16bit。所以理论上的数据率为2400MHZ*16bit=4800MB/S。如果使用内存模组最高可以达到64bit的数据位宽, 这时理论上的数据率为2400mhz*64bit=19200MB/S。速度还是相当的给力的。这里还需要关注一个地方,我们选择接口速率为1.2GHZ的时候,这里的参考时钟我们看到可以选择的范围为200.08mhz,而我们实际使用的参考时钟是200mhz的,这里我们实际测试下来并不会影响数据收发。

接下来四DDR4型号选择,这里要和你们原理图上的硬件型号相对应。关于数据位宽,如果原理图上设置的一组几片就选择多少。我们这里只使用了一片,就设置为16位。前面提到过64bit的数据位宽,按照这里就是使用了四片DDR,他们级联起来就是64bit的数据位宽。后面的突发位宽这里可以保持默认。

AXI选项页

AXI数据位宽支持选择。我们选择32位。

时钟配置界面

可以看到你的参考时钟和你第一页配置的一致。

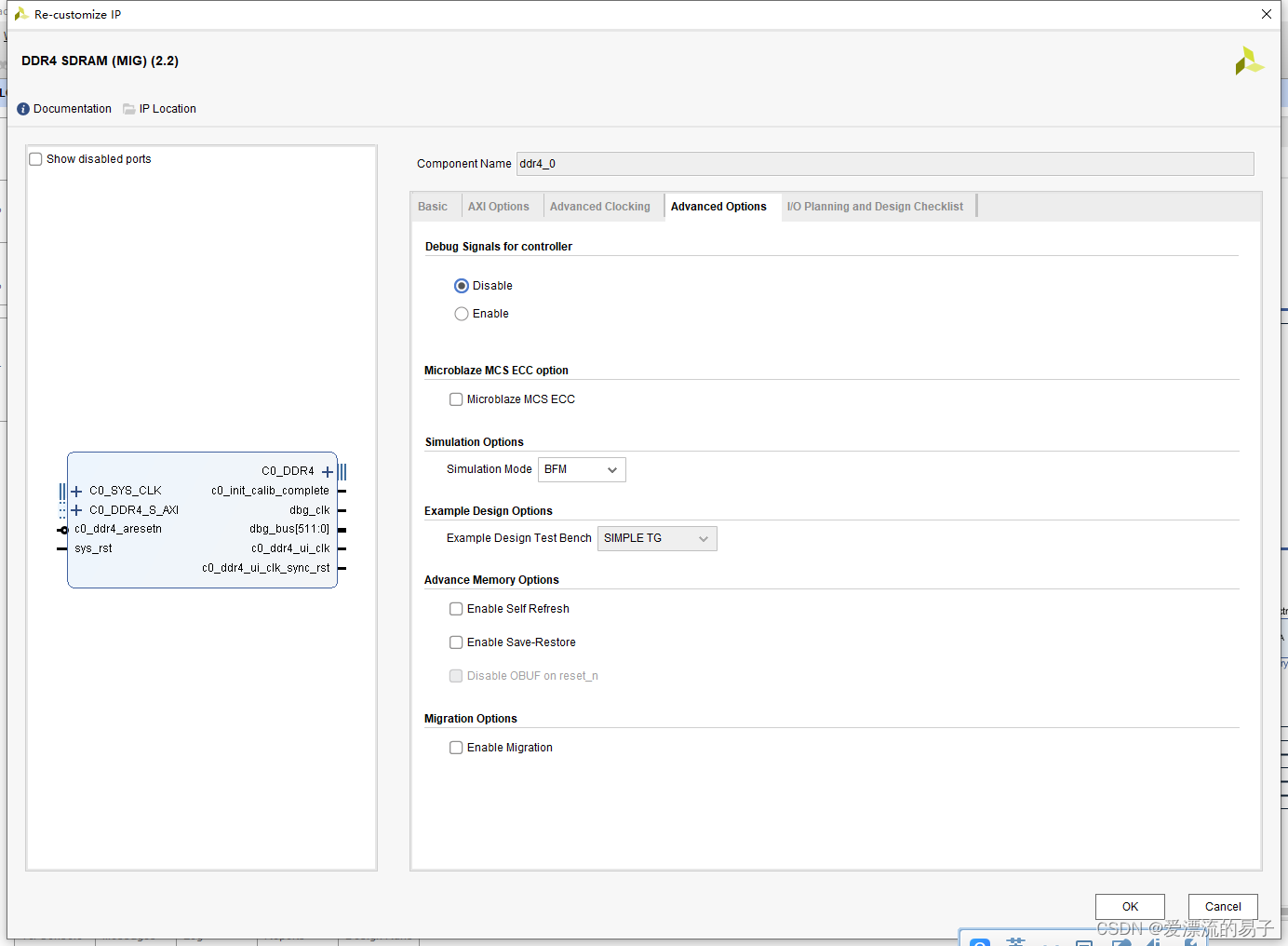

高级选项

默认就好

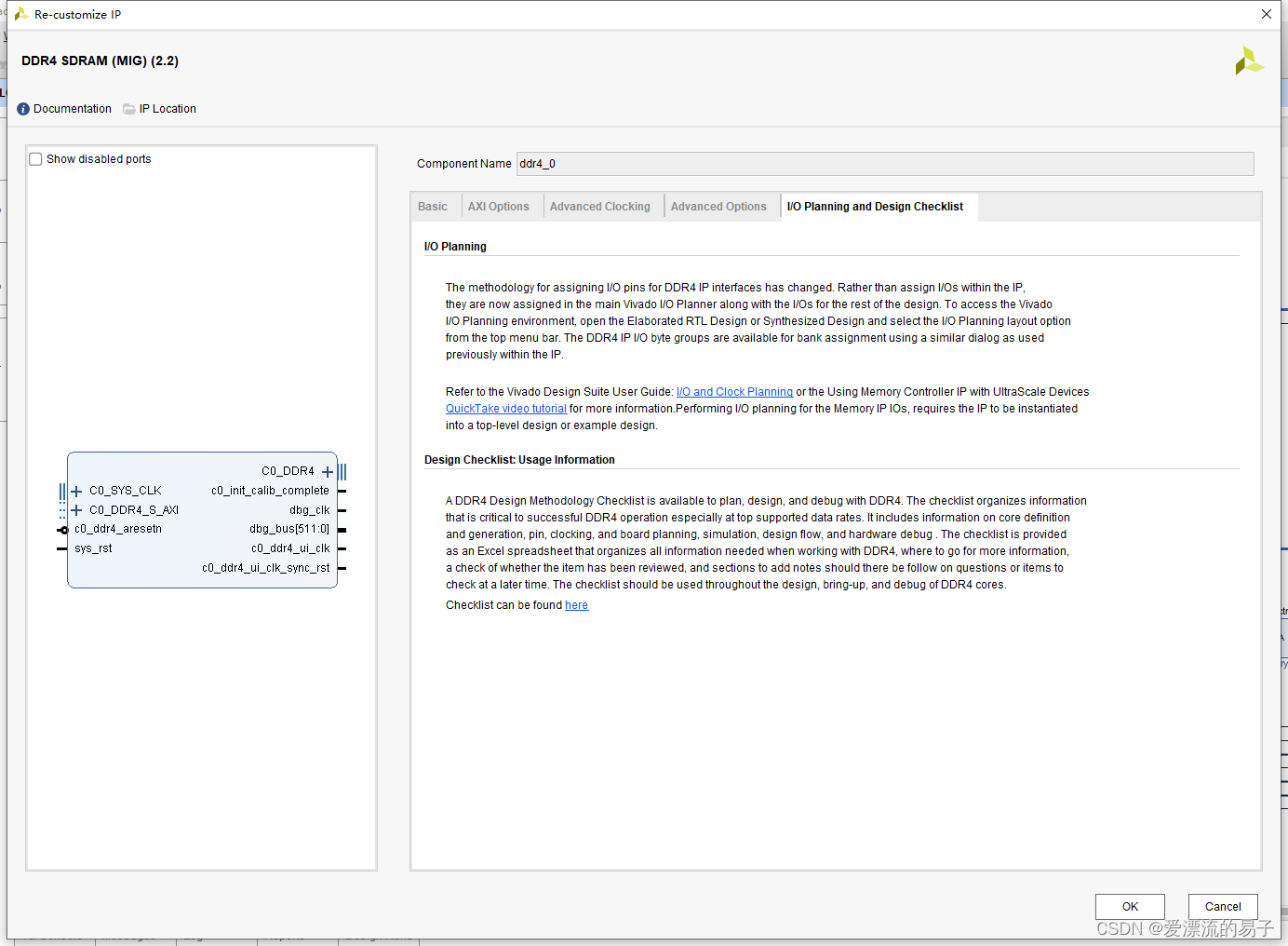

I/O Planning and Design Checklist Tab

默认就好。

这里我们就新建好了。

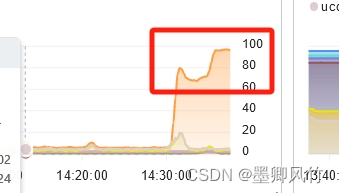

工程测试。

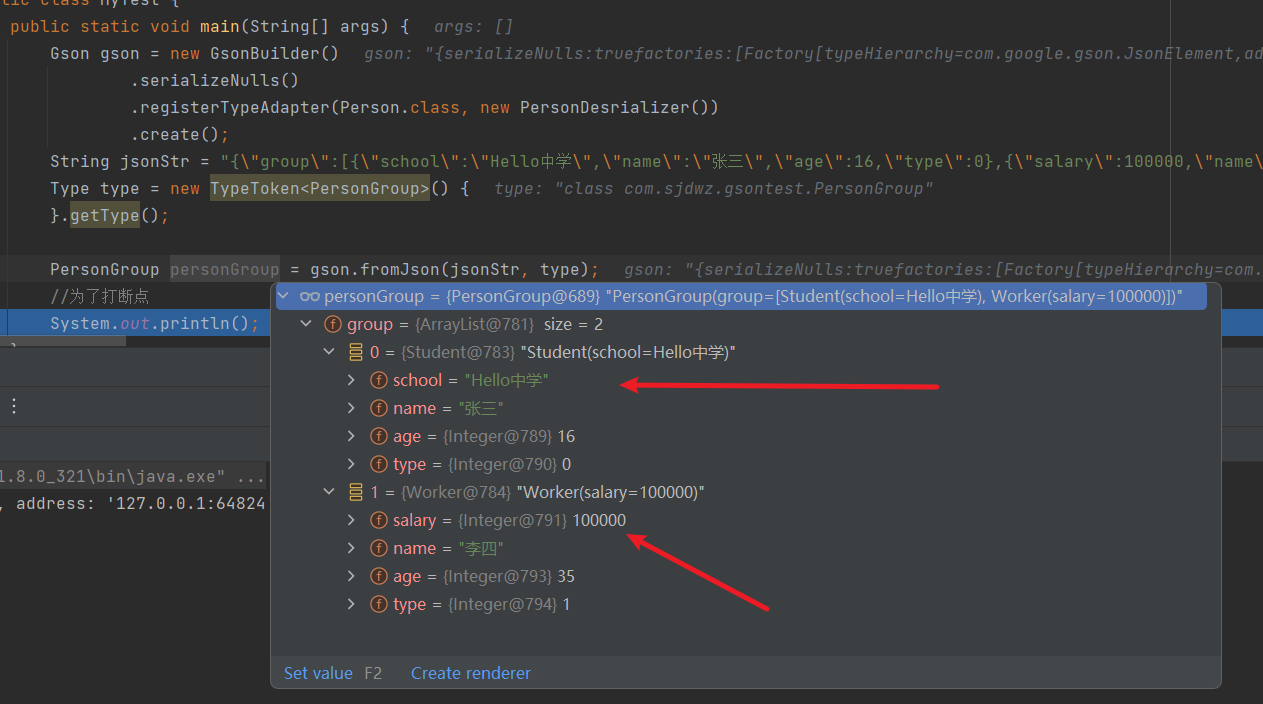

由于我们是通过PCIE直连DDR4的模式。我们可以直接使用xilinx提供的测试函数取读写DDR4的数据。

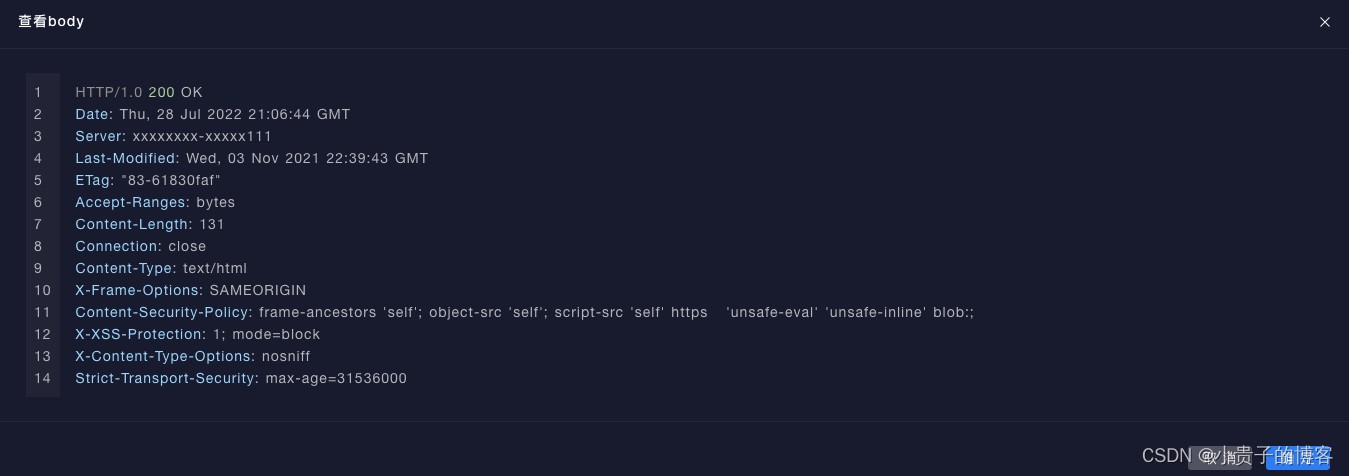

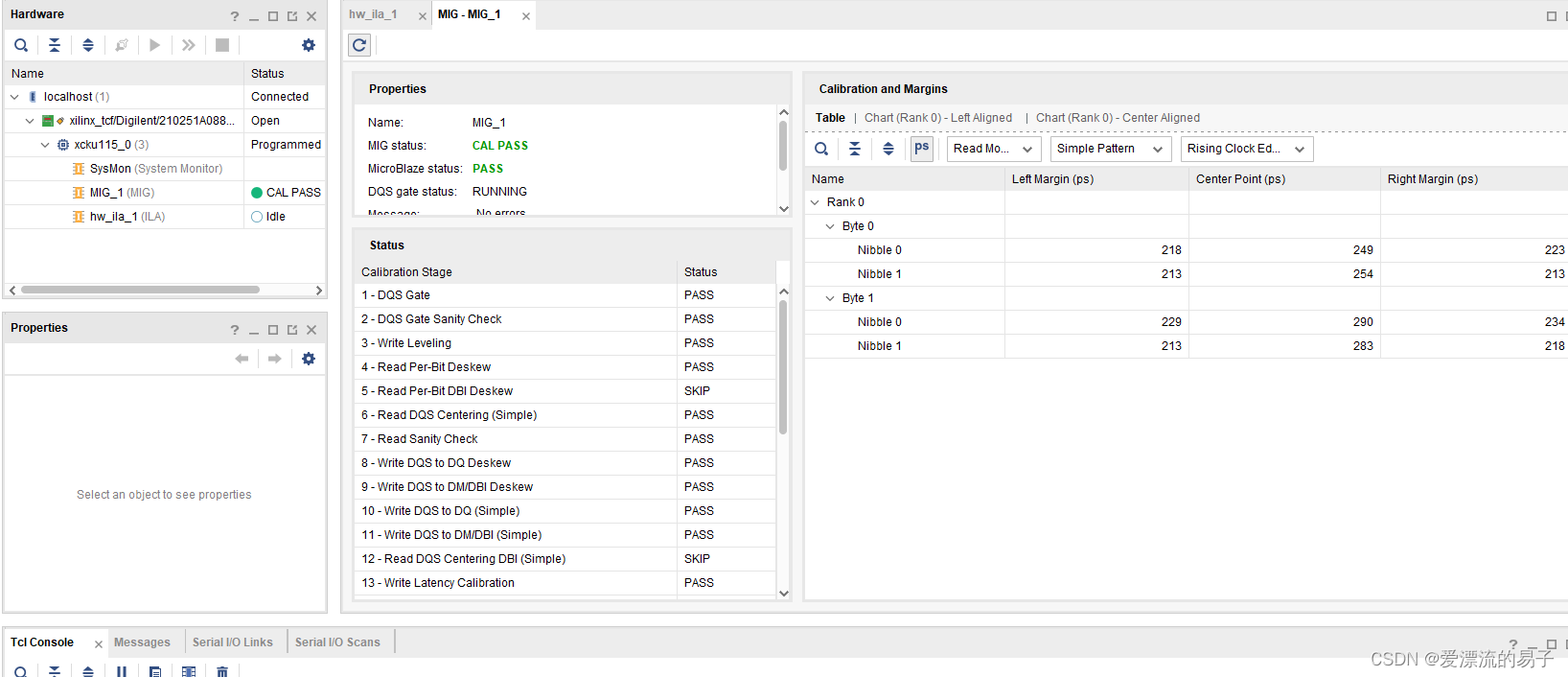

在下载成功后,会自带的有个这个界面。我们在此界面上可以看到绿色的CAI PASS。表明DDR4初始化成功。此外在调试的过程中,会存在很多问题在此界面中。可以看到DDR4初始化到哪一个步骤下失败。从而取考虑硬件上的设计错误。

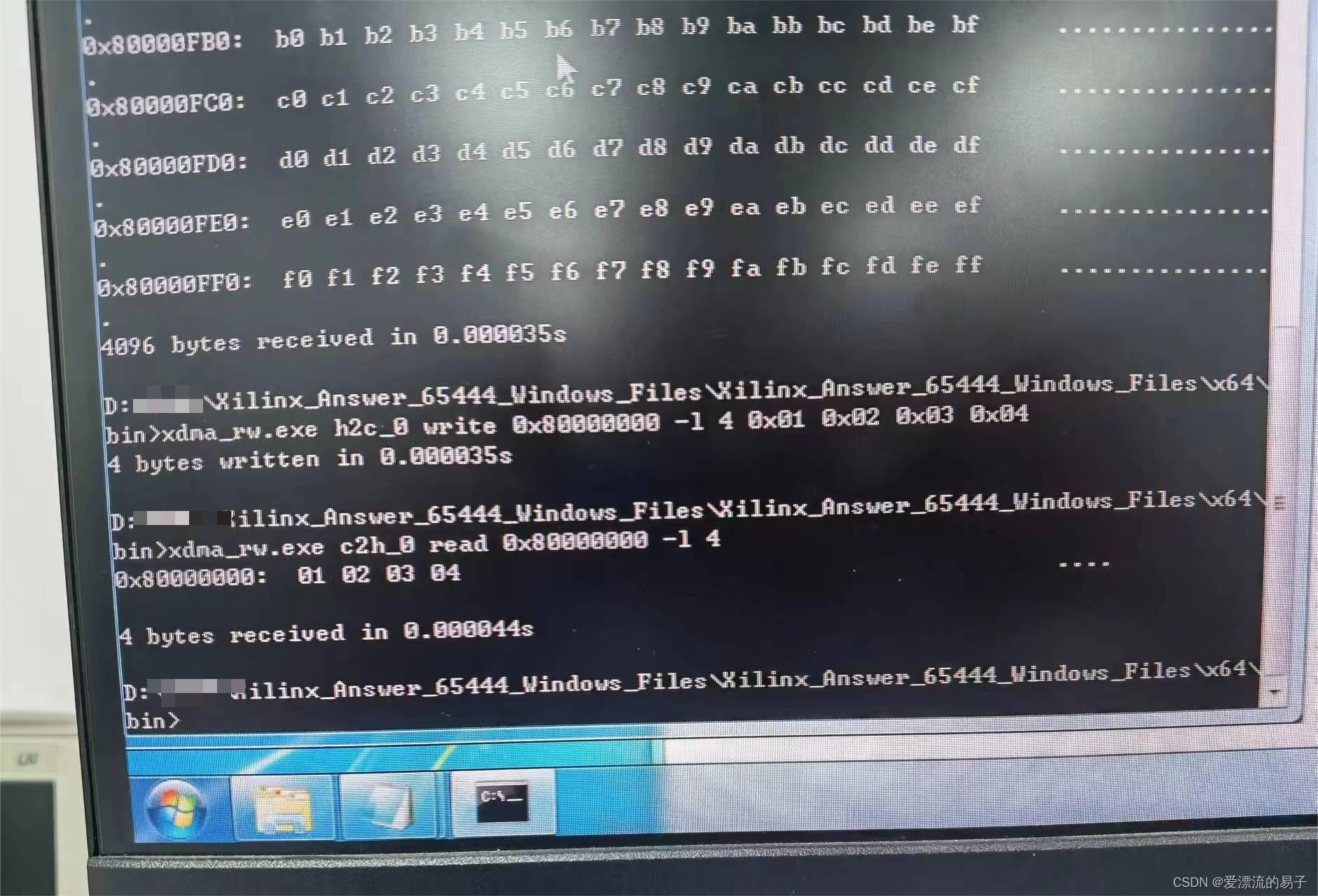

使用PCIE 下发数据。

分别测试了向0x8000_0000写入数据。(即向DDR4写入)

从0x8000_0000读出数据。(即从DDR4读出)

写入了4K的bin文件。后读出。数据一致。表明读写正常。

DDR4的测试完成,是不是发现xilinx把这些IP做的越来越简单。

DDR4的测试完成,是不是发现xilinx把这些IP做的越来越简单。

![[ROS2系列] ORBBEC(奥比中光)AstraPro相机在ROS2进行rtabmap 3D建图](https://img-blog.csdnimg.cn/933f27029fa743439f5389f503e9f7a1.png)