👉个人主页:highman110

👉作者简介:一名硬件工程师,持续学习,不断记录,保持思考,输出干货内容

参考资料:《镁光DDR数据手册》

目录

DDR2 SDRAM介绍

DDR2相对DDR的变化

DDR2 SDRAM芯片框图

DDR2 SDRAM的mode register

DDR2 SDRAM介绍

到DDR2了,同样以镁光的数据手册为主要参考,我们来介绍它的主要特性以及相对DDR的新增功能和变化。

DDR2相对DDR的变化

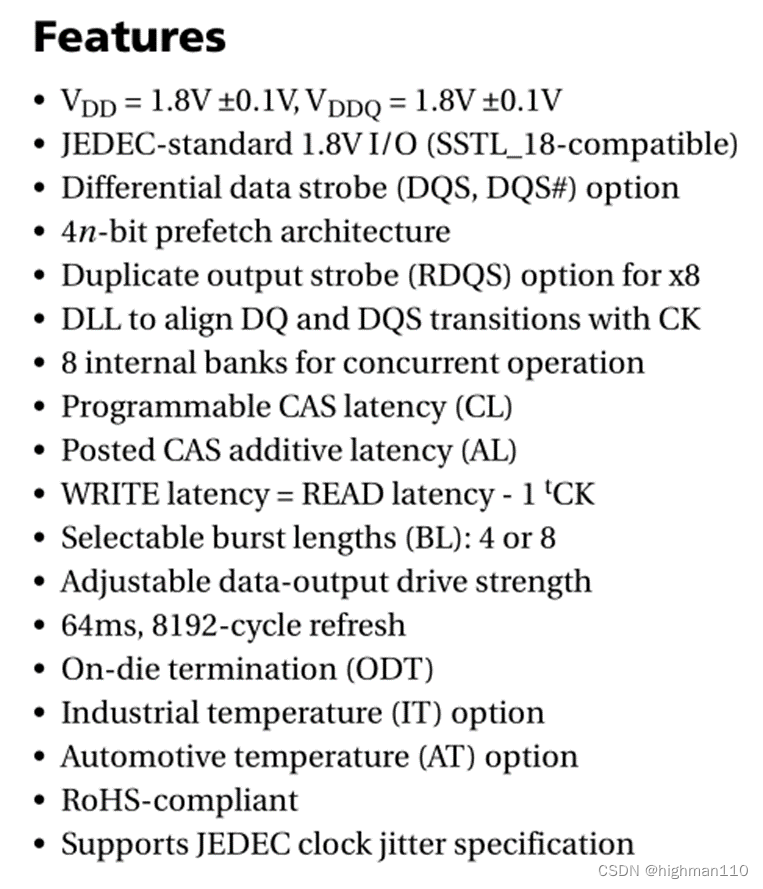

以上是镁光DDR2数据手册列出来的主要特性,下面逐条解释:

1、VDD = 1.8V ±0.1V, VDDQ = 1.8V ±0.1V

DDR2核心电压和IO电压均为1.8V,DDR为2.5V。

2、JEDEC-standard 1.8V I/O (SSTL_18-compatible)

DDR2 IO电平为SSTL_18,DDR为SSTL_2。

3、Differential data strobe (DQS, DQS#) option

DDR2 DQS为差分信号,DDR单端信号。

4、4n-bit prefetch architecture

DDR2为4n预取,DDR为2n。

5、Duplicate output strobe (RDQS) option for x8

RDQS,与DM功能复用,只有x8颗粒有此引脚定义,后面代数的DDR此引脚称为TDQS,主要用于x4和x8颗粒混用的场景,后面会介绍。

6、DLL to align DQ and DQS transitions with CK

使用DLL来使DQ和DQS与CK对齐传输,这个DDR2与DDR基本一样。

7、8 internal banks for concurrent operation

DDR2内部有8个bank可同时操作,DDR通常只有4个bank。

8、Programmable CAS latency (CL)

可编程CL,DDR的CL也可以编程。

9、Posted CAS additive latency (AL)

DDR2新增了CAS前移机制,这里产生了一个附加延迟,后面详细讲。

10、WRITE latency = READ latency - 1tCK = AL + CL - 1tCK

DDR2的WL相当于DDR中的tDQSS,只是DDR2由于CL可编程,相当于WL也可编程,DDR中的tDQSS是固定的。

11、Selectable burst lengths (BL): 4 or 8

DDR2突发长度可选4或8,DDR是2、4或8。为什么没有2了,前面将预取的时候解释过。

12、Adjustable data-output drive strength

DDR2的IO输出驱动强度可调,DDR是不可调的。

13、64ms, 8192-cycle refresh

刷新周期64ms,这个与DDR一致。

14、On-die termination (ODT)

DDR2新增支持片内终端匹配,DDR不支持。

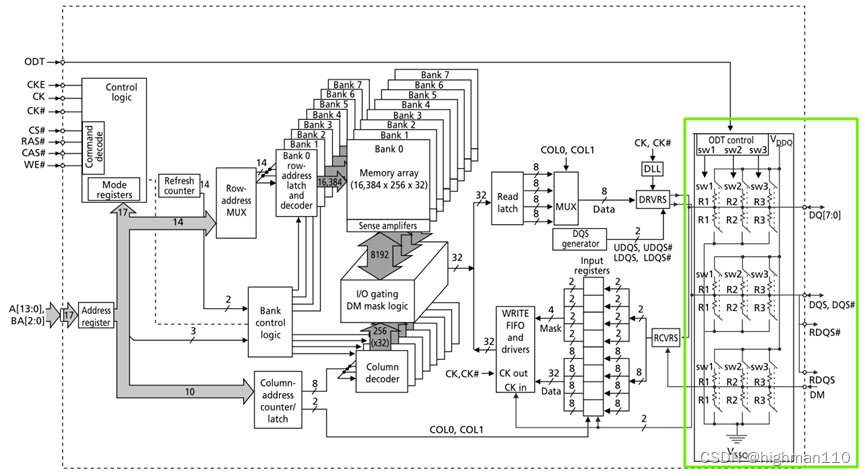

DDR2 SDRAM芯片框图

上图绿框是DDR2相对DDR的主要区别,新增的ODT电路,另外bank数变为了8个,预取为4n预取,所以针对这个x8的颗粒,IO gating出来的总线宽度是32bit,然后用两个低位列地址COL0、COL1来控制MUX的输出先后顺序。其他的与DDR基本相同,就不多提了。

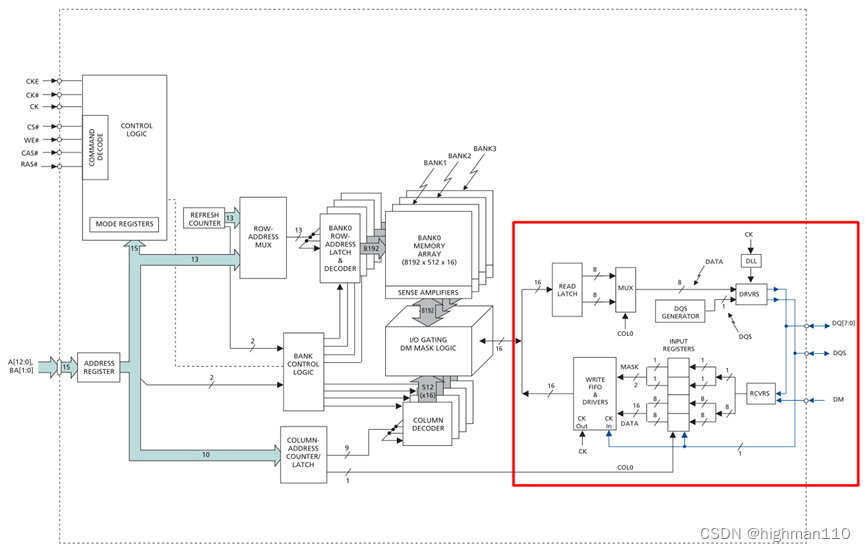

把DDR的框图再贴出来一起对比:

DDR2 SDRAM的mode register

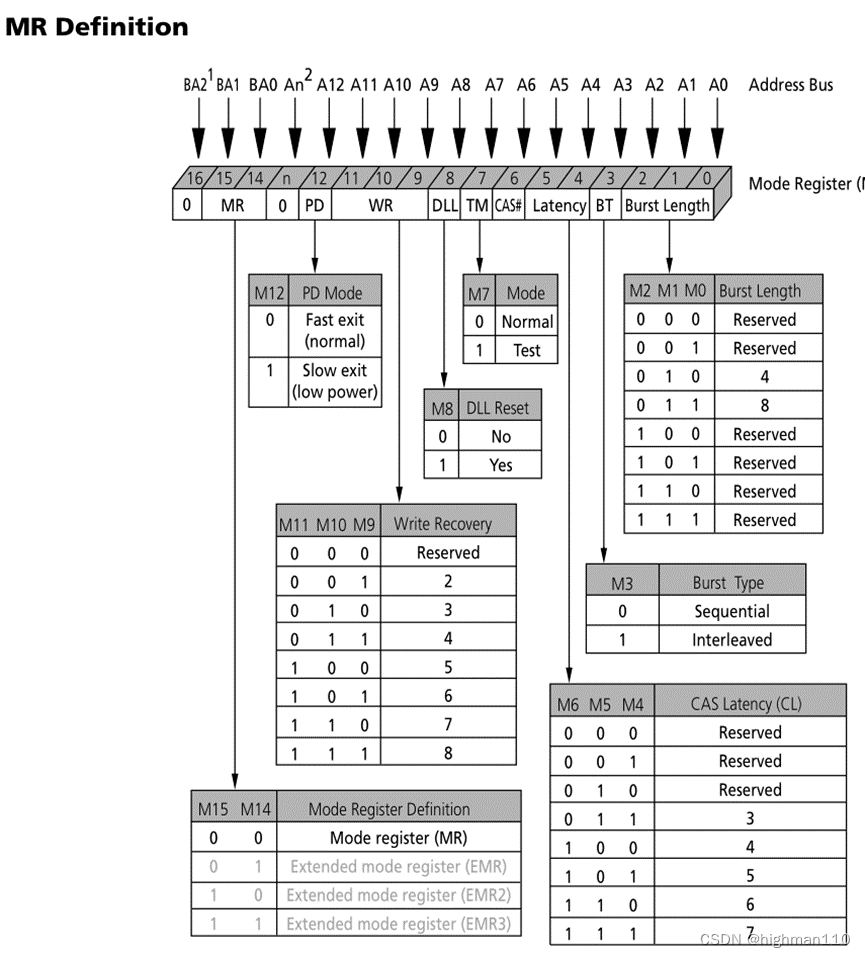

DDR2的模式寄存器有四个:MR、EMR、EMR2、EMR3。

与DDR相同的就不多说了,说一下差异点:

Bit[11:9]:write recovery,写数据之后如果要进行预充电,则需要在数据完全写入后才能预充电,这段时间称为tWR,单位为ns,而这里的WR单位为tCK,其值等于tWR / tCK,四舍五入取整数。

Bit12:PD mode,为0表示快速退出PD模式,这种情况下的PD需要DLL持续运行;为1表示缓慢退出PD模式,这种情况的PD DLL可以冻结,功耗能更低点。

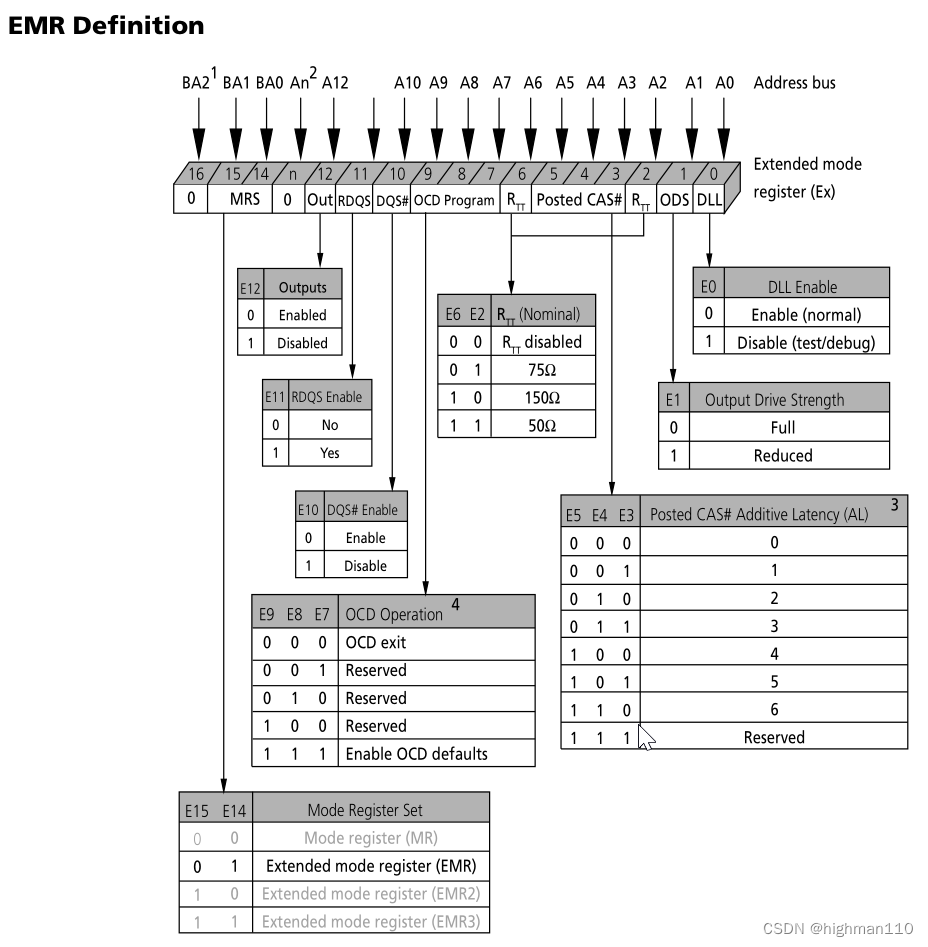

Bit0:使能或不使能DLL;

Bit1:输出驱动强度配置;

Bit2、Bit6:片上终端匹配电阻值配置;

Bit[5:3]:CAS前置配置;

Bit[9:7]:离线驱动调整,OCD的作用在于调整DQS与DQ之间的同步,以确保信号的完整与可靠性,让DQS的高低电平与DQ的高低电平更好地对齐。这是JEDEC规范定义的可选功能,镁光的这颗DDR2没有此功能,在初始化时先使能OCD default模式,初始化后需要配置为退出OCD模式。具体的OCD功能后面讲。

Bit10:DQS差分信号使能,0表示使用差分信号,1表示使用单端信号;

Bit11:RDQS使能,如果使能就是DQS功能,不使能就是DM功能。x8颗粒与x4颗粒的条子混用时,x8的条子要使能;

Bit12:输出使能。

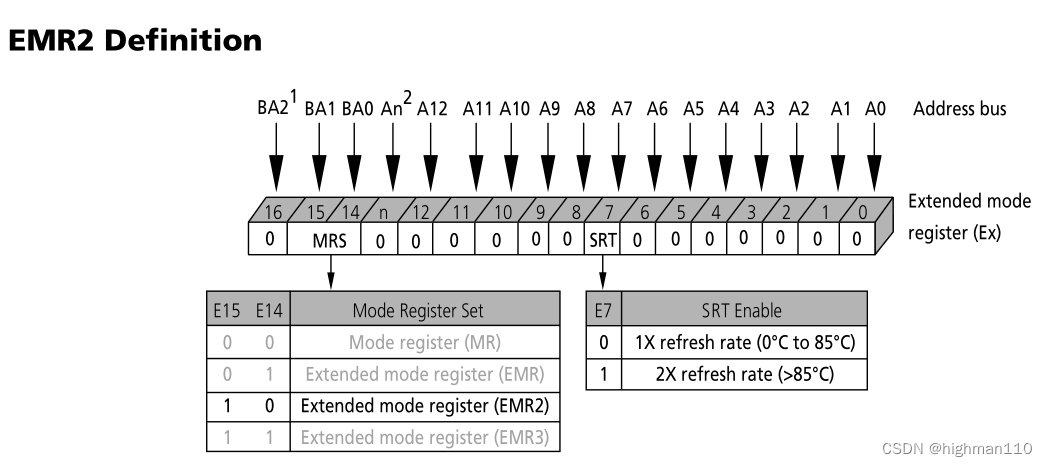

Bit7:刷新率配置,JEDEC规范规定,如果Tc超过85度,则DDR的刷新率要翻倍,普通消费级刷新周期为64ms,工业级或汽车级的刷新周期为32ms。

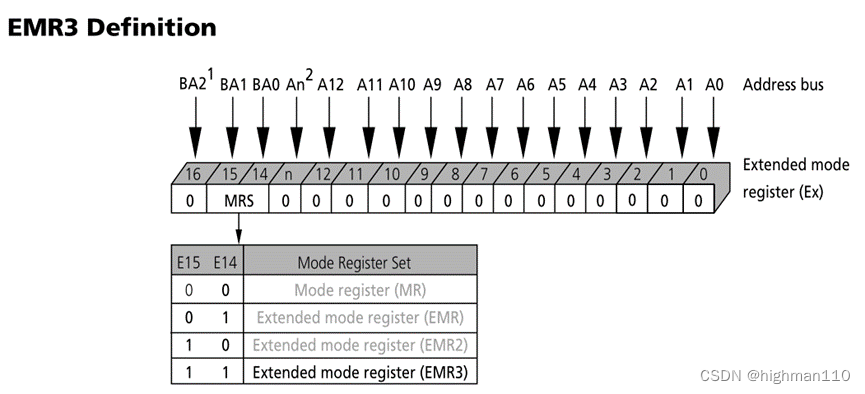

EMR3目前是预留的,初始化时需全部设为0。

今天先到这里,下篇介绍DDR2的主要技术。