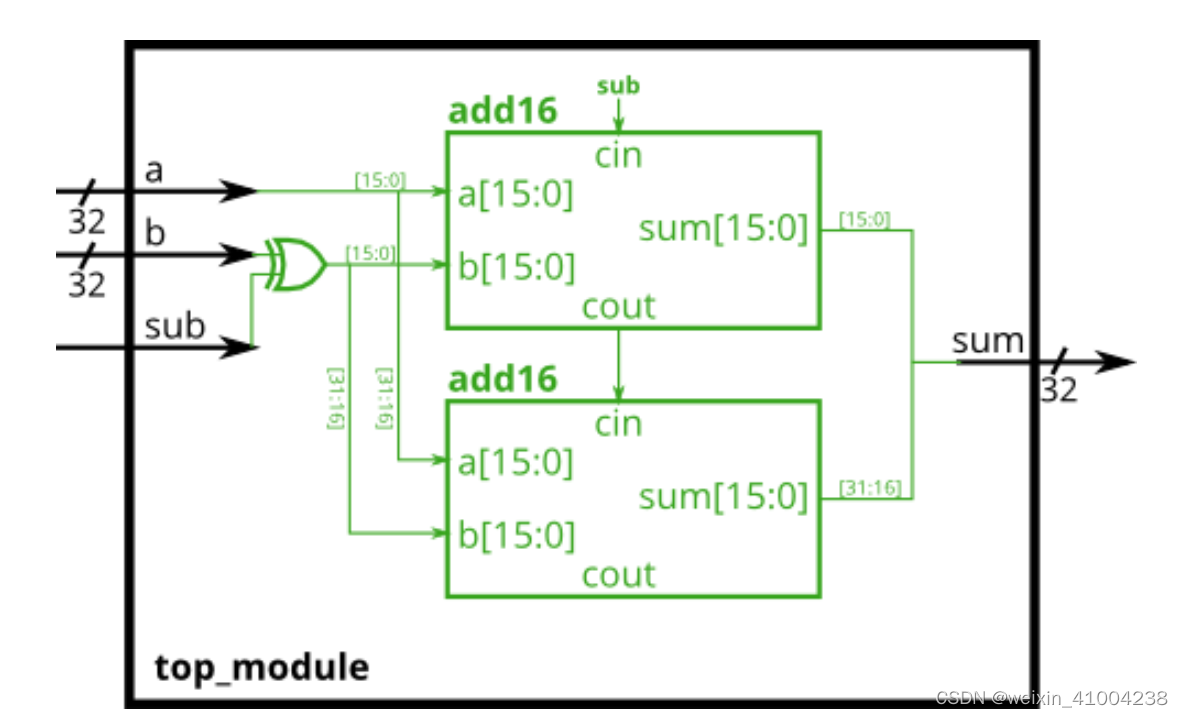

module top_module(

input [31:0] a,

input [31:0] b,

input sub,

output [31:0] sum

);

wire w1;

add16 add16_1(a[15:0],b[15:0]^{16{sub}},sub,sum[15:0],w1);

add16 add16_2(a[31:16],b[31:16]^{16{sub}},w1,sum[31:16],);

endmodule注意:sub位扩展

![[C]嵌入式中变量存储方案](https://img-blog.csdnimg.cn/045f9ad988bd412cab38dd54d17b2070.png)