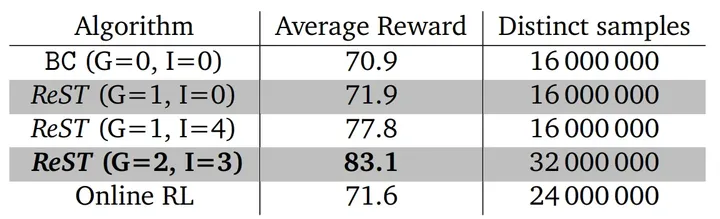

一、数据手册学习

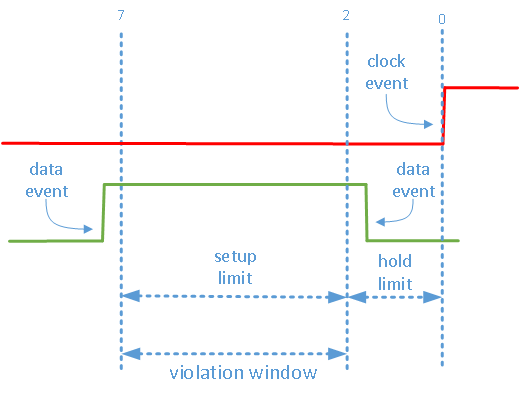

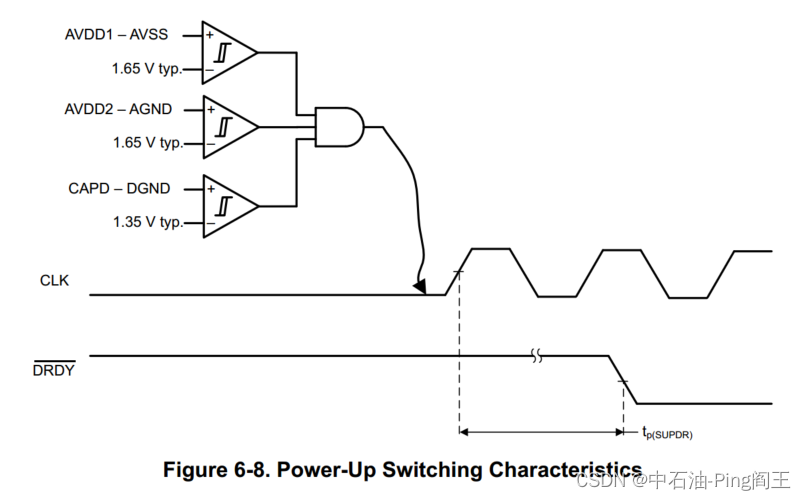

1.1时序图

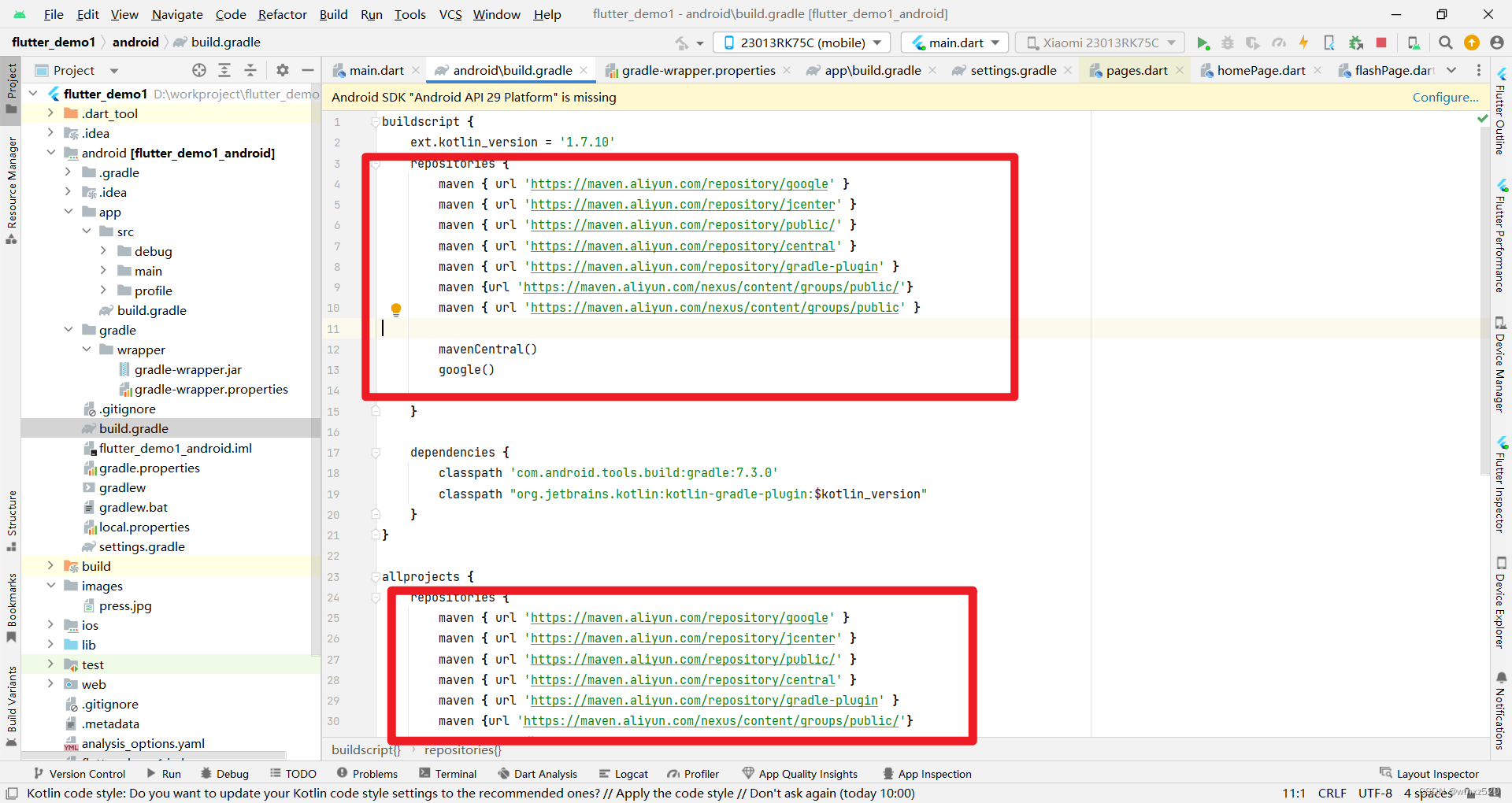

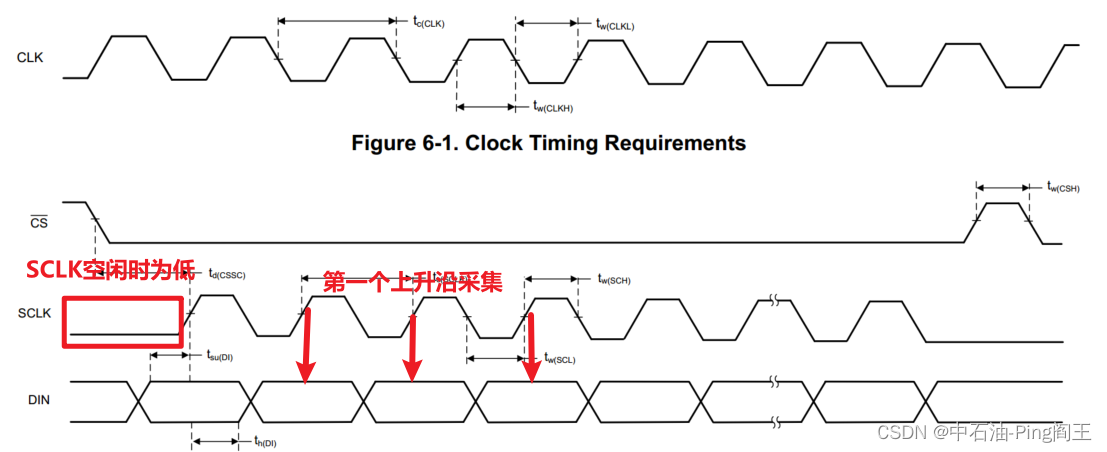

SPI时序图,这是很重要的一个地方,一定要在代码中将SPI配置成对应的模式。

先放一堆截图在这吧,一些引脚的功能及特性还未看到,等具体了解之后再详细介绍下面几张截图的时序:

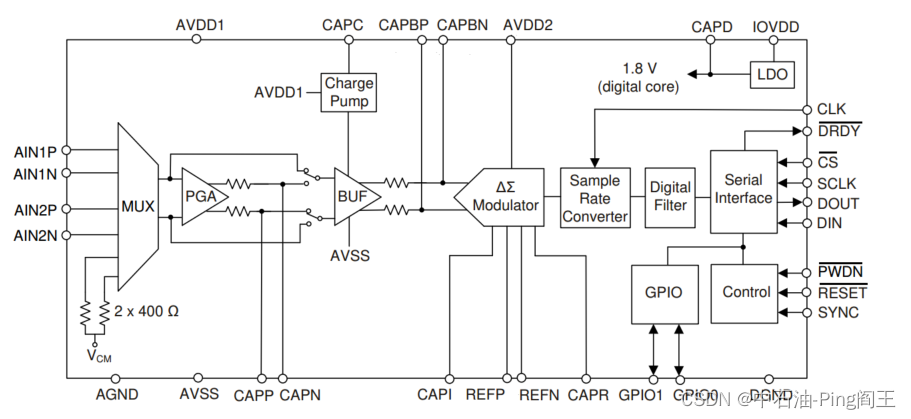

1.2 内部框图及各部分介绍

注意:该芯片的噪声特性取决于参考电压,参考电压为4.096V或者5V时,噪声性能最好;参考电压为2.5V(设计时需要注意,若参考电压设计为2.5V,那么AVDD1要设计为3.3V而不是5V),会降低噪声特性。

下图是芯片的内部框图,稍后会对各个模块进行一一的介绍

部分引脚简介:

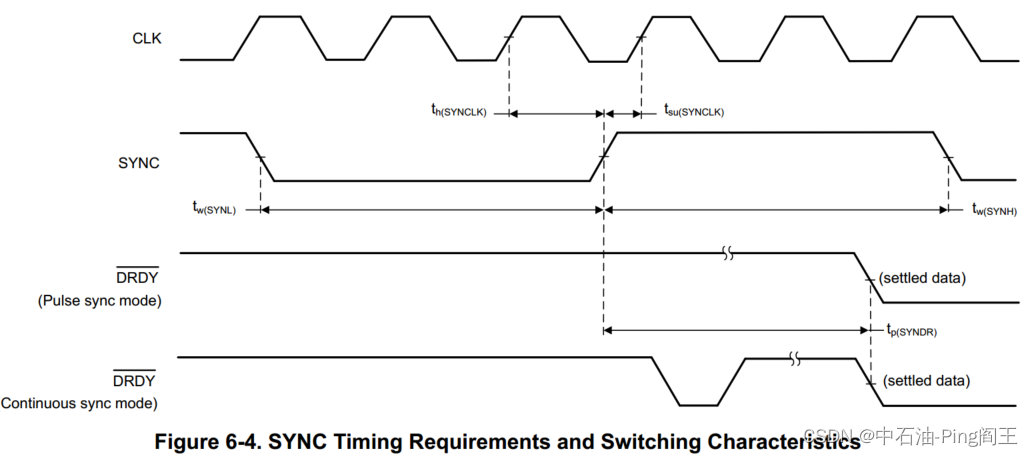

- SYNC:ADC同步引脚,有脉冲同步和连续同步

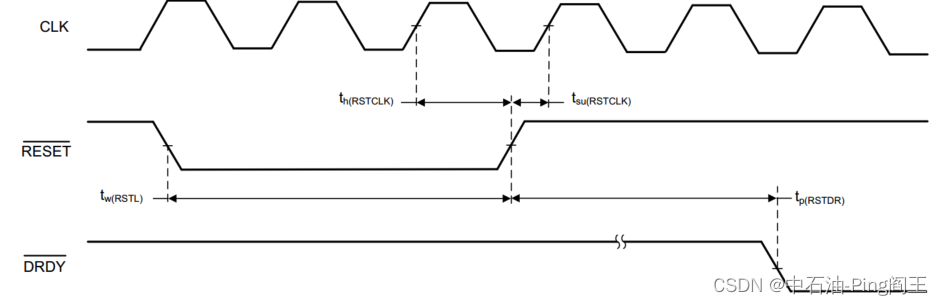

- RESET:复位引脚,由施密特触发输入,抗噪声

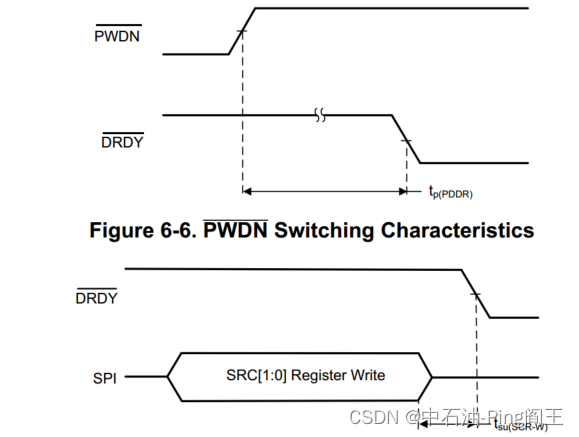

- PWDN:在ADC不使用时切断电源

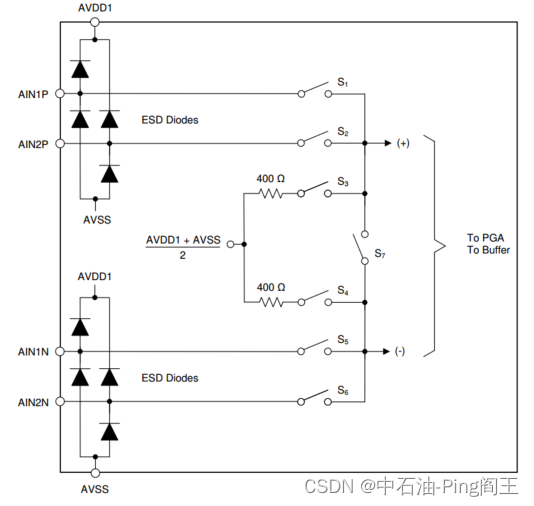

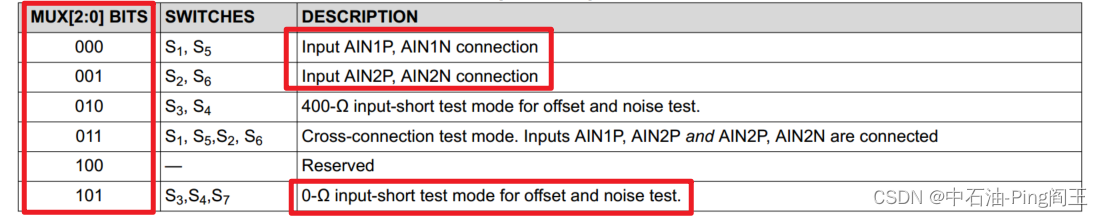

1.2.1 模拟输入和多路复用器

在输入端已经集成了ESD(静电保护)二极管,不再需要我们自己设计外围的静电保护电路;ADC包含两个差分输入通道,多路复用器在两个差分输入之间选择进行测量。多路复用器还提供了测量噪声和偏置的测试模式。短输入测试配置可带或不带400-Ω电阻,以模拟800-Ω检波器产生的热噪声。多路复用配置如下表所示。

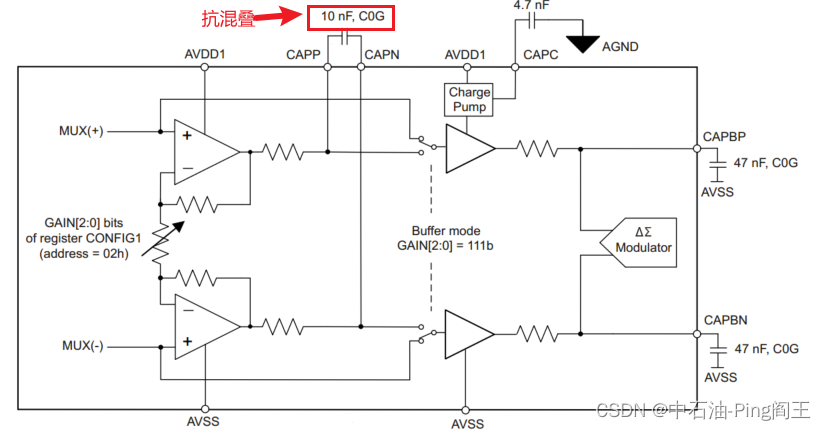

1.2.2 可编程增益放大(PGA)和缓冲(Buffer)

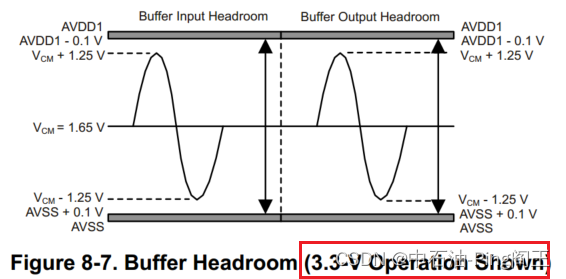

缓冲操作会禁用PGA bias,降低设备功耗。“当AVDD1 = 3.3 V时,由于PGA增益= 1的输入余量有限,因此必须在此条件下使用缓冲器。”–对于手册的这句话,我个人理解是:如果设计AVDD1为3.3V,那么PGA不能使用,只能使用Buffer(个人理解,如有错误,还请指正!)。

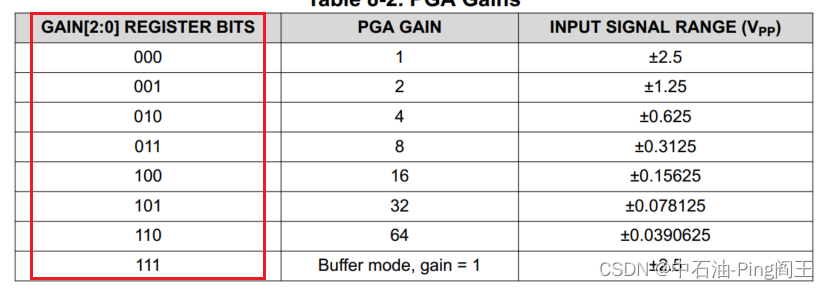

PGA可提供1~16的模拟增益,通过数字缩放提供32和64的增益。

PGA增益由CONFIG1寄存器的gain[2:0]位编程:

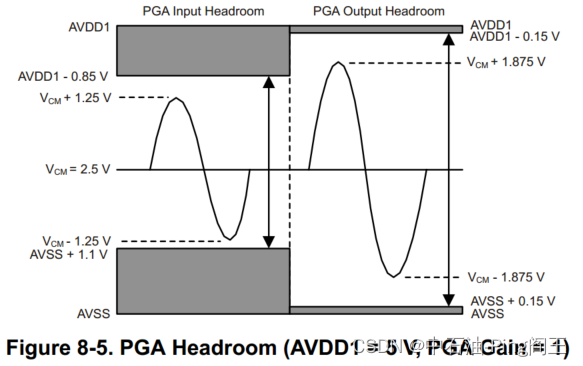

下图显示了AVDD1 = 5v、输入共模电压= 2.5 V、差分输入电压=±2.5 VPP、增益= 1时的输入输出电压。PGA输入电压的绝对最小值和最大值(1.25 V和3.75 V)分别为差分信号电压加共模电压的±1/2(±1.25)。PGA在负峰值处提供0.15 v的输入电压裕量,在正峰值处提供0.4 v的输入电压裕量。如图所示,当ADC工作在4.096 v或5v参考电压下时,PGA增益增加了× 1.5。PGA在正、负峰值处提供0.475 v输出电压裕度。

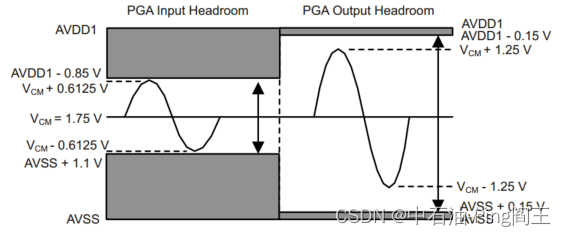

当AVDD1 = 3.3 V工作时,PGA不支持±2.5-VPP的输入信号。对于±1.25 - vpp的输入信号(PGA增益= 2),通过将共模电压提高0.1 V至AVSS + 1.75 V来增加输入净空。下图给出了AVDD1 = 3.3 V、VCM = 1.75 V、输入信号=±1.25 VPP、增益= 2时的输入输出工作净空。当VREF = 2.5 V时,PGA使用正常增益缩放。

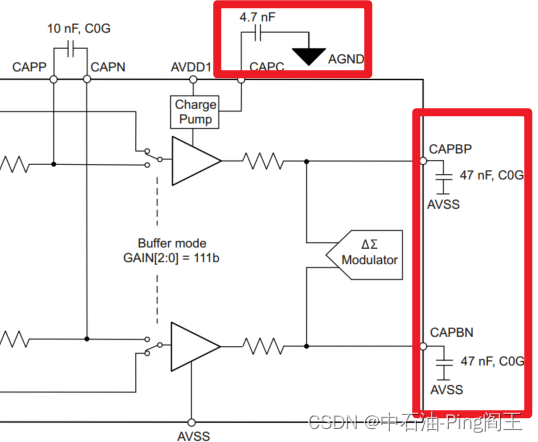

该芯片有一个缓冲选择,可以绕过PGA,降低功耗。当AVDD1工作在3.3 V时,使用±2.5 vpp输入信号缓冲器。通过设置CONFIG1寄存器的GAIN[2:0] bits = 111b来启用缓冲区操作。

下图为AVDD1 = 3.3 V、VCM = 1.65 V、输入信号=±2.5 VPP时的缓冲电压净空。当AVDD1 = 3.3 V工作时,缓冲器有足够的电压余量,可以承受±2.5-VPP的输入信号。

无论PGA或缓冲操作,从每个缓冲输出连接两个47-nF, C0G介电电容器到AVSS (CAPBP和CAPBN)。电压电荷泵增加了缓冲输入的操作净空。在CAPC和AGND之间连接一个外部4.7-nF电容器,用于电荷泵操作。

1.2.3 参考电压输入

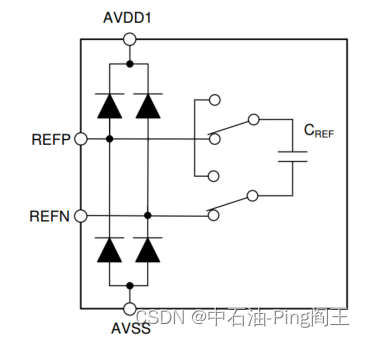

该芯片提供三种参考电压选择:5 V、4.096 V或2.5 V。使用VREF = 5 V或4.096 V实现最大动态范围性能,这需要AVDD1 = 5 V才能运行。如果AVDD1 = 3.3 V,则限制参考电压为2.5 V(一定要注意!!!)。通过CONFIG1寄存器的REF[1:0]位编程使参考电压与物理电压匹配。使用低噪声的精密电压基准,在测量带宽内最佳小于0.5 μVRMS。

下图给出了一个简化的参考输入电路。与模拟输入类似,参考输入由ESD二极管保护。如果参考输入低于AVSS - 0.3 V或高于AVDD1 + 0.3 V,则保护二极管可以导通。如果这些条件是可能的,使用外部箝位二极管,串联电阻,或两者兼而有之,以限制参考输入电流到规定值。

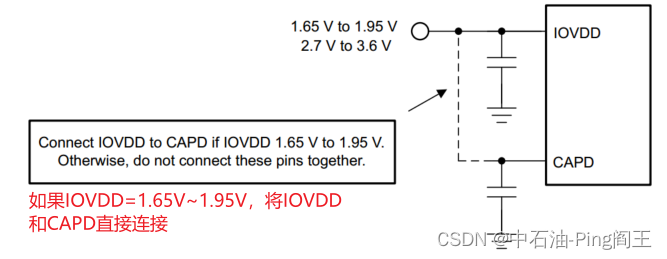

1.2.4 IOVDD电源

IOVDD数字电源工作在两个电压范围:1.65 V至1.95 V和2.7 V至3.6 V。如果IOVDD工作在1.65 v ~ 1.95 v范围内,请将IOVDD直接连接到CAPD引脚上。当IOVDD工作在1.65 v ~ 1.95 v范围时,接线方式如下图所示。否则,如果工作在2.7 v ~ 3.6 v范围内的IOVDD,不要将连接在一起。

1.2.5 调制器

调制器采用多比特delta-sigma架构,具有低功耗和出色的动态范围性能,频谱中的杂散音水平非常低。调制器将内部量化器的量化噪声塑造为带外频率范围,在该频率范围内噪声被数字滤波器去除。留在通带区域内的噪声是密度恒定的热噪声(白噪声)。通带内的综合噪声由数字滤波器OSR决定。

1.2.6 数字滤波器

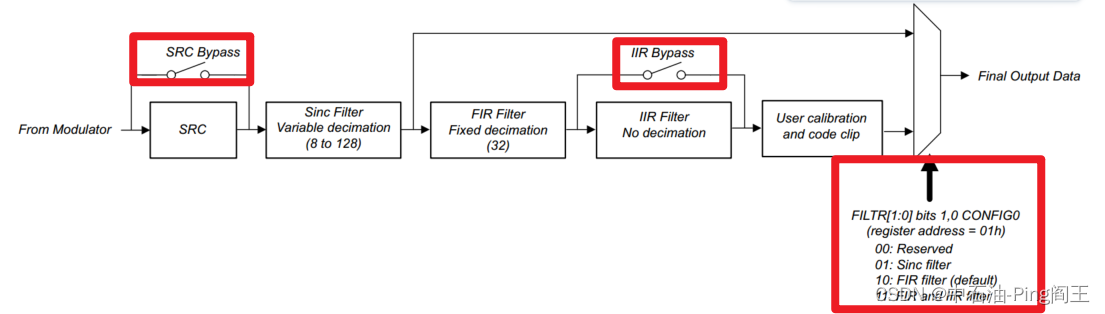

数字滤波器对调制器数据进行抽取和滤波以提供高分辨率输出数据。通过调整通过OSR的滤波量,可以在总噪声和带宽之间进行权衡。提高OSR降低了总噪声,同时降低了信号带宽。如下图所示,采样率转换器(SRC)在输入到数字滤波器块之前从调制器接收数据。

数字滤波器由三部分组成:可变抽取正弦滤波器;可变系数、固定抽取FIR滤波器;和一个可编程高通滤波器(IIR)。所需的滤波器路径由CONFIG0寄存器的**filter[1:0]**位选择。

sinc滤波器提供部分滤波的数据,绕过FIR和HPF滤波器和用户校准。

对于完全过滤的数据,选择FIR过滤器选项

IIR滤波器级去除直流和低频数据

FIR和组合FIR + IIR滤波器被路由到用户校准块和输出代码裁剪块。

具体的滤波器介绍,我就不写了(菜鸡一个,信号与系统没学好,有点看不明白)。

1.2.8 时钟输入

操作需要时钟信号(从时序图可以看出,与SCLK,即SPI的时钟信号区别开来)。时钟信号应用于CLK引脚,fCLK = 8.192 MHz用于高功率和中功率模式,4.096 MHz用于低功率模式。与许多精度数据转换器一样,需要低抖动时钟来实现数据表性能。避免使用rc时钟振荡器(我们使用TI推荐的8.092MHz有源晶振)。建议使用水晶时钟源。为了避免时钟信号振铃,可以在到源端的时钟PCB线路中放置一个串联电阻。时钟信号走线应远离其他时钟信号、输入引脚和模拟组件。

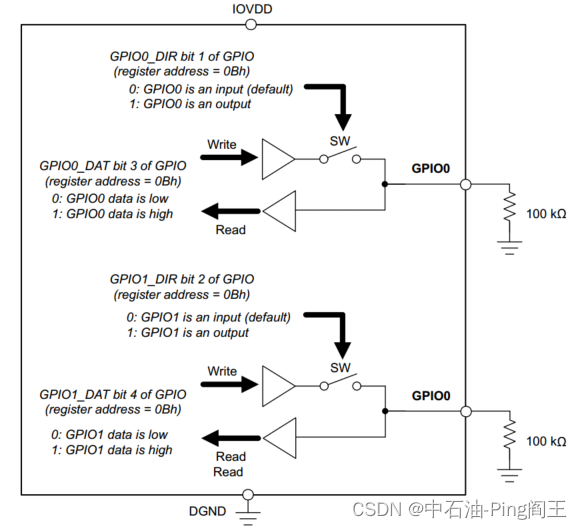

1.2.9 GPIO

ADC提供两个通用I/O (GPIO)引脚,可用作数字输入或输出。GPIO电压等级为IOVDD和DGND。GPIO模块示意图如下图所示。

通过GPIO寄存器对GPIO进行编程。gpio被编程为GPIOx_DIR位的输入或输出。GPIO状态通过GPIOx_DAT位进行读写。当作为输出编程时,读取GPIOx_DAT位返回先前写入的寄存器位值。如果gpio未使用,请使用下拉电阻终止gpio,以防止引脚浮动。

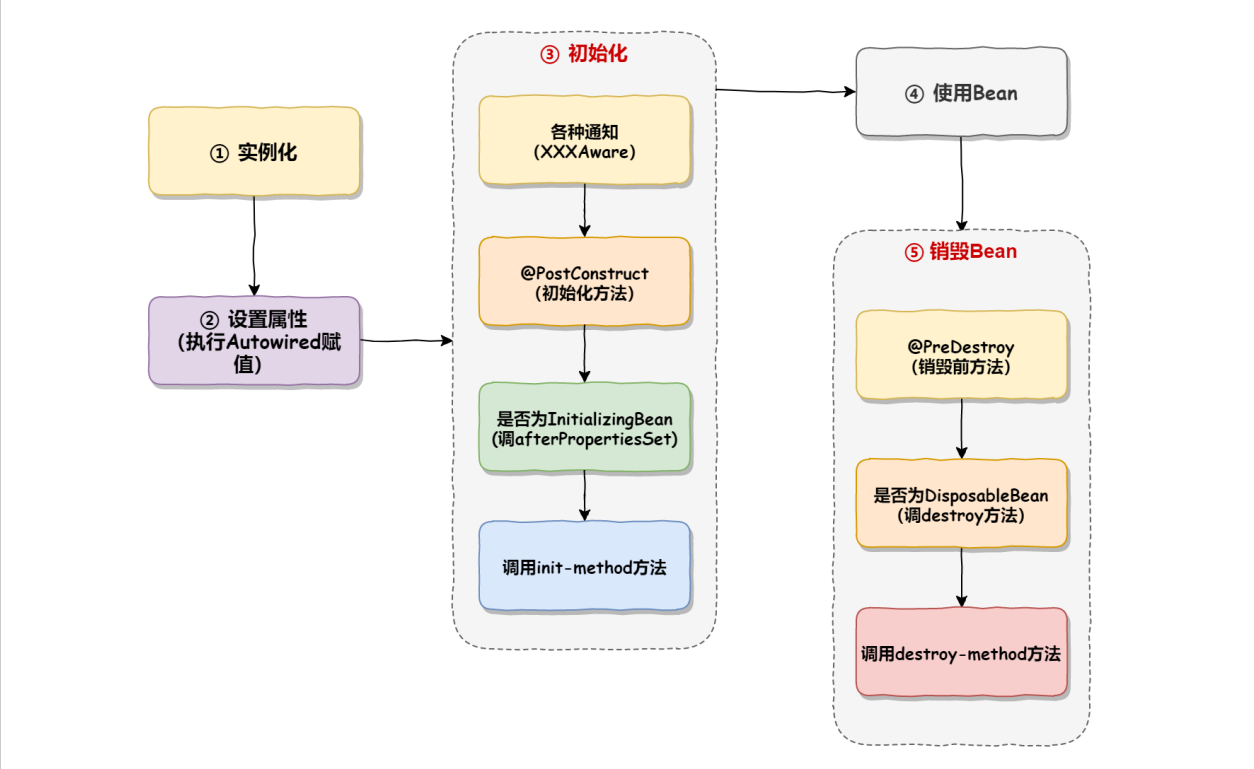

1.3 芯片功能模式介绍

1.3.1断电模式

通过将PWDN引脚设为低电平或通过发送STANDBY命令的软件控制来进行断电。如果需要退出断电模式,可以将PWDN调高或发送WAKEUP命令退出软件断电(时钟运行)。断电使模拟电路失效;然而,数字LDO (CAPD引脚)仍然偏置,从IOVDD提取小偏置电流。相比之下,软件断电会产生更大的IOVDD偏置电流。在两种断电模式下,数字输出的交流信号停止,但保持高或低驱动。数字输入不能浮动;否则,漏电流会从IOVDD电源流出。如果断电时时钟被打断,则复位ADC。断电时同步丢失;因此需要同步ADC。

1.3.2 复位

ADC有三种复位方法:上电复位(POR)、reset引脚或reset命令。

通过引脚复位ADC,驱动reset低电平至少两个fCLK周期,然后返回高电平进行复位。

通过命令复位,在复位命令的SCLK上升沿第8条之后的下一个fCLK上升沿生效。在重置时,过滤器将重新启动,寄存器将重置为默认值。

1.3.3 同步

通过SYNC引脚或SYNC命令对ADC进行同步,从而重新启动数字滤波器周期。在CLK的下降沿上同步后,引脚的同步发生在CLK的下一个上升沿上。SYNC命令的同步发生在CLK的上升沿,在该命令的第8位之后。

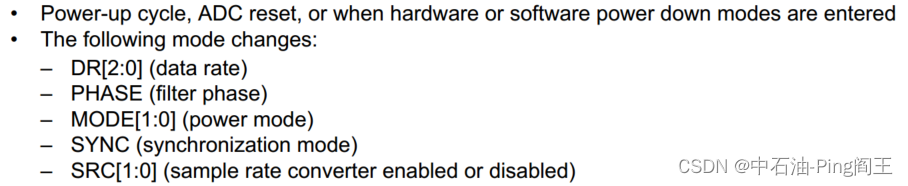

以下情况会导致同步丢失:

同步控制方式有脉冲同步和连续同步两种。同步模式由ID/SYNC寄存器的SYNC位编程。

1.3.3.1 脉冲同步

脉冲同步模式无条件在SYNC上升沿进行同步。当同步时,内部过滤器内存复位,DRDY变高,过滤器周期重新开始。之后的63个DRDY周期被禁用,以允许数字滤波器进行设置。当转换数据准备好时,DRDY断言为低。

1.3.3.2 连续同步

连续同步模式提供了接受连续时钟信号到同步引脚的选项。ADC将SYNC时钟信号的周期与DRDY信号的N个周期进行比较,以确定是否可以重新同步。最初,第一个SYNC正边同步ADC。只有当SYNC的上升沿在N多个DRDY周期之间的时间间隔相差至少±1个fCLK周期时,才会发生重新同步,其中N = 1,2,3…否则,SYNC时钟周期与已经存在的DRDY脉冲处于同步状态,不会发生重同步。注意,当采样率转换器启用时,不能使用连续同步模式。

同步完成后,DRDY继续脉冲;然而,数据保持低63个数据周期,以允许数字滤波器设置。由于数字滤波器的初始延迟,同步输入信号和DRDY脉冲表现出偏移时间。偏移时间是数据速率的函数。

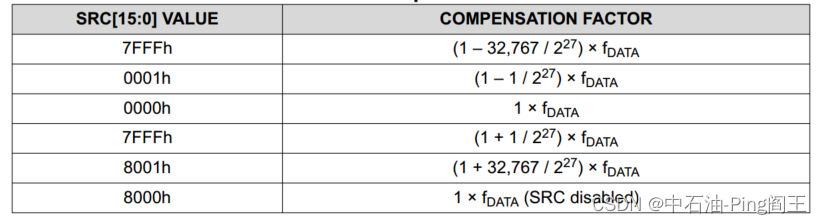

1.3.4 采样率转换器

采样率转换器(SRC)通过对调制器数据以写入SRC寄存器的补偿因子设定的新速率重新采样来补偿时钟频率误差。频率补偿范围为±244 ppm,分辨率为7.45 ppb(1 / 227)。时钟频率误差通过向SCR0和SRC1寄存器写入一个值来补偿。寄存器值为2补码格式,用于正负频率误差补偿。正寄存器数据值降低数据速率频率(增加周期)。新的数据速率频率由DRDY信号的频率观测到。

8000h禁用采样率转换器。0000h使数据不加补偿地通过,但在同步输入到DRDY脉冲的时间延迟上增加了8 / fCLK延迟。

注意:!!!在启用或禁用采样率转换器后重新同步ADC!!!

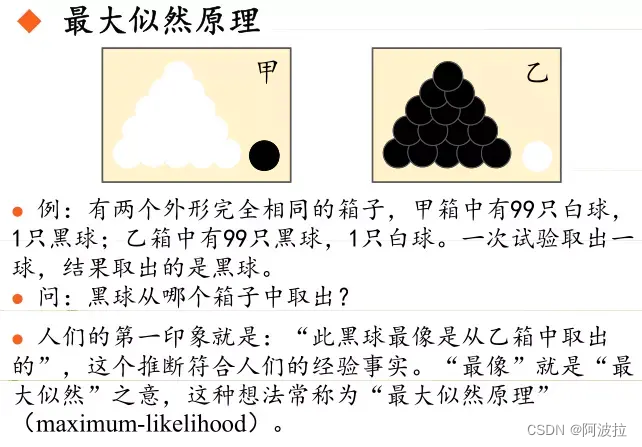

1.3.5 偏移和增益校准

ADC集成了校准寄存器来校正偏移和增益误差。如下图所示,从滤波器数据中减去24位偏移量(offset[23:0]),然后乘以24位增益值(gain[23:0]),再除以400000h。数据被裁剪为32位以产生最终输出。当高通滤波器(IIR)启用时,偏移操作被绕过。

1.3.5.1 偏移寄存器

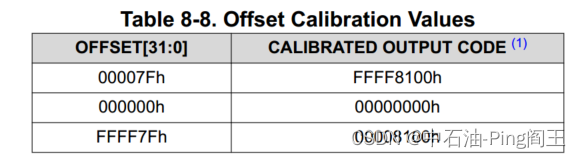

偏移量校正是由一个24位字组成的三个8位寄存器(高地址是MSB)。偏移值左对齐以与32位数据对齐。偏移值为2补码,最大正值为7FFFFFh,最大负值800000h。从转换数据中减去OFFSET,如下表所示。偏置误差通过带输入短多路复用器选项的偏置校准命令或通过收集短输入ADC数据并将值写入寄存器来纠正。虽然偏置校正范围从-FS到+FS,但偏置和增益校正的总和不得超过未校准范围的106%。

当高通滤波器被启用时,偏移校正被禁用。偏移值被用作起始值,以缩短高通滤波器的设置时间。要重新加载偏移值到HPF,请禁用并重新启用高通滤波器。

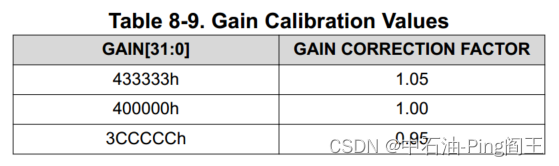

1.3.5.2 增益寄存器

增益校正是通过一个24位字,由三个8位寄存器(高地址= MSB)组成。增益值为24位,用连续二进制编码,对于gain[23:0],归一化为1.0,等于400000h。应用校准信号后,通过增益校准命令或通过收集ADC数据并将计算值写入增益寄存器来校准增益误差。下表列出了GAIN[23:0]寄存器值的示例。

虽然增益值的范围可以大于或小于1,但偏置和增益校正的总和不得超过未校准范围的106%(即不超过1.06)。

1.3.5.2 校准过程

可以使用ADC校准命令或手动校准来执行ADC校准:

- 选择PGA或缓冲操作,输入通道和PGA增益条件进行校准

- 预置OFFSET寄存器= 000000h和GAIN寄存器= 400000h

- 禁用高通滤波器进行偏移校准。短输入到系统,或使用输入MUX提供短输入。系统级输入短可以产生更精确的校准。输入确定后,发送OFSCAL命令或执行手动校准

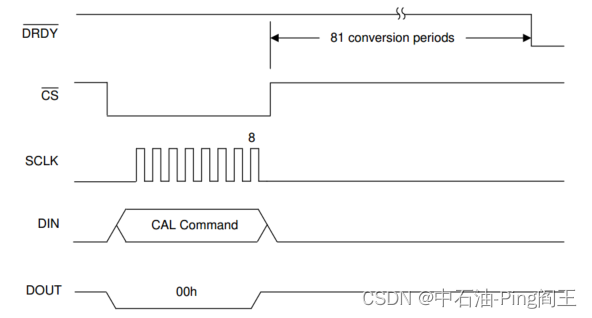

a. OFSCAL命令。命令发出后,DRDY在81个转换周期后被驱动至低电平,表示校准完成。OFFSET寄存器用新的校准值更新。如下图所示,第一个数据输出使用新的OFFSET值

b.手动校准。等待数字滤波器至少64次转换,然后平均一些数据点,以提高校准精度。将该值写入24位OFFSET寄存器 - 施加增益校准电压。输入确定后,发送GANCAL命令或执行手动校准

a. GANCAL命令。施加正直流满量程校准电压。命令发出后,DRDY在81个转换周期后被驱动至低电平,表示校准完成。ADC计算增益,使满量程码等于应用的校准信号。如下图所示,第一个数据输出使用新的“GAIN”值

b.手动校准。对采样率或略低于满量程(例如,增益= 1时为2.4 V)的直流校准信号应用交流相干信号。使用小于满量程的校准信号可防止截断输出代码,否则会导致不正确的校准。等待64转换的数字滤波器解决,然后平均一些数据点,以提高校准精度。对于交流信号校准,使用一些相干信号周期来计算均方根值。

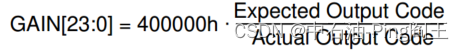

下面的公式用来计算手动校准的增益值。

二、总结

上面的一些介绍有很多是数据手册翻译过来的,然后掺杂一些自己的理解,可能不是很准确,这篇博客基本上已经把芯片的一些功能介绍完毕了,接下来也就是SPI的格式以及Register map的介绍了,这部分会在下一篇博客中进行详细介绍。

三、往期回顾

项目进展(一)-晶振正常输出、焊接驱动芯片、查找芯片手册并学习

项目进展(二)-配置MCT8316ZR芯片,主要学习如何根据数据手册配置外设等

项目进展(三)-电机驱动起来了,发现了很多关键点,也遇到了一些低级错误

项目进展(四)-双电机均可驱动,配置模拟SPI,调平仪功能初步实现!

项目进展(五)-修复PCB电路板,学习32位ADC芯片ADS1285