就像人类容易接受自然数,但对于负数缺乏某种直觉上的认识一样;后仿过程中经常出现的 Negative Delay 和 Negative Timing Check 也非常容易使人困惑。

Warning-[SDFCOM_NICD] Negative INTERCONNECT Delay encountered

今天这篇首先简要分析这些 Negative 们产生的原因,然后看一下 EDA 工具是如何处理它们的。

产生 Negative Delay 的原因

从根本上来说有两种原因。一种是测量的原因,比如输入和输出信号的观测方法不同,导致输出信号反而比输入信号在时间上提前;一种是信号在传输过程中真实发生了某种变化,导致信号跳变的提前。

具体原因大概分下面几种。

Voltage Converting

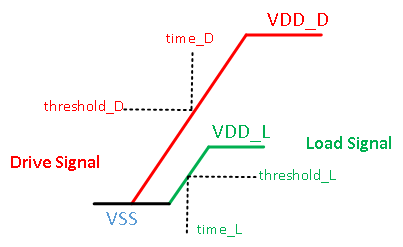

信号在不同电压域之间的转换可能会导致负延时产生,如下图所示。

假设都以 50% VDD 为信号跳变的阈值,那么如果信号从高电压域输出到低电压域,50% VDD 对应的时刻反而会提前,导致负延时的出现。这种极端情况出现的前提是信号的 Transition Time 足够的大,连器件的正延时都不足以抵消电压下降带来的负延时。

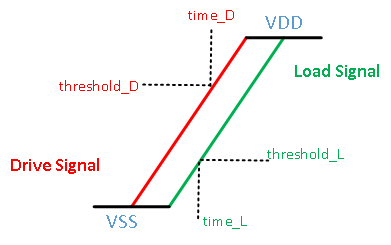

Threshold Converting

阈值转换的原因其实类似于电压转换,如果输出负载的阈值低于该器件的输入阈值,并且信号的 Transition Time 也足够的大,那么从观测者的角度,信号在输出时被观测到逻辑跳变的时刻反而提前于输入跳变的时刻。

Noise

信号在传输过程中难免受到一些干扰,如果这种干扰来自于相邻的器件或者走线,就称之为串扰(crosstalk)。串扰可能造成信号传输的滞后或者提前。

造成提前的情形如下图所示。

红色实线表示输入信号;绿色虚线是没有串扰的输出信号,如果在这个输出信号跳变之前有个串扰发生(黑色实线),会在输出上产生一个很短的高脉冲(绿色实线),和原本的输出信号合起来看,就相当于输出信号的跳变提前了。如果这个提前量足够大,就相当于该器件有了一个负延时。

Calculation

还有一些负延时来自于 EDA 工具特定算法的计算过程。比如时序模型做数值计算过程中引入的误差;针对 stage delta delay 和 net delay 分别做 derating 可能引入的负值。这些理解起来不那么浅显,就不做详细的解释了。

EDA 工具如何处理 Negative Delay

这个问题有点复杂,因为各家 EDA 公司的仿真器都有不同的算法来解决。

从直观的角度来考虑,一个负延时总归是要结合其相邻的器件延时、线延时来解决的,用整体更大的正延时来抵消局部的负延时。

有些仿真器干脆做简化处理,把从 SDF 中读取的负延时直接变为零延时。这种做法无可厚非,是符合 Verilog 和 SDF 标准的。

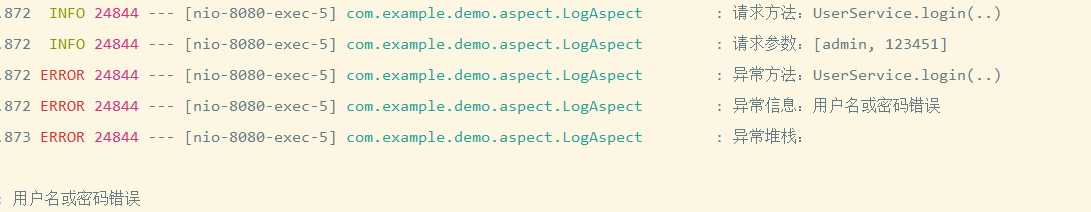

打开 VCS 仿真器的负延时特性,就是在编译时加上-negdelay选项。

另外,PT 写出 SDF 时是默认带有 Negative Delay 和 Negative Timing Check 的,如果不想写出这些负值,需要加上如下的特定选项,这时 PT 会自动把相关负值都变成零。

pt_shell> write_sdf -no_negative_delays {timing_checks | cell_delays | net_delays} postsim.sdf

产生 Negative Timing Check 的原因

Negative Timing Check 中的 Negative 其实和 Negative Delay 中的 Negative 不太一样,前者只是描述器件时序特性参数时规定的一种算术表达形式。

Positive Setup/Hold Timing Check

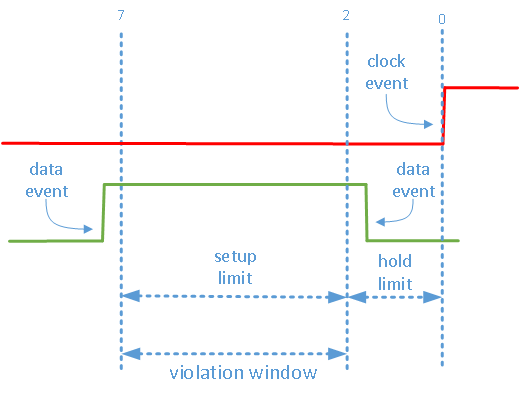

先看一个常见的 Setup Limit 和 Hold Limit 都为正值的例子。

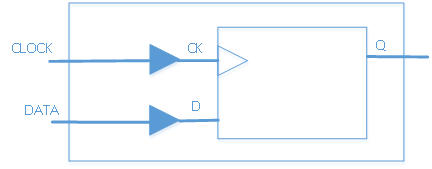

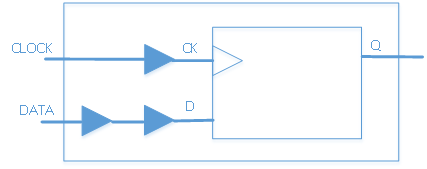

下图是一个标准单元 D 触发器的框图,我们接下来所讨论的时序检查都是相对于最外层框图所对应的管脚。

仿真模型中用来检查时序的语句如下,其中的 Setup Limit 和 Hold Limit 的具体数值都是从 SDF 文件取出后反向标注到网表的。

$setuphold (posedge clock, data, 2, 3, notifyreg);

这种语法模式下,Clock Event 的时刻规定为 0 时刻;Data Event for Setup Check要早于 Clock Event;Data Event for Hold Check 要晚于 Clock Event;符合这种一般情况的时序参数,包括 Setup Limit 和 Hold Limit 都用正值来表示。

但是标准单元内部因为一些特殊的设计,会造成 Clock 和 Data 到达内部真正的时序器件的延时不同,这样从外部来看,时序参数会有一些不同的情况。

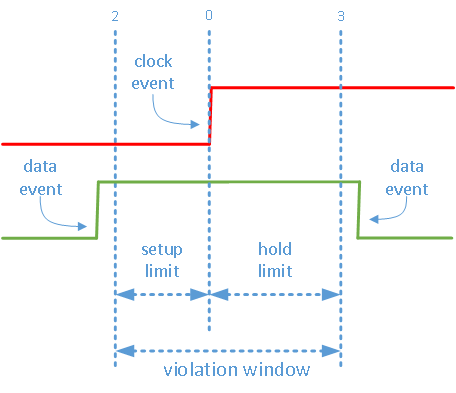

Negative Setup Limit

从下面的示意图可以看出,Negative Setup Limit 的产生主要是因为标准单元内部 Clock 上的延时相对较大,从外部来看,Data Event for Setup Check 就可以晚一些来,如果晚于 Clock Event(时刻为 0),就用负值来表示(和早于的情况相反)。

$setuphold (posedge clock, data, -2, 7, notifyreg);

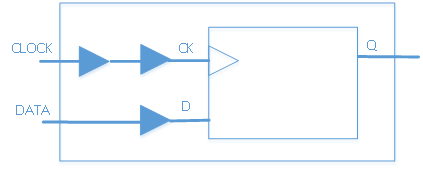

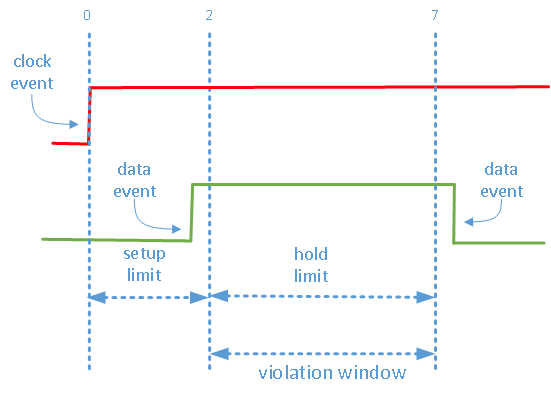

Negative Hold Limit

从下面的示意图可以看出,Negative Hold Limit 的产生主要是因为标准单元内部 Data 上的延时相对较大,从外部来看,Data Event for Hold Check 就必须早一些来,如果早于 Clock Event(时刻为 0),就用负值来表示(和晚于的情况相反)。

$setuphold (posedge clock, data, 7, -2, notifyreg);

EDA 工具对于 Negative Timing Check 的支持

当时序参数存在负值的情况时,必须要用 $setuphold 以及 $recrem 来表示;而不能用单独的 $setup,$hold,$recovery,$removal。具体语法如下。

$setuphold(reference_event, data_event, setup_limit,

hold_limit, notifier, [timestamp_cond, timecheck_cond,

delayed_reference_signal, delayed_data_signal]);

$recrem(reference_event, data_event, recovery_limit,

removal_limit, notifier, [timestamp_cond, timecheck_cond,

delayed_reference_signal, delayed_data_signal]);

并且从 STA 工具写出 SDF 文件的时候,需要设置恰当的选项,来支持这种标注语法。例如:

pt_shell> write_sdf -version 3.0 -include {SETUPHOLD RECREM} postsim.sdf

同样,在调用仿真器的时候,例如 VCS,需要加上 +neg_tchk 的编译选项来支持 Negative Timing Check 的动态仿真。