SPI协议详解

- 前言

- 一、SPI简介

- 二、接口

- 三、SPI总线个特点:

- (一)主从模式

- (二)同步传输

- (三)全双工串行通信(数据传输高位在前,低位在后)

- 四、SPI总线传输的4种模式

- (一)SPI总线的极性

- (二)SPI总线的相位

- (三)四种模式

- 1.模式0 (CPOL=0; CPHA=0)

- 1.模式1 (CPOL=0; CPHA=1)

- 2.模式2 (CPOL=1; CPHA=0)

- 3.模式3 (CPOL=1; CPHA=1)

- 五、关于提高传输速率

- (一)标准SPI–三线SPI

- (二)Dual SPI–四线SPI

- (三)Quad SPI–六线

- 参考链接

前言

前面有学过SPI读写flash,这里再梳理总结一下。

一、SPI简介

SPI(Serial Peripheral Interface,串行外围设备接口),是Motorola公司提出的一种同步串行接口技术,是一种高速、全双工、同步通信总线,在芯片中只占用四根管脚用来控制及数据传输,广泛用于EEPROM、Flash、RTC(实时时钟)、ADC(数模转换器)、DSP(数字信号处理器)以及数字信号解码器上。SPI通信的速度很容易达到好几兆bps,所以可以用SPI总线传输一些未压缩的音频以及压缩的视频。

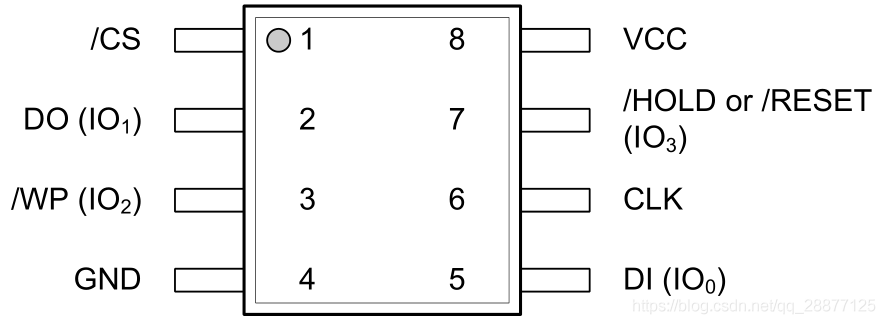

二、接口

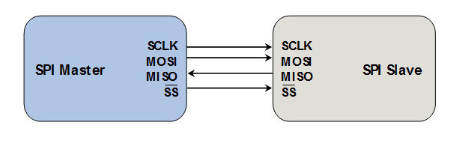

下图是只有2个chip利用SPI总线进行通信的结构图

可知SPI总线传输只需要4根线就能完成,这四根线的作用分别如下:

- SCK(Serial Clock):SCK是串行时钟线,作用是Master向Slave传输时钟信号,控制数据交换的时机和速率;

- MOSI(Master Out Slave in):在SPI Master上也被称为Tx-channel,作用是SPI主机给SPI从机发送数据;

- CS/SS(Chip Select/Slave Select):作用是SPI Master选择与哪一个SPI Slave通信,低电平表示从机被选中(低电平有效);

- MISO(Master In Slave Out):在SPI Master上也被称为Rx-channel,作用是SPI主机接收SPI从机传输过来的数据;

三、SPI总线个特点:

(一)主从模式

采用主从模式(Master-Slave)的控制方式,支持单Master多Slave。SPI规定了两个SPI设备之间通信必须由主设备Master来控制从设备Slave。也就是说,如果FPGA是主机的情况下,不管是FPGA给芯片发送数据还是从芯片中接收数据,写Verilog逻辑的时候片选信号CS与串行时钟信号SCK必须由FPGA来产生。同时一个Master可以设置多个片选(Chip Select)来控制多个Slave。SPI协议还规定Slave设备的clock由Master通过SCK管脚提供给Slave,Slave本身不能产生或控制clock,没有clock则Slave不能正常工作。单Master多Slave的典型结构如下图所示

(二)同步传输

SPI总线在传输数据的同时也传输了时钟信号,所以SPI协议是一种同步(Synchronous)传输协议。Master会根据将要交换的数据产生相应的时钟脉冲,组成时钟信号,时钟信号通过时钟极性(CPOL)和时钟相位(CPHA)控制两个SPI设备何时交换数据以及何时对接收数据进行采样,保证数据在两个设备之间是同步传输的。

(三)全双工串行通信(数据传输高位在前,低位在后)

SPI总线协议是一种全双工的串行通信协议,数据传输时高位在前,低位在后。SPI协议规定一个SPI设备不能在数据通信过程中仅仅充当一个发送者(Transmitter)或者接受者(Receiver)。在片选信号CS为0的情况下,每个clock周期内,SPI设备都会发送并接收1 bit数据,相当于有1 bit数据被交换了。数据传输高位在前,低位在后(MSB first)。SPI主从结构内部数据传输示意图如下图所示

四、SPI总线传输的4种模式

在芯片的资料上,有两个非常特殊的寄存器配置位,分别是 CPOL (Clock POlarity)和 CPHA (Clock PHAse)。

- CPOL配置SPI总线的极性

- CPHA配置SPI总线的相位

(一)SPI总线的极性

极性 会直接影响SPI总线空闲时的时钟信号是高电平还是低电平

- CPOL = 1:表示空闲时是高电平

- CPOL = 0:表示空闲时是低电平\

由于数据传输往往是从跳变沿开始的,也就表示开始传输数据的时候,是下降沿还是上升沿。

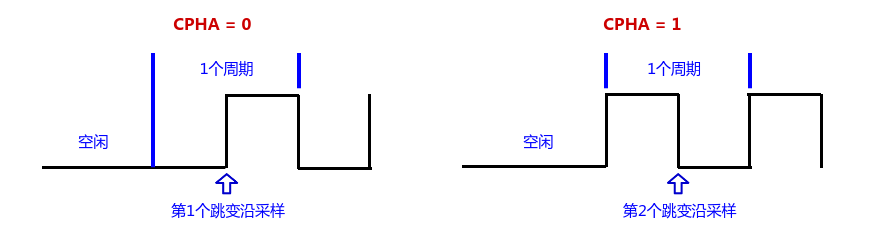

(二)SPI总线的相位

一个时钟周期会有2个跳变沿。而相位,直接决定SPI总线从那个跳变沿开始采样数据。

- CPHA = 0:表示从第一个跳变沿开始采样

- CPHA = 1:表示从第二个跳变沿开始采样

至于跳变沿究竟是上升沿还是下降沿,这取决于 CPOL。记住, CPHA 只决定是哪个跳变沿采样。

(三)四种模式

CPOL 和 CPHA 的不同组合,形成了SPI总线的不同模式。

| mode | CPOL | CPHA |

|---|---|---|

| mode | 0 | 0 |

| mode | 1 | 0 |

| mode | 2 | 1 |

| mode | 3 | 1 |

1.模式0 (CPOL=0; CPHA=0)

- CPOL = 0:空闲时是低电平,第1个跳变沿是上升沿,第2个跳变沿是下降沿

- CPHA = 0:数据在第2个跳变沿(下降沿)采样

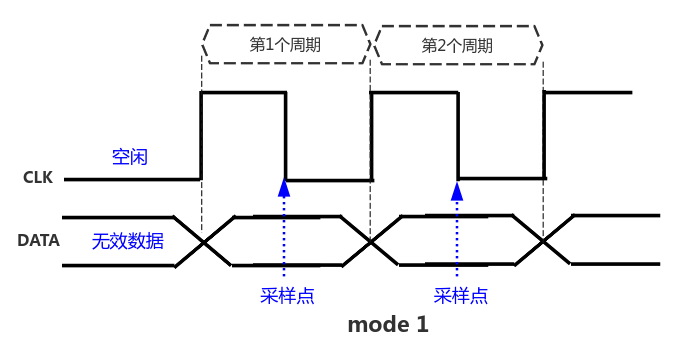

1.模式1 (CPOL=0; CPHA=1)

- CPOL = 0:空闲时是高电平,第1个跳变沿是下降沿,第2个跳变沿是上升沿

- CPHA = 1:数据在第1个跳变沿(下降沿)采样

2.模式2 (CPOL=1; CPHA=0)

- CPOL = 1:空闲时是高电平,第1个跳变沿是下降沿,第2个跳变沿是上升沿

- CPHA = 0:数据在第2个跳变沿(上升沿)采样

3.模式3 (CPOL=1; CPHA=1)

- CPOL = 1:空闲时是高电平,第1个跳变沿是下降沿,第2个跳变沿是上升沿

- CPHA = 1:数据在第2个跳变沿(上升沿)采样

五、关于提高传输速率

从spi flash里面读数据的时候,常规操作(也是必不可少的)是使用到了VCC,GND,CS,CLK,DO这些引脚,这没得说,在这个组合里面只有DO这个引脚是数据线,也就是说一个时钟沿只能传输一个位的数据; 如何在时钟频率不变的情况下提高传输速度呢?

一般来说,nor flash是SOP-8封装,有8个引脚:

| 名称 | 介绍 |

|---|---|

| VCC | 电源正 |

| GND | 电源地 |

| CS | 传输控制–片选 |

| CLK | 传输控制–时钟 |

| MOSI | 可以复用 |

| MISO | 可以复用 |

| WP | 可以复用 |

| HOLD | 可以复用 |

除了电源引脚(VCC,GND)以及控制传输的CS、CLK不能复用外,其他的四个引脚都是可以复用为数据传输引脚的。这里设定的场景是单向通信(比如只读的操作中,只写的操作中),并非双工通信。

(一)标准SPI–三线SPI

标准SPI通常就称SPI,它是一种串行外设接口规范,有4根引脚信号:clk , cs, mosi, miso

一个时钟周期发送1个bit

(二)Dual SPI–四线SPI

它只是针对SPI Flash而言,不是针对所有SPI外设。对于SPI Flash,全双工并不常用,因此扩展了mosi和miso的用法,让它们工作在半双工,用以加倍数据传输。也就是对于Dual SPI Flash,可以发送一个命令字节进入dual mode,这样mosi变成SIO0(serial io 0),mosi变成SIO1(serial io 1),这样一个时钟周期内就能传输2个bit数据,加倍了数据传输

四根线:CS、CLK、SIO1、SIO2

一个时钟周期发送2个bit

(三)Quad SPI–六线

与Dual SPI类似,也是针对SPI Flash,Qual SPI Flash增加了两根I/O线(SIO2,SIO3),目的是一个时钟内传输4个bit。

六根线:CS、CLK、SIO1、SIO2、SIO3、SIO3

一个时钟周期发送4个bit

所以对于SPI Flash,有标准spi flash,dual spi , qual spi 三种类型,分别对应3-wire, 4-wire, 6-wire,在相同clock下,线数越多,传输速率越高。

参考链接

4、SPI总线的原理与Verilog实现

SPI总线传输的4种模式

SPI协议_Verilog实现

嵌入式–Flash操作中的标准SPI,Dual SPI,Quad SPI

![[附源码]计算机毕业设计Python贵港高铁站志愿者服务平台(程序+源码+LW文档)](https://img-blog.csdnimg.cn/6c37b894c26b44028fb8c8627dee4848.png)

![[附源码]Nodejs计算机毕业设计江西婺源旅游文化推广系统Express(程序+LW)](https://img-blog.csdnimg.cn/c7fc02a05e294ea3bf22c62dcc3fd35f.png)