文章目录

- 一、基础概念

- 1.1 DMA---Direct Memory Access 直接存储器访问,目的减少CPU资源占用

- 二、典型DMA硬件模型

- 2.1 基本硬件特性---通道数、源/目标类型,地址与累加方式,数据位宽,搬移长度,循环模式,中断

- 2.2 提升硬件利用率的链表模式(部分芯片支持)

- 三、典型DMA软件驱动方案

- 内存+DMA搬移(待补充)

- CRC+DMA模式(待补充)

- 串口+DMA模式(待补充)

- I2C+DMA模式(待补充)

- DMA软件方案总结(待补充)

- 四、DMA注意事项(待补充)

- DMA与Cache一致性(待补充)

一、基础概念

1.1 DMA—Direct Memory Access 直接存储器访问,目的减少CPU资源占用

DMA是用于在外设与存储器之间以及存储器与存储器之间提供高速数据传 输。可以在无需任何CPU操作的情况下通过DMA快速移动数据。目的是节省的 CPU 资源,可供其它操作使用。CPU资源用于重复性的内存搬移 或者 从低速外设接口查询获取非连续数据 利用率是不高的。

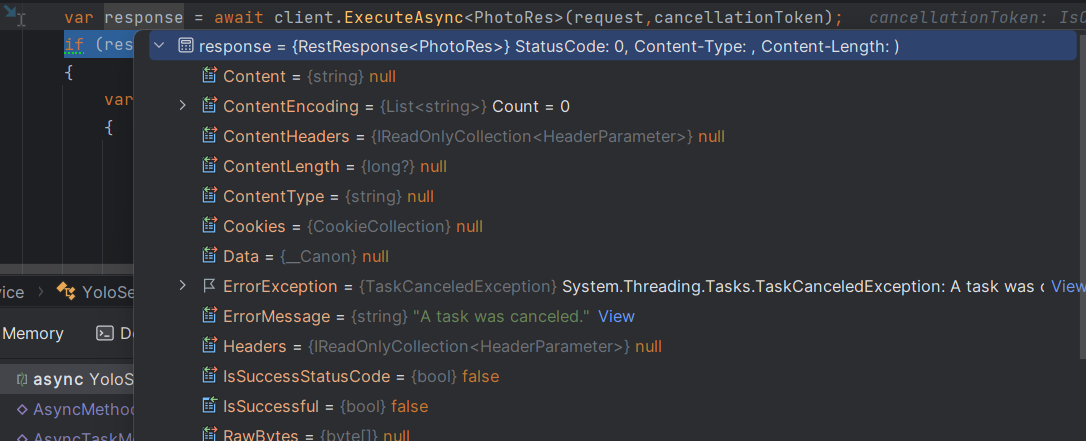

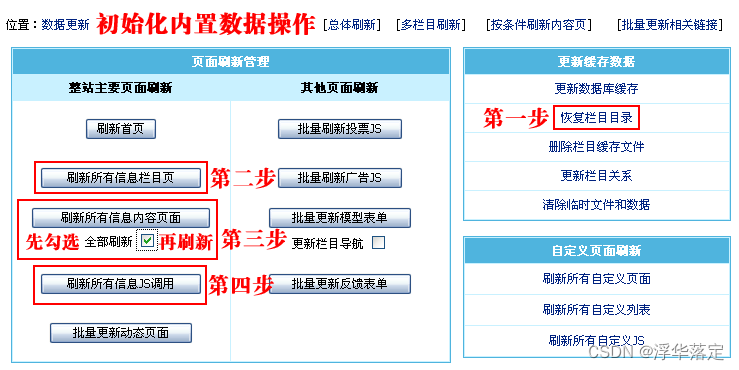

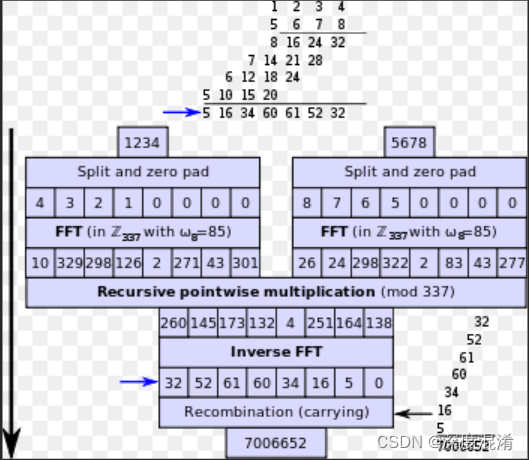

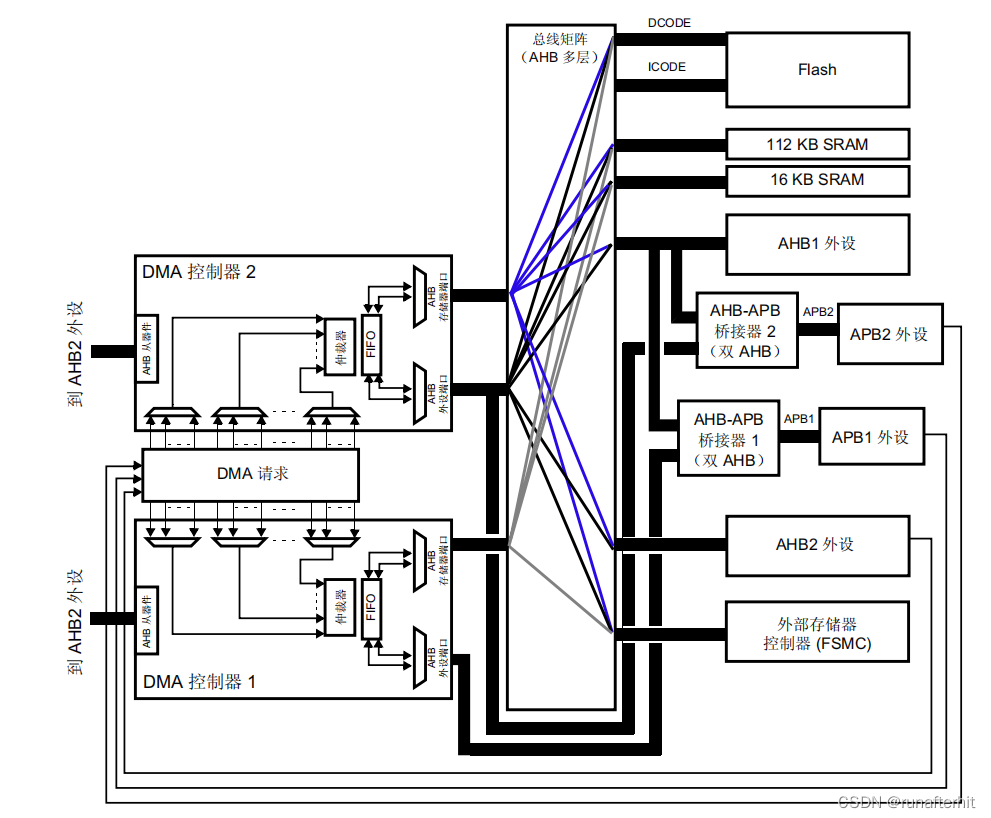

举例某块STM32的DMA数据链路:

二、典型DMA硬件模型

2.1 基本硬件特性—通道数、源/目标类型,地址与累加方式,数据位宽,搬移长度,循环模式,中断

我们拿到模块带DMA控制器的芯片如SOC之后,通常需要DMA硬件模型特性如下:

1、有几个DMA通道:决定了可以同时传输数据的数量。如A通道搬移串口数据同时,B通道搬移内存数据;

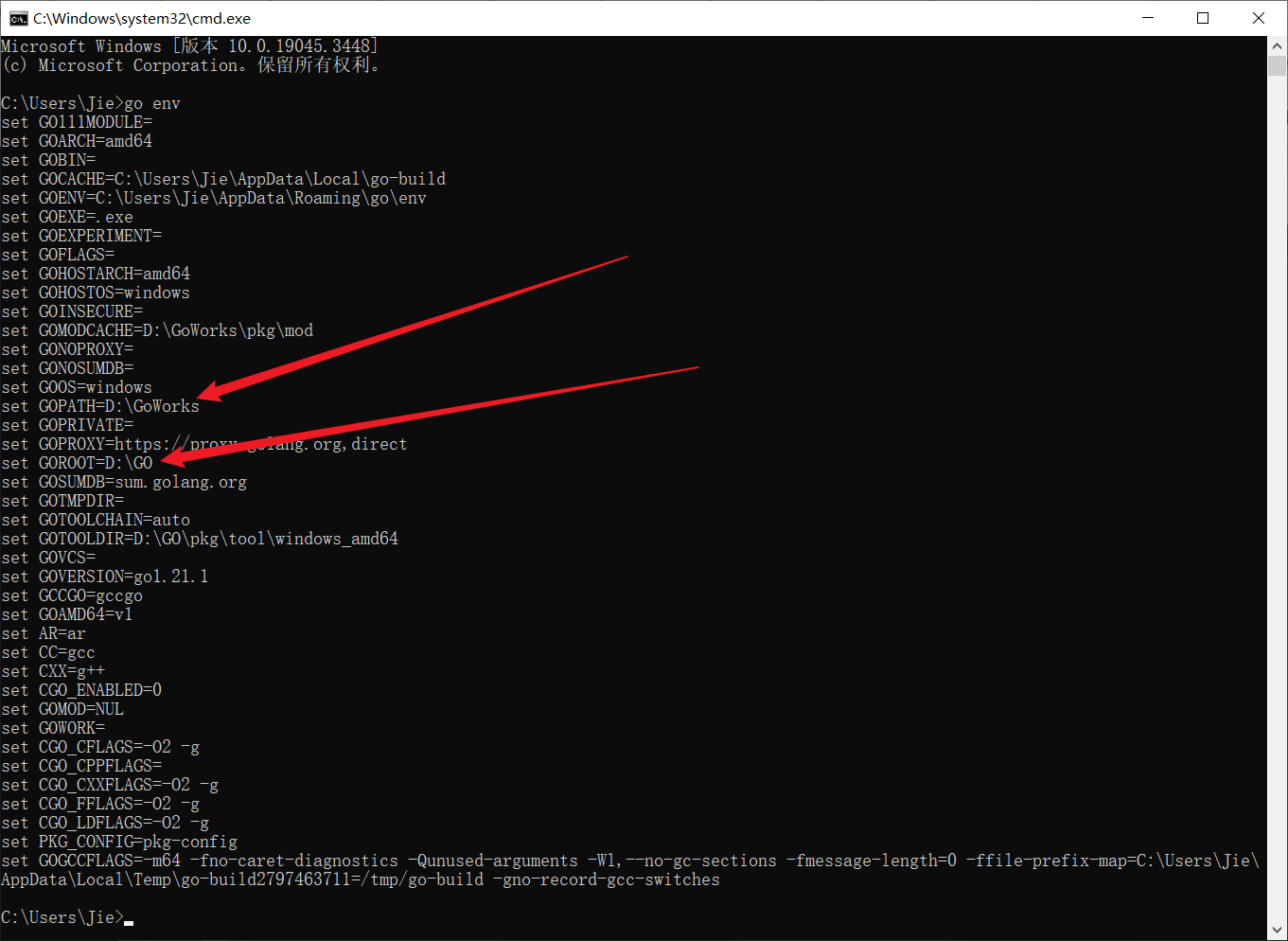

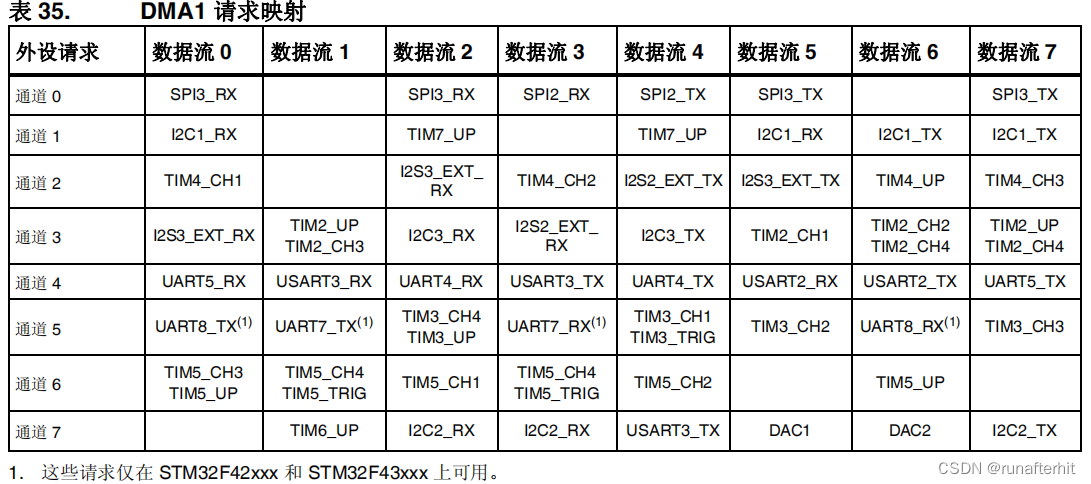

2、源/目标支持类型:不同通道支持的源类型和目标类型是有差异的,典型外设有SPI、UART、I2C、ADC、CRC、等,因此要做好规划,举例某款STM32芯片DMA类型支持如下:

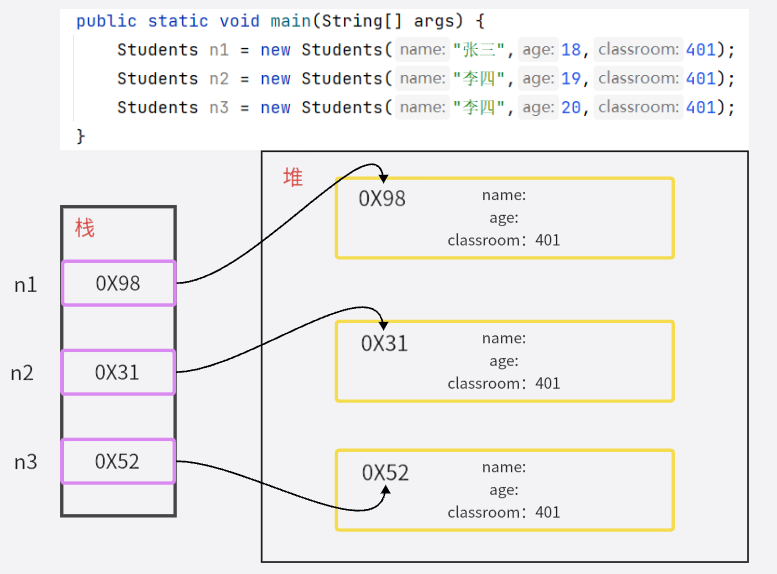

3、地址与累加方式:源和目标在设置地址的同时,也需要设置地址指针偏移方式,比如内存搬移时 就需要递增,而一些外设比如Uart、CRC控制器等在访问时都是访问的逻辑FIFO寄存器地址,往往不会变化一直都是同一个地址。

4、访问数据宽度:通常由于不同外设有数据长度访问限制,DMA需要支持独立的源和目标传输宽度(字节、半字、字):源和目标的数据宽度不相等时,DMA 自动 封装/解封必要的传输数据来优化带宽。

5、搬移长度:启动搬移后搬移数据长度,举例如 支持1~65536字节设置,根据实际需求进行设置,如果长度超过最大长度,就需要软件多次配置启动搬移;

6、循环模式:当传输结束时,硬件自动会将传输数据量寄存器进行重装,进行下一轮的数据传输。

7、中断支持:DMA搬移完之后,经常需要通过中断上报事件给CPU,通知做后续行为,DMA控制器通常都支持中断上报(如 传输完成中断、半传输中断、传输错误等)。当然不用中断也可以通过状态寄存器访问硬件当前搬移地址状态和是否搬移完成的判断;

2.2 提升硬件利用率的链表模式(部分芯片支持)

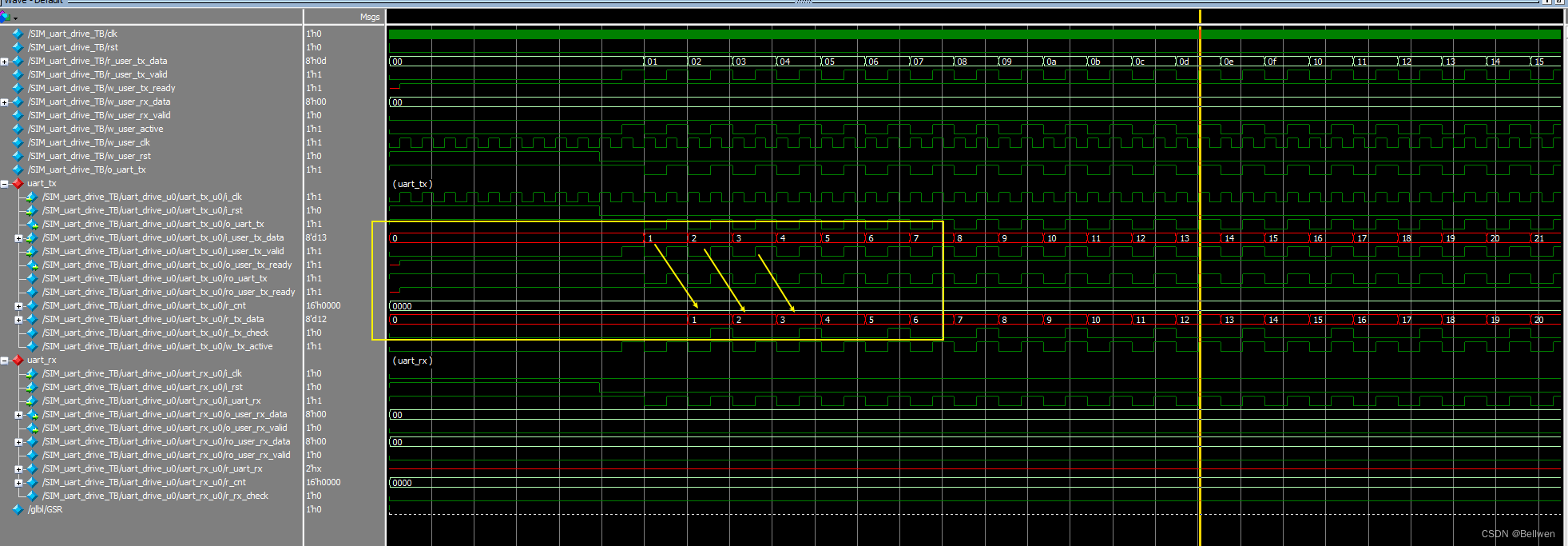

由于DMA单次搬移有长度限制举例64KByte,如果要搬移1MByte的数据,通常是下面两种方式:

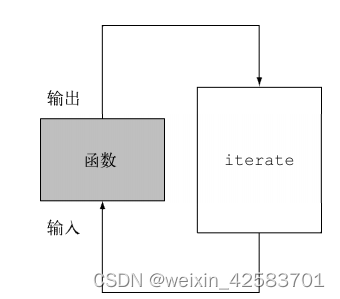

1)非中断的循环查询迭代策略: 先配置第一个64K搬移,然后在轮询调度中不停的查看DMA是否搬移完成,如果搬移完成就配置下一个64K并使能搬移,如此反复。逻辑利用率是最低的,当逻辑搬移完成 要等到下一次 轮询查看到空闲,才开始配置下一次。

2)完成中断迭代策略 相比循环查询方式,这种方式利用每个64K的搬移完成 DMA中断事件,配置启动下一块搬移。逻辑利用率有提高(中断更及时),但是仍然不是100%,从中断唤醒到下次配置之间逻辑仍然是空闲的。

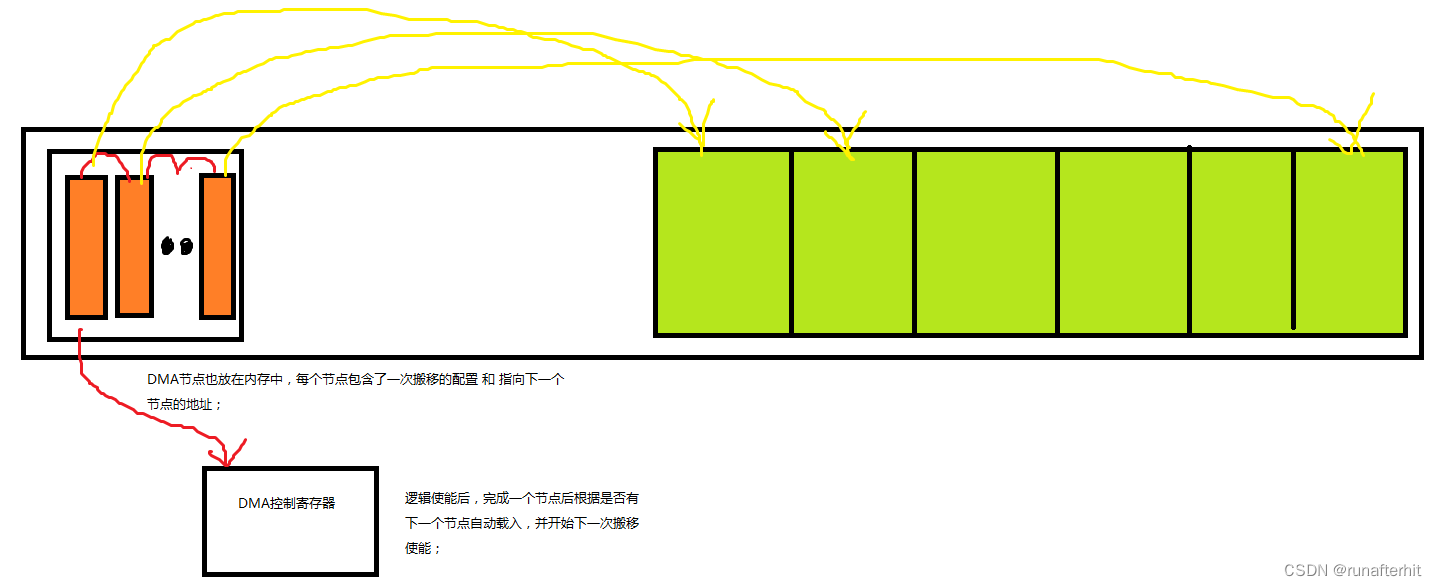

有没有能让硬件DMA利用率到100%的方式呢?部分芯片支持链表模式可以做到。思路如下:

3)、链表模式:此种模式下硬件生效的不是直接寄存器配置,而是一个链表首地址,这个地址指向的内存里面一个固定大小的区域,可以看做一个DMA节点,节点区域包含了 当次搬移 包含的 起始地址、结束地址、搬移长度、数据位宽、是否屏蔽中断等 以及 下一个节点地址(如果配置0就没有下一个节点)。这样就可以把比如1M地址范围,拆分为一个一个节点串成链表,把最后一个节点完成中断打开,前面节点无需使能中断。当逻辑工作起来后,每完成一个节点后自动查找载入下一个节点,到最后一个完成时上报完成中断。

三、典型DMA软件驱动方案

了解完硬件模型,再看一下软件抽象的方案。DMA本身通常不会被业务模块直接访问,作为小系统能力的一部分。单纯的DMA驱动模块,调用者往往 是 内存模块(提供非CPU的内存搬移),串口模块(提供DMA模式传递数据)、CRC模块(提供非CPU的CRC计算)。因此如果是业务模块开发者通常接触较少;