Lattice Diamond关于原语的使用

- 前言

- 一、原语基本概念

- (一)简介

- (二)常用原语

- 1.时钟相关原语

- 2.差分输入/输出原语

- 3.接口相关原语

- 二、Lattice原语

- (一)原语使用

- (二)IP调用

- (三)Diamond帮助文档

- 三、更多使用

- 参考链接

前言

前一期有简单提到原语Lattice系列内存时序的概念,这里重点研究

一、原语基本概念

这里参考Diamond软件的使用(6)–Lattice原语基本概念

(一)简介

原语,英文名称primitive,是FPGA软件集成开发环境所提供的一系列底层逻辑功能单元。

由于是底层逻辑功能单元,所以它们往往跟目标FPGA芯片以及芯片厂商紧密相关,因此不同厂商、不同器件的原语往往不能通用。当编译器对 HDL代码进行编译时,其中间环节的一些输出往往就是由原语组成的逻辑网表。因此,原语往往是不参与综合过程的,而使用原语描述的逻辑往往也不会被综合工具所优化。

例如,Xilinx 公司的ISE软件集成开发环境中的unisims库中定义了所有用于综合的原语,而simprims库中则定义了所有用于实现的原语。需要注意的是,如果在ISE安装目录下的verilog\src\unisims或verilog\src\simprims文件夹中看这些原语的代码,可以发现其实这些并不是真正的原语,而是在原语的基础上又封装了一层,不过人们常常将它们也泛称为原语。

(二)常用原语

1.时钟相关原语

如果时钟信号不是由FPGA芯片的专用时钟pin(或pad)引入FPGA 的,那么它通常就需要在FPGA内部被显式地连接到时钟树资源上,否则,直接使用这种不经过时钟树的时钟信号,会给FPGA设计的时序带来非常麻烦的问题,进而导致逻辑行为失败。

可是HDL代码仅仅描述功能,无法向编译器表达“希望将某一时钟信号连接到时钟树资源”这样的一层意思,那么此时,就需要使用类似BUFG这样的库里提供的底层模块来进行指示。

2.差分输入/输出原语

FPGA的接口具有单端和差分两种形式,同样,HDL代码只能描述功能,无法表达“某两个pin(或pad)脚互为一个差分对”这样的一层意思。那么此时,就需要使用类似IBUFDS、IBUFGDS、OBUFDS这样的库里提供的底层模块或原语来进行指示。

3.接口相关原语

当需要使用接口资源中的寄存器来实现高速数据采集时,除了使用本篇→编程思路→代码中的约束信息→HDL中的常用约束示例→寄存器的相关约束】中介绍的方法外,如果直接调用相关的原语,编译器便会利用接口资源中的寄存器来做事情。例如,使用ODDR,IDDR,IDDR2CLK,ISERDES,OSERDES等原语后﹐编译器便会利用接口资源的寄存器来实现相关接口功能,这样便能达到比较高的性能。

二、Lattice原语

(一)原语使用

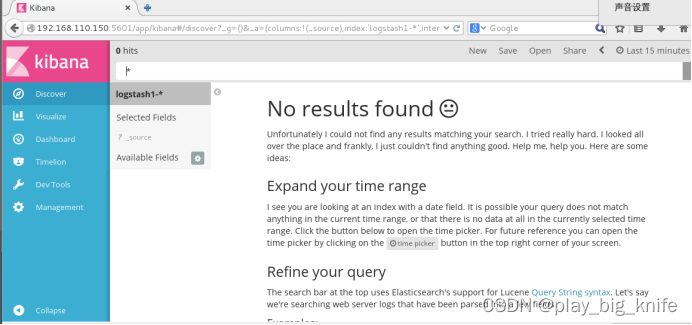

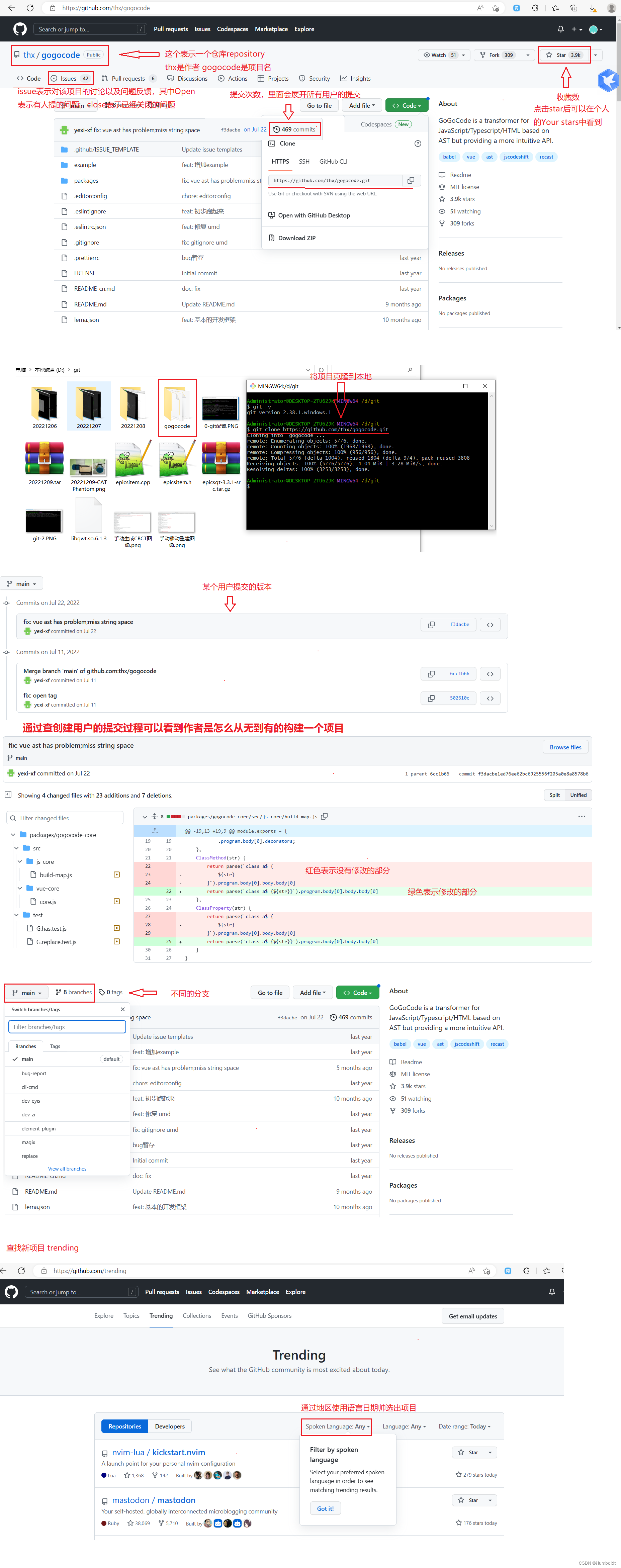

使用LATTICE的原语在设计中使用内存的另一种方法是直接实例化ECP5设备的内存原语,用户必须在EBR

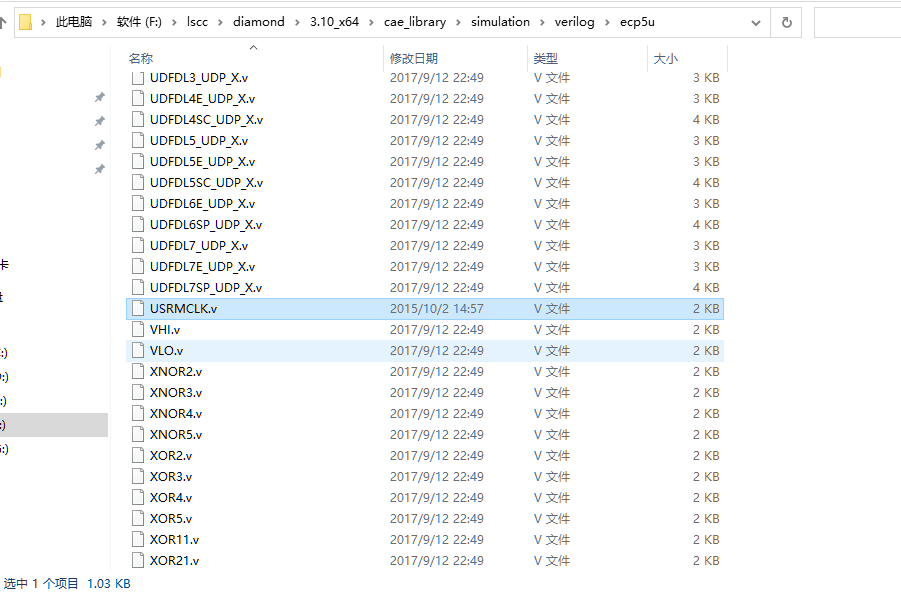

块级别上工作。如果需要具有跨多个模块的内存,则用户需要自己创建级联内存。Lattice 在 Lattice Diamond 软件安装文件夹的 cae_library/synthesis 文件夹下的 VHDL/Verilog 文件中提供了所有原语的详细列表。

例如:在软件Lattice Diamond安装目录下F:\lscc\diamond\3.10_x64\cae_library\simulation\verilog\ecp5u可以看到ecp5u系列的一些Verilog原语。

(二)IP调用

一些IP仿真时会调用原语,例如FIFO,参考Lattice库联合ModelSim仿真FIFO→ 二、库文件添加→(二)方法二:直接添加器件库到Libray,和tb.v在同一个目录下仿真

(三)Diamond帮助文档

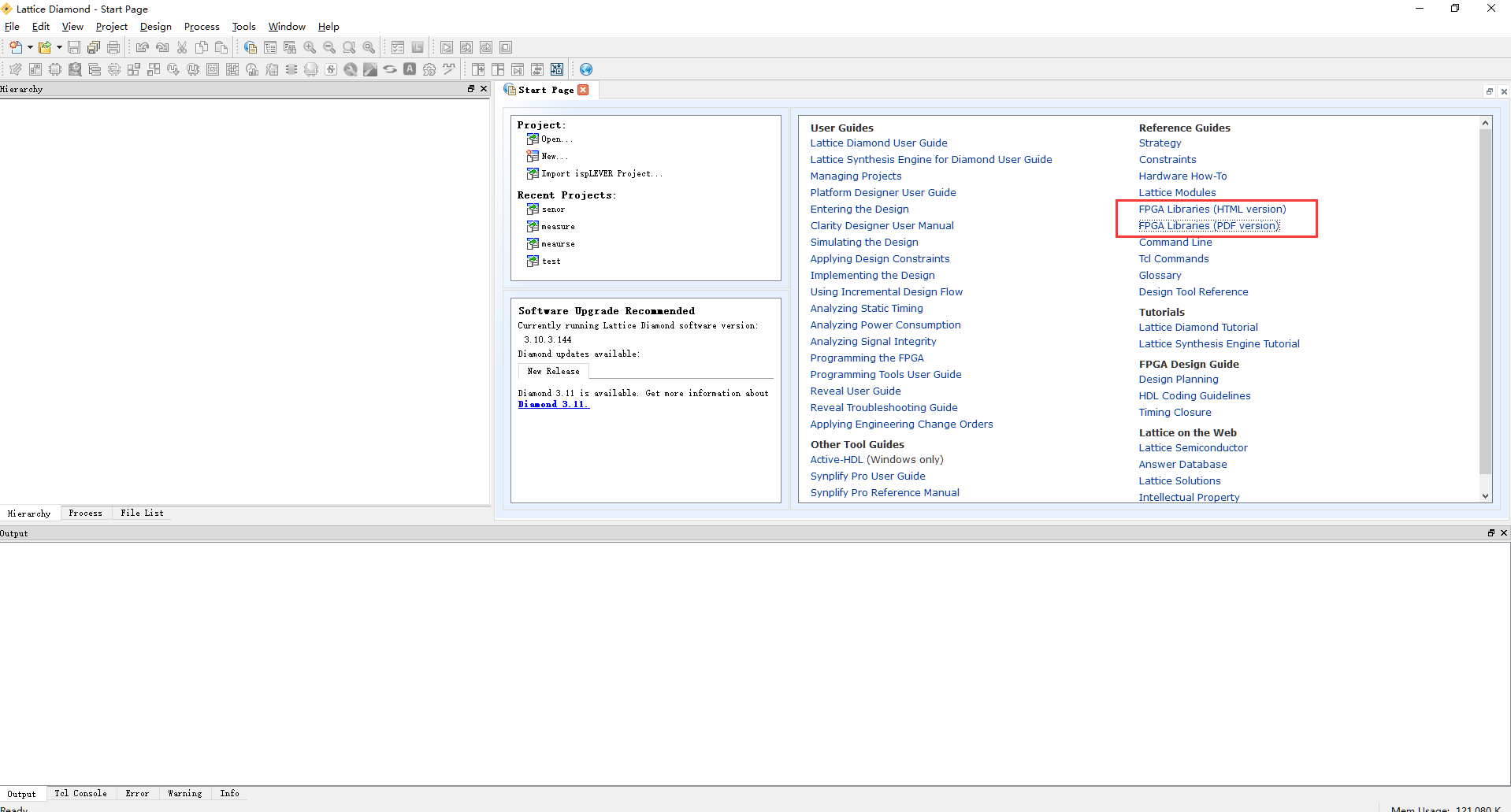

进入lattice diamond软件,可以看到FPGA Libraries (HTML version)和FPGA Librarles (PDF version)。可以点进去找到相应库调用的原语在内的详细介绍。

三、更多使用

因为原语FPGA软件集成开发环境所提供的一系列底层逻辑功能单元,硬件底层是一些门的调用和操作,需要有良好的模电基础,具体参考1.1 Verilog 门的类型|菜鸟教程

参考链接

Diamond软件的使用(6)–Lattice原语基本概念

Lattice FPGA 开发工具Diamond使用流程总结——IP核使用、原语调用