🔥点击查看精选 CXL 系列文章🔥

🔥点击进入【芯片设计验证】社区,查看更多精彩内容🔥

📢 声明:

- 🥭 作者主页:【MangoPapa的CSDN主页】。

- ⚠️ 本文首发于CSDN,转载或引用请注明出处【https://mangopapa.blog.csdn.net/article/details/132553162】。

- ⚠️ 本文目的为 个人学习记录 及 知识分享。因个人能力受限,存在协议解读不正确的可能。若您参考本文进行产品设计或进行其他事项并造成了不良后果,本人不承担相关法律责任。

- ⚠️ 若本文所采用图片或相关引用侵犯了您的合法权益,请联系我进行删除。

- 😄 欢迎大家指出文章错误,欢迎同行与我交流 ~

- 📧 邮箱:mangopapa@yeah.net

- 💬 直达博主:loveic_lovelife 。(搜索或点击扫码)

文章目录

- 0. 引言

- 1. CXL RCRB

- 1.1 RCRB 基地址

- 1.2 RCH DP RCRB

- 1.3 RCD UP RCRB

- 2. CXL Component Registers

- 2.1 RCH/RCD Component Register

- 2.2 Component Register for ALL Other CXL Components

- 2.3 CXL CHBCR

- 3. 参考

0. 引言

CXL Device/Port 相关寄存器一部分位于 PCIe 配置空间内,一部分位于 MMIO 空间内。早前《CXL寄存器分类》简单介绍了 CXL 的寄存器分布及 CXL 相关的 DVSEC,接下来进一步介绍下 MMIO 中的 CXL RCRB 及 Component Registers。

1. CXL RCRB

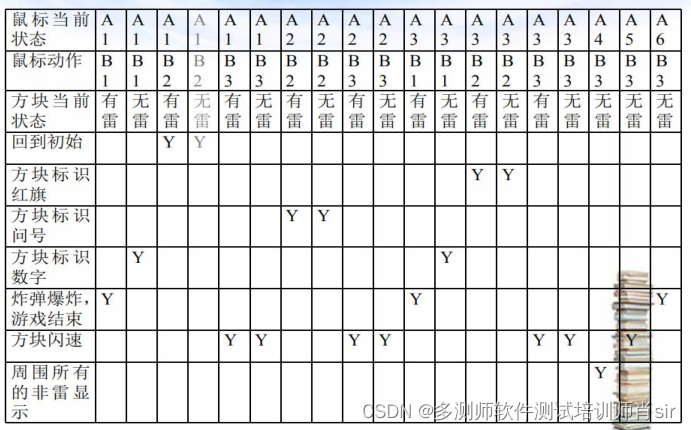

CXL RCH DP 及 RCD UP 没有配置空间,通过扫描 PCIe 配置空间的方式无法发现 RCH DP 及 RCD UP。RCH DP 及 RCD UP 相关的寄存器实现在了 RCRB 范围内。

RCRB 功能类似于 PCIe 配置空间,其内部实现了 CXL 链路相关控制、状态寄存器及各种所需的能力结构。Flex Bus Port DVSEC 是所有 Port RCRB 中必须实现的能力结构,相关介绍可参考《CXL DVSEC》PCIe DVSEC for Flex Bus Port。

1.1 RCRB 基地址

RCRB 的基地址由 System Firmware 指定,

- 对于 eRCD,其 RCRB 基地址由 System Firmware 直接指定;

- 对于工作在 RCD Mode 的 RP 或 DSP,System Firmware 通过配置 PCIe 配置空间中的 CXL DVSEC ID3 中的 RCRB Base/Base_High 并使能 RCRB 来指示 RCRB 的基地址;

- 对于 RCD UP(只能是 eRCD UP 不能为 USP,eRCH 下不能直接挂载 USP),RCD 捕获复位之后收到的第一笔 MRd(CXL 1.1 时 MWr/MRd 均可)的地址(低 12b 清零)作为 RCRB 地址。

上述 RCH 和 RCD 的 RCRB 占用相邻的两个 4KB 地址空间,RCRB 的地址范围不能与 Device 配置空间及内存空间出现交叠。

1.2 RCH DP RCRB

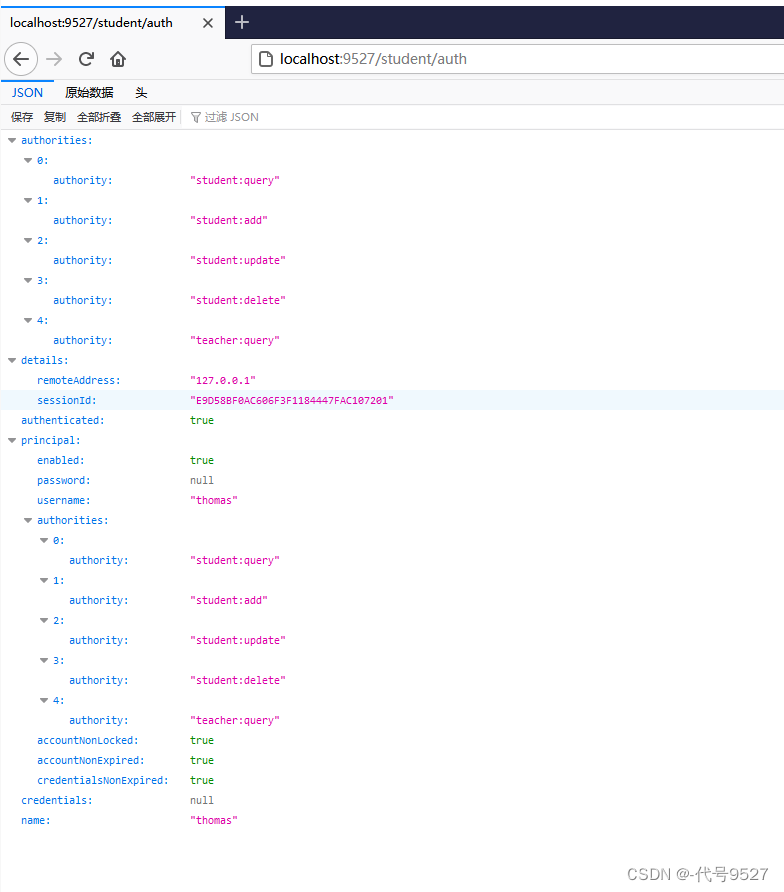

下图是 RCH DP RCRB 寄存器布局图,其带有 Type 1 类型的配置头。RCRB 中的 MEMBAR0 用以指示该 Port 相关的 Component 寄存器在 MMIO 中的基地址。

1.3 RCD UP RCRB

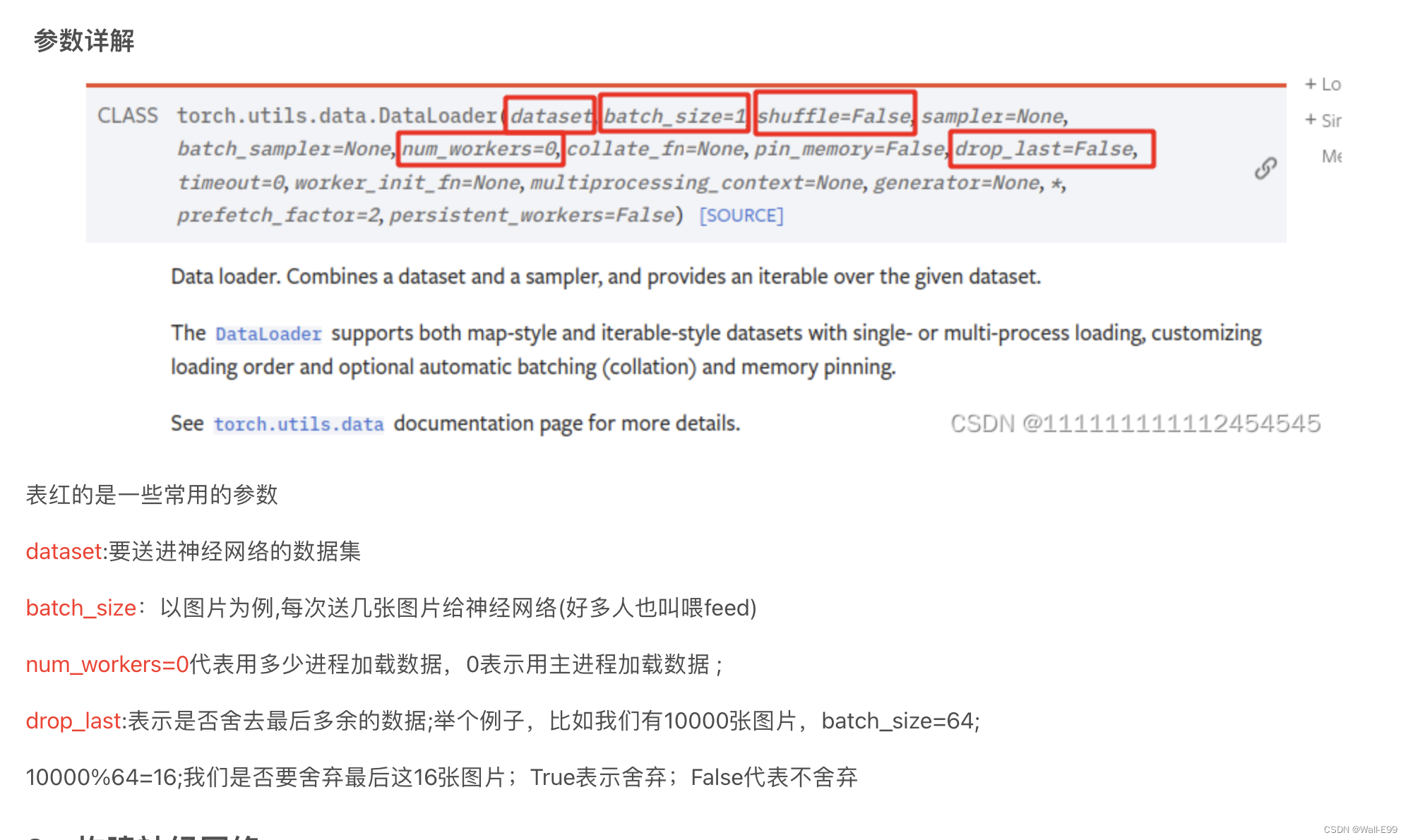

下图是 RCD UP RCRB 寄存器布局图,其带有 Type 0 类型的配置头。对于 RCD UP RCRB,其:

- MEMBAR0 用以指示该 Port 相关的 Component 寄存器在 MMIO 中的基地址;

- Config Header 中 的 Command 寄存器及 Status 寄存器 Reserved;

- Device Capabilities、Control、Status 及 Device Capabilities 2、Control 2、Status 2 Reserved;

- Device/Port Type、Slot 实现、中断消息数量等字段均 Reserved。

2. CXL Component Registers

早前简单介绍了 CXL 的寄存器分布、CXL 相关的 DVSEC 及 MMIO 中的 CXL RCRB,接下来进一步介绍下 MMIO 中的 Component Registers。

2.1 RCH/RCD Component Register

CXL Component Register 包括 CXL.io、CXL.cachemem、CXL ARB/MUX 寄存器等常规 CXL Component 的寄存器,对于实现了 RCRB 的 RCH 及 RCD,该寄存器块唯一 RCRB MEMBAR 内;对于未实现 RCRB 的 RCD 该寄存器块位于 Register Locator DVSEC 指定的 PCIe BAR MMIO 空间内;对于 CXL Host Bridge,该寄存器块位于 CHBCR 内,由 ACPI CEDT 指定其在 Memory Mapped 空间内的基地址。

CXL Component Register 寄存器块 Size 为 64KB,按照地址从前到后的顺序分别为:

- CXL.io 寄存器块,4KB;预留。

- CXL.cachemem 寄存器块 1,4KB;

- 预留给 CXL.cachemem 的扩展寄存器块,48KB;

- CXL ARB/MUX 寄存器块,1KB;

- 预留 7KB。

2.2 Component Register for ALL Other CXL Components

其他 CXL Component 的寄存器块,比如:

- BAR Virtualization ACL Register Block

- CPMU Register Block

- CXL Device Register

- Designated Vendor Specific Register

这组寄存器的具体类型及位置 由 Register Locator DVSEC 来指定。

2.3 CXL CHBCR

CXL 主桥中用以控制一到多个 RP 相关功能的 Component Register Block,其基地址从 ACPI CEDT 中取得。

3. 参考

- CXL Base Spec, r3.0

|

|

🔥 精选往期 CXL 协议系列文章,请查看【 CXL 专栏】🔥

⬆️ 返回顶部 ⬆️