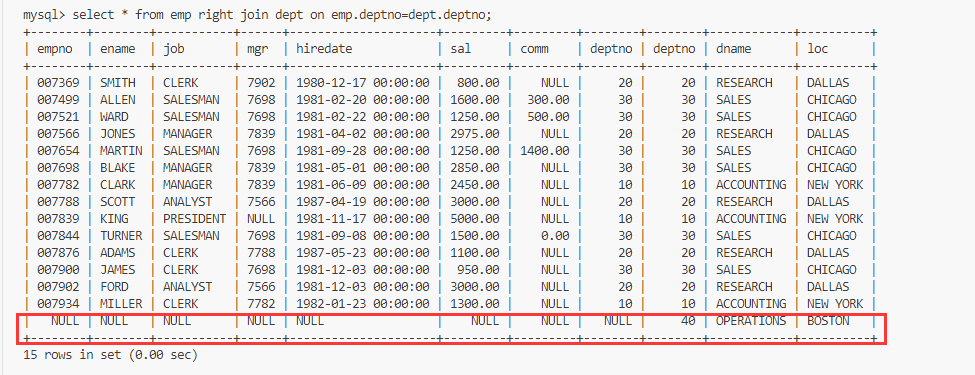

核心信息:

信号:

Layout

信号轨迹:

PCB迹线是有损耗的,长迹线会降低信号质量。痕迹必须尽可能短。除非另有说明,否则所有信号迹线应为50Ω,单端阻抗。差分记录道应为50Ω,单端和100Ω差分。注意阻抗始终保持恒定。阻抗不连续会导致反射,从而导致EMI和信号完整性问题。必须避免使用存根在所有信号迹线上,尤其是差分信号对上。看见图 11-1

在差分对中,迹线长度必须相互平行并在长度上匹配。匹配长度最小化延迟差异,避免共模噪声的增加和EMI的增加。

长度匹配在MAC接口上也很重要。所有传输信号跟踪长度必须相互匹配并且所有接收信号迹线长度必须彼此匹配。

理想情况下,信号路径上不应存在交叉或过孔。过孔存在阻抗不连续性应尽量减少。如果可能,在单层上路由整个跟踪对

不同层上的信号不应在它们之间没有至少一个返回路径平面的情况下相互交叉

迹线之间的耦合也是一个重要因素。不必要的耦合可能会导致串扰问题。另一方面,差分对之间应具有恒定的耦合距离。

为了方便和高效的布局过程,首先对关键信号进行布线。

返回路径:

一般的最佳实践是在所有信号迹线下都有一个坚实的返回路径。此返回路径可以是连续接地或直流电源平面。减小返回路径宽度可能会影响信号迹线的阻抗。当返回路径的宽度与信号迹线的宽度。应不惜一切代价避免信号迹线下方的返回路径中断。A.穿过平面分裂的信号可能会导致不可预测的返回路径电流,并可能影响信号质量并且可能产生EMI问题。看见图 11-2

变压器布置图:

变压器下方不应有金属层。变压器会在下面的金属中注入噪音它们会影响系统的性能

金属连接:

所有不是信号或电源的金属连接都应接地。上面不应该有漂浮的金属系统。差分迹线之间不应有金属

PCB层堆叠:

为了满足信号完整性和性能要求,至少应使用4层PCB。然而建议使用6层板。看见图 11-3用于4层、6层和8层板的推荐层堆叠。这些是建议而非要求,可以根据系统要求使用其他配置。

在PCB中,可能需要使用不同的方法运行迹线,微带线与带状线,具体取决于PCB上信号的位置。例如,可能需要改变层堆叠使用底盘接地平面。图 11-4示出了可供选择的PCB堆叠选项

布局示例:

![【PWN · ret2text | RISC-V异构】[2023 羊城杯]login](https://img-blog.csdnimg.cn/989b8062afa04f91bfa8378b366aac1d.png)