🔥点击查看精选 CXL 系列文章🔥

🔥点击进入【芯片设计验证】社区,查看更多精彩内容🔥

📢 声明:

- 🥭 作者主页:【MangoPapa的CSDN主页】。

- ⚠️ 本文首发于CSDN,转载或引用请注明出处【https://mangopapa.blog.csdn.net/article/details/132553166】。

- ⚠️ 本文目的为 个人学习记录 及 知识分享。因个人能力受限,存在协议解读不正确的可能。若您参考本文进行产品设计或进行其他事项并造成了不良后果,本人不承担相关法律责任。

- ⚠️ 若本文所采用图片或相关引用侵犯了您的合法权益,请联系我进行删除。

- 😄 欢迎大家指出文章错误,欢迎同行与我交流 ~

- 📧 邮箱:mangopapa@yeah.net

- 💬 直达博主:loveic_lovelife 。(搜索或点击扫码)

文章目录

- 0. 缩写

- 1. CXL 内存交织概念

- 2. CXL 内存交织实现

- 2.1 HDM Decoder 基本介绍

- 2.1.1 交织集/交织设置(Interleave Set)

- 2.2 HDM Decoder 相关寄存器

- 2.2.1 CXL HDM Decoder 能力结构

- 2.2.1.1 状态

- 2.2.1.2 控制

- 2.2.2 CXL HDM Decoder 扩展能力结构

- 2.2.3 Desired_Interleave @CXL DVSEC ID0

- 2.3 HDM Decoder 解码规则

- 2.3.1 CXL RP/USP 中的 HDM 地址解码

- 2.3.2 CXL Device 中的 HDM 地址解码

- 3. CXL 内存交织举例

- 4. Q&A

- 5. 参考

0. 缩写

| 缩略词 | 释义 |

|---|---|

| BI | Back Invalidation |

| DPA | Device Physical Address,设备物理地址 |

| DSP | Downstream Switch Port,Switch 的下行端口 |

| eRCD | Exclusive Restricted CXL Device,只支持 CXL 1.1 的 CXL Device |

| HDM | Host-managed Device Memory,由 Host 管理的 Device Memory |

| HPA | Host Physical Address,主机物理地址 |

| IG | Interleave Granularity,交织粒度 |

| IW | Interleave Way,交织路数 |

| RP | Root Port,根节点 |

| UIO | Unordered Input/Output,无序 IO |

| USP | Upstream Switch Port,Switch 的上行端口 |

1. CXL 内存交织概念

Memory Interleaving,内存交织,是一种内存访问方法,其将一段连续的内存地址映射到不同的内存,通过在不同内存上交叉访问来提高内存访问性能。一个带有 4 Bank 的内存交织访问示意图如下,其中红色 Bank 表示其正在进行自刷新且不可用。

https://en.wikipedia.org/wiki/Interleaved_memory#/media/File:Interleaving.gif

对于 CXL 而言,CXL 内存交织是指把一段地址连续的 HDM 地址以统一的地址间隔映射到不同 CXL.mem Device 的 HDM 中。

CXL 1.1 时,对于 Multi-head 的 eRCD,若多个 eRCD UP 直连到同一 CPU 内的 RCH 上,改 CPU 可以通过不同发 Flex Bus 来交织访问改 eRCD 的 HDM 空间。相关介绍可以参考《Multi-headed eRCD》。

CXL 2.0 时支持多个 CXL Device 之间的内存交织,通过配置传输链路上相关 Host Bridge、USP 及 Device 内的 HDM Decoder 来实现相关控制。进一步地,CXL 支持在同一跨主桥逻辑下的 多个 CXL 主桥 之间、同一 CXL 主桥下的 多个 RP 之间、同一 Switch 内的 多个 DSP 之间有选择地进行 单级或多级 Interleave 访问。

2. CXL 内存交织实现

CXL 主桥、USP 及 Device 基于 HDM Decoder 来实现内存交织中的 CXL.mem 包路由及 HPA->DPA 的地址映射。多个 CXL 主桥之间的 Interleave 由 跨主桥逻辑内的 Host 属性寄存器 进行控制。

2.1 HDM Decoder 基本介绍

HDM Decoder 是 HDM 地址解码器,CXL 组件依据 HDM Decoder 内的相关配置把上层设备发来的 CXL.mem 访问请求路由到不同的端口或设备区域。

HDM Decoder 位于 Host Bridge、USP 及 CXL Device 中:

- 对于 Host Bridge 及 USP 而言,HDM Decoder 主要起路由作用,将 Host Bridge 或 USP 下发的 Transaction 分配到对应的 RP 或 DSP 上;

- 对于 Device,HDM Decoder 主要用于把带有 Interleave 信息的 HPA 映射到 DPA。

2.1.1 交织集/交织设置(Interleave Set)

同一 HDM Decoder 控制下的一组内存交织的 CXL Device 称为一个交织集(Interleave Set),HDM Decoder 基于以下关键参数对内存交织行为进行控制:

- Base HPA ,HPA 基地址,要求 256 MB 地址对齐,即地址低 28b 为 0。

- Size ,内存交织地址空间大小,需要为 256 MB 的整数倍,从 HPA Base ~ (HPA Base + Size)之间为当前 HDM Decoder 所要控制的内存交织地址范围。

- Interleave Way (IW),内存交织路数,即把当前的 Size 的 HPA 空间映射到 IW 指示的路数,CXL 2.0 时 CXL RP/DSP/Device 支持 1/2/4/8 路交织,到 CXL 3.0 后同一 CXL Device 内还支持 3/6/12/16 路交织(RP/USP 不支持)。

- Interleave Granularity (IG),内存交织粒度,每隔 IG 所指示的粒度,就将相关包路由到下一路出口上;支持 256B、512B、1KB、2KB、4KB、8KB、16KB 粒度的内存交织,分别对应 HPA[8]~HPA[14]。对于 RCH 除外的 CXL Host Bridge 必须支持所有 IG(HPA[8:14]共七种),对于 CXL Type3 Device 必须支持其 HDM Decoder 能力结构显示的 HPA[8:11]或 HPA[12:14]中的至少一组 IG。

- Target ,内存交织目标,可以为 CXL 根节点(RP)或 Switch 下行端口(DSP)。

软件通过配置 HDM Decoder 来确定一个 Interleave Set。若同一 CXL 组件内存在多个 HDM Decoder,软件需确保同一组件内部多个 Decoder 之间以及同一 Path 内上下游 HDM Decoder 之间的行为一致,并通过 Commit Flow 发起自身一致性检查。对于同一组件内的多个 HDM Decoder,不能出现地址重合之类的错误;对于同一 Path 上的 HDM Decoder,上游 Decoder 的 Range 应包含下属 HDM Decoder 的 Range。

2.2 HDM Decoder 相关寄存器

2.2.1 CXL HDM Decoder 能力结构

CXL 组件采用 CXL HDM Decoder 能力结构对其内部的 HDM Decoder 进行控制或指示,其寄存器分布如下图所示。

对于 CXL 主桥(HID=“ACPI0016”),若其下存在多个 CXL RP,该 CXL 主桥的 CHBCR 中必须实现该能力结构;对于 CXL Switch,其 USP Component Register Block 中必须实现该能力结构;对于非 eRCD 的 Type 3 Device 或支持 BI/UIO 的 Type2 Device,应实现该能力结构,将 HPA 映射到其内部 DPA。

2.2.1.1 状态

HDM Decoder 能力结构能够指示以下能力/参数/状态:

- Decoder Count,当前组件内支持的 HDM Decoder 的数量,CXL Device 内最所支持 10 个 HDM Decoder,RP 和 Switch 最多支持 32 个;

- Target Count,每个 Decoder 支持下属 1/2/4/8 个目标端口;

- UIO Capable、Meta-NXM Capable,是否支持 UIO、Meta-NXM;

- Address Interleave Capable,支持基于哪些 HPA 地址位的交织地址,有 HPA[8:11]和 HPA[12:14]两组;

- 是否支持 3/6/12 或 16 路地址交织;、

- ……

2.2.1.2 控制

HDM Decoder 能力结构能够控制以下参数:

- 是否开启 HDM Decoder

- 每个 HDM Decoder 的基地址及 Size

- 每个 HDM Decoder 的交织路数

- 目标类型,为 HDM-D/DB 还是 HDM-H

- 是否使能 BI 或 UIO 中的地址交织

- 每一路所对应的 Port ID

- ……

每个 HDM Decoder 都有 Commit 相关寄存器,Commit 可以理解为 Decoder Info Valid,在配置完 HDM Decoder 之后需要按从前往后的顺序配置 Commit=1 并将其 Lock 住。

2.2.2 CXL HDM Decoder 扩展能力结构

CXL HDM Decoder 能力结构支持的 HDM Decoder 数量有限,CXL 协议提供了一组 CXL HDM Decoder 扩展能力结构(CXL Extended HDM Decoder Capability Structure)以支持更多的 HDM Decoder 数量。CXL HDM Decoder 扩展能力结构内的寄存器布局与 CXL HDM Decoder Capability Structure 完全一致,两者 Capability ID 不同。

2.2.3 Desired_Interleave @CXL DVSEC ID0

在 CXL Device 的 CXL PCIe DVSEC 中,HDM Range 寄存器内有换个 Desired_Interleave 字段来指示当前 HDM Range 所预期的内存交织粒度。CXL 1.1 的时候只支持 256B 和 4KB 两种粒度,到了 CXL 2.0 增加支持 512B, 1KB, 2KB, 8KB, 16KB 交织粒度。

对于支持 CXL.mem 的 eRCD,若其通过多个 CXL Link 连接到了单个 CPU 上,该字段用以指示 Device 期望的交织粒度。BIOS 配置 CPU 通过交织的方式来访问该 HDM Range,在 Host 支持的范围内访问粒度可以采用 Device 所期望的粒度或最接近期望值的粒度。

对于 Non-eRCD,该字段表示该设备期望交织粒度的最小值,可以视为一种 Hint。若 Device 实现了 HDM Decoder 能力结构,软件配置的 IG 建议大于等于 Device 所指示的 Desired_Interleave,即便比 Desired_Interleave 小,Device 也要保证内存交织功能正确。

对于同一个 CXL Device,若当前 CXL Range 内的多个 DPA Range 有不同的 Desired_Interleave 值,Device 应采用所有 DPA Range 中的最大 Desired_Interleave 值;对于同一 Interleave Set 中的多个 Device,若其上报的 Desired_Interleave 值不同,软件选择最小的 Desired_Interleave 值。

2.3 HDM Decoder 解码规则

2.3.1 CXL RP/USP 中的 HDM 地址解码

若开启了 CXL 内存交织,CXL RP 及 USP 中的 HDM Decoder 负责检测 HPA 是否位于 Active Decoder 的 HPA Base ~HPA+Size 之间,

- 若没落在任何 Decoder 范围内,

- Write 直接 Drop;

- Read 且 Decoder Error Enable=0,直接反馈全 1;

- Read 且 Decoder Error Enable=1,反馈 Poison。

- 若落在了某 Decoder 范围之内,

- 依据 HDM Decoder 中的交织粒度及交织路数参数,提取当前 HPA 相关地址位,判断需要路由到哪一路端口中;

- 读取上述端口号,发送到上述请求到相关该端口。

2.3.2 CXL Device 中的 HDM 地址解码

若开启了 CXL 内存交织,CXL Device 中的 HDM Decoder 负责检测是否位于 Active Decoder 的 HPA Base ~HPA+Size 之间,并将 HPA 还原为 DPA,

- 若没落在任何 Decoder 范围内,

- Write 直接 Drop;

- Read 且 Decoder Error Enable=0,直接反馈全 1;

- Read 且 Decoder Error Enable=1,反馈 Poison。

- 若落在了某 Decoder 范围之内,抹去 HPA 内用以 Interleave 用的地址位作为 DPA Offset,加上 DPA.Base 作为 DPA,Device 内部访问 DPA。

3. CXL 内存交织举例

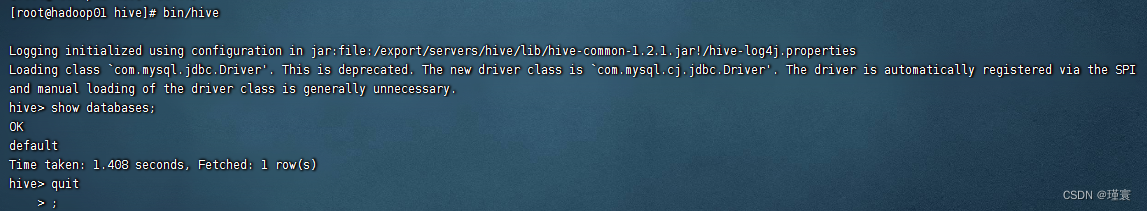

CXL 内存交织支持单级或多级 Interleave,其中 Target 为 RP、DSP 的层级中 Interleave 路数只能为 1/2/4/8 路,跨主桥逻辑及 CXL 设备内支持 3/6/12/16 路 Interleave。

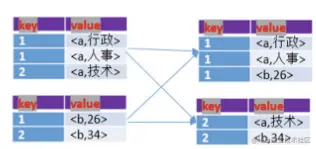

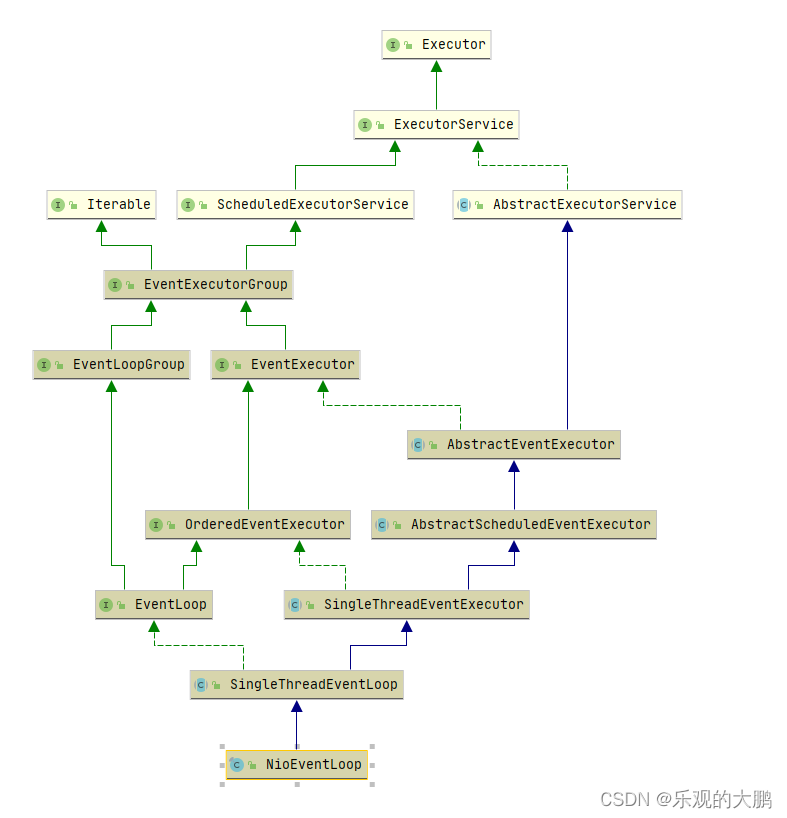

下图是一个对 16~20 TB 的 HPA 空间进行 8 路三级 Interleave 的例子。

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-luSeVGfr-1693265230892)(RackMultipart20230828-1-a7e9p4_html_b1f6f63b7c816202.gif)]](https://img-blog.csdnimg.cn/d411907cf91f46d5b82b61a9cee2fc48.png#pic_center)

上图释义如下:

- 跨主桥逻辑内设置为 2 路交织,IG 为 4KB,依据 HPA[12]进行路由,即[16TB+2*n*4KB,16TB+2*n*4KB+4KB)区间内的 CXL.mem 请求路由至左侧的 CXL 主桥,[16TB+2*n*4KB+4KB,16TB+2*n*4KB+8KB)区间内的 CXL.mem 请求路由至右侧的 CXL 主桥;

- 设置每一个 CXL 主桥的 HDM Decoder 为 2 路 2KB 粒度的交织,依据 HPA[11]决定路由到其下哪个 RP

- 设置每一个 CXL Switch USP 的 HDM Decoder 为 2 路 1KB 粒度的交织,依据 HPA[10]决定路由到哪个 DSP;

- 设置 CXL Device 为 8 路 1KB 交织,Device 以此为依据取 CXL.mem HPA[12:10]=0,转换为 DPA 后对 DPA 进行访问。

4. Q&A

-

同一 Decoder 下不同 Way 之间的 IG 可以不同吗?

不可以,同一 Decoder 内只要=存在一个 IG 寄存器,所有 Way 均遵从该配置。 -

RP/DSP 中没有 HDM Decoder 吗?

RP 及 DSP 中没用 HDM Decoder,这两者的 Decode 之后的 Transaction 接收方,其根 USP 或 Device UP 是一对一点到点连接,无需 Interleave。 -

Interleave Set 是如何建立的?

配置链路上的各个 HDM Decoder 能力结构。 -

HDM Decoder 能力结构中的 Commit 是什么意思?

简单理解为 HDM Decoder 的 Info_Valid 吧。 -

上边下来的 CXL.mem 包没用 BDF 号吗?指定了 BDF 号的话,是怎么实现 Interleave 的?要改 BDF 吗?

Interleave 仅限 CXL.mem 的包,其不是 PCIe 那种 TLP,没用 BDF,而是采用 HDR 或 PBR 的路由方式。

5. 参考

- CXL Base Spec, r3.0

- Interleaved memory - Wikipedia

- What is Interleaved Memory? | Webopedia

- 聊一聊DDR(7)—— 内存交织(memory interleaving) - 知乎 (zhihu.com)

- DDR 的多通道(channel)和交织(interleave) - 简书 (jianshu.com)

- memory interleaving(内存交织)_南风在冥想的博客-CSDN 博客

- 内存系列二:深入理解硬件原理- 知乎 (zhihu.com)

- 存储器术语interleave 解释_雨轩学院的博客-CSDN 博客

|

|

🔥 精选往期 CXL 协议系列文章,请查看【 CXL 专栏】🔥

⬆️ 返回顶部 ⬆️