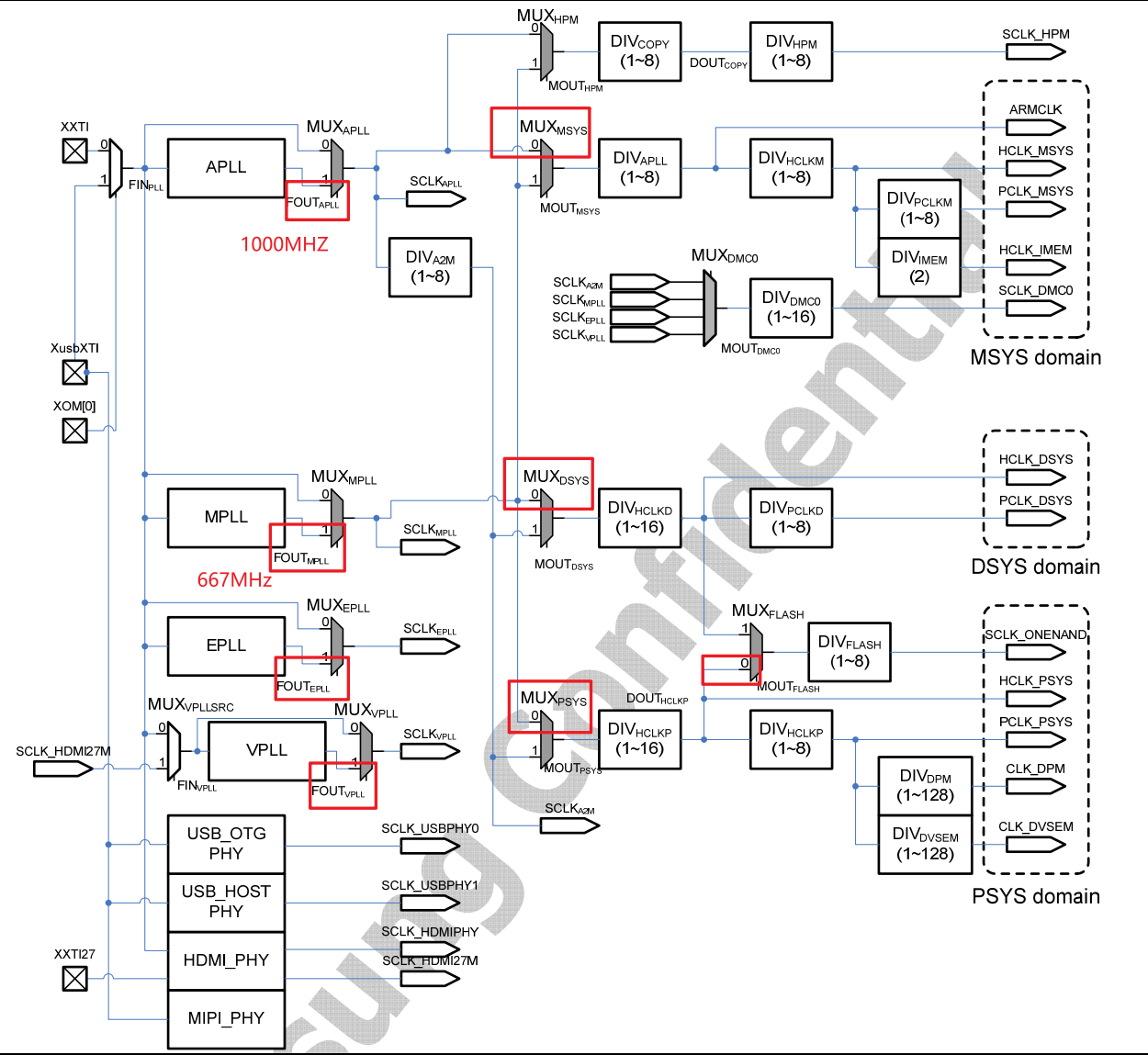

一、时钟设置的步骤分析

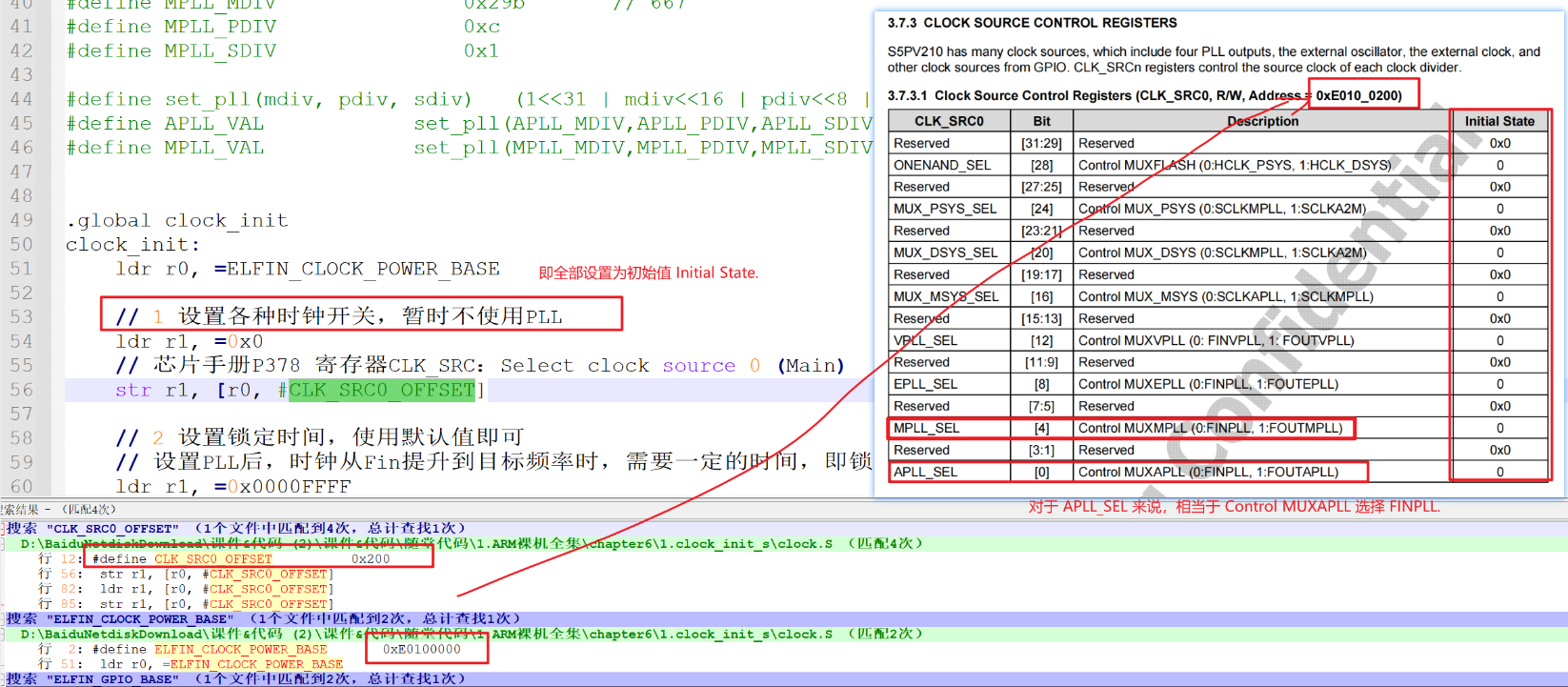

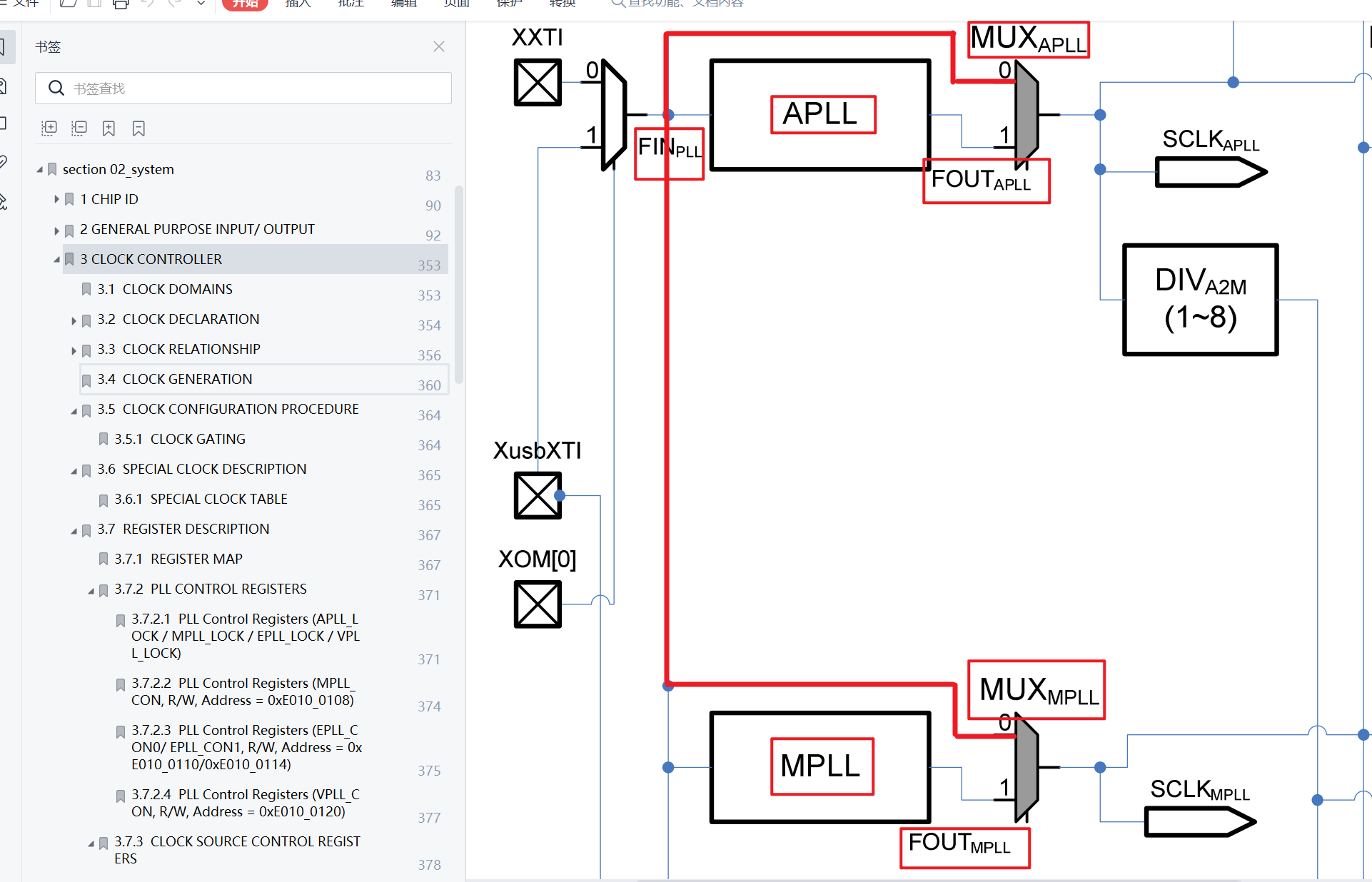

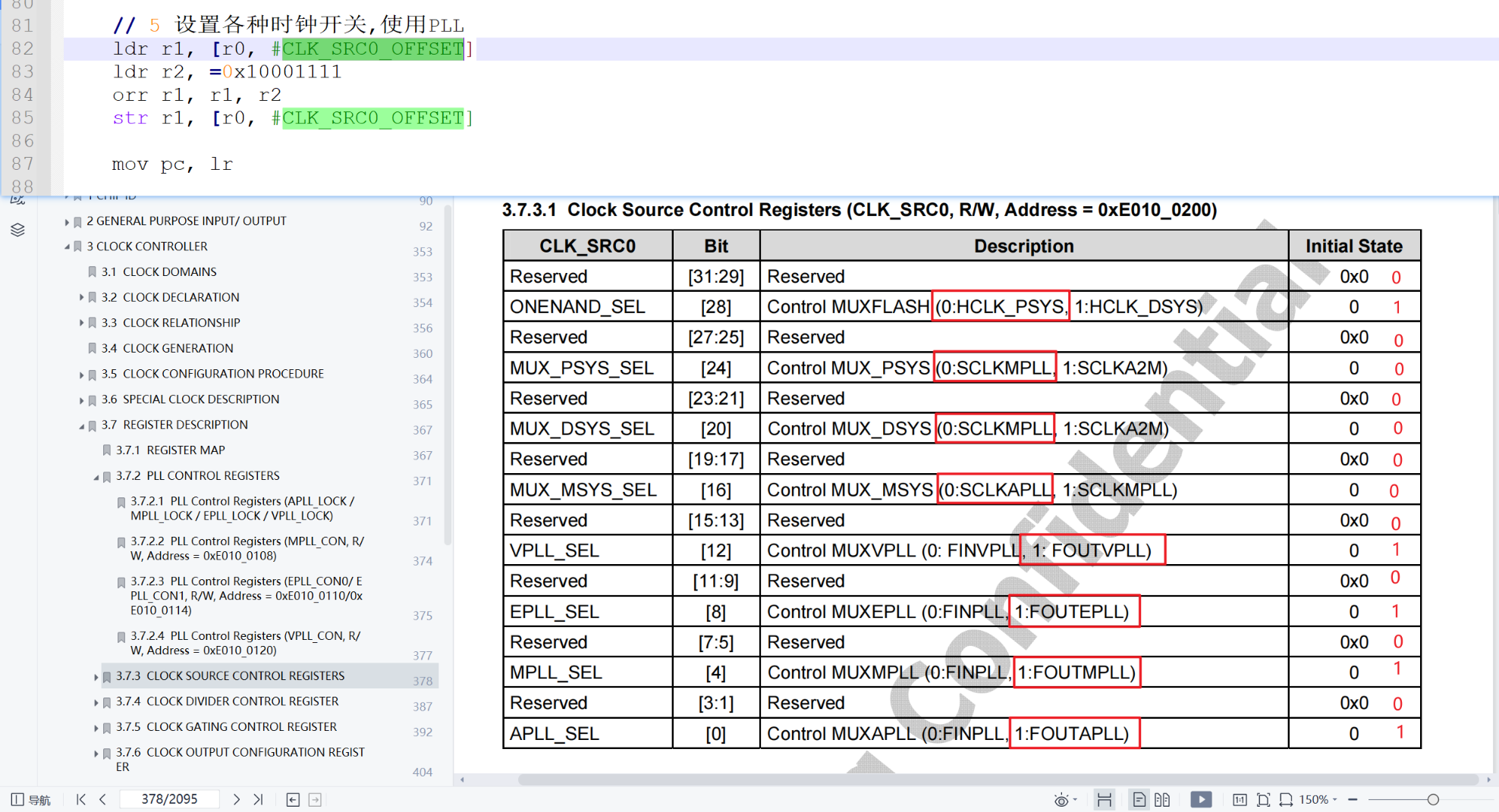

第1步:CLK_SRC寄存器的设置分析

先选择不使用 PLL。让外部 24MHz 原始时钟直接过去,绕过 APLL 那条路。

CLK_SRC 寄存器其实是用来设置 MUX 开关的。在这里先将该寄存器设置为全 0,主要是 bit0 和bit4 设置为 0,表示 APLL 和 MPLL 暂时都不启用。

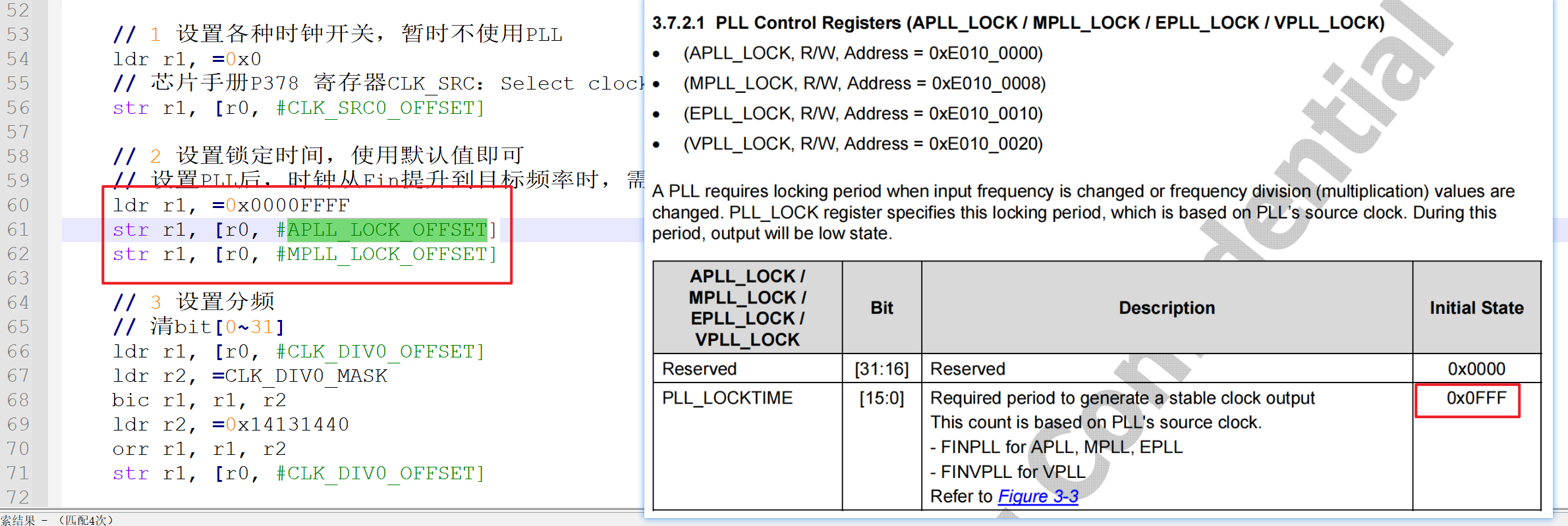

第2步:CLK_LOCK 寄存器的设置分析

设置 PLL 锁定延时的。官方推荐值为 0xFFF,我们设置为 0xFFFF。

设置锁定时间。默认值为0x0FFF,保险起见我们设置为0xFFFF。

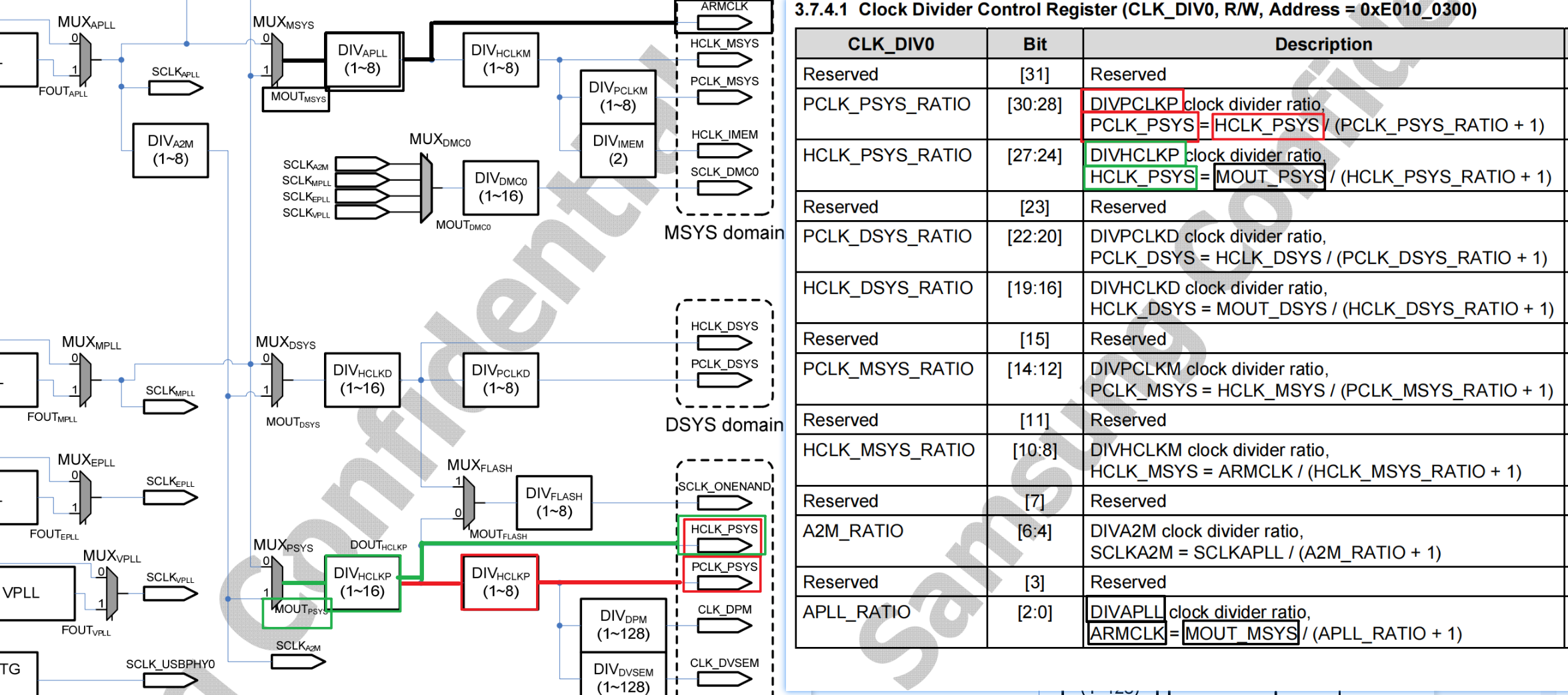

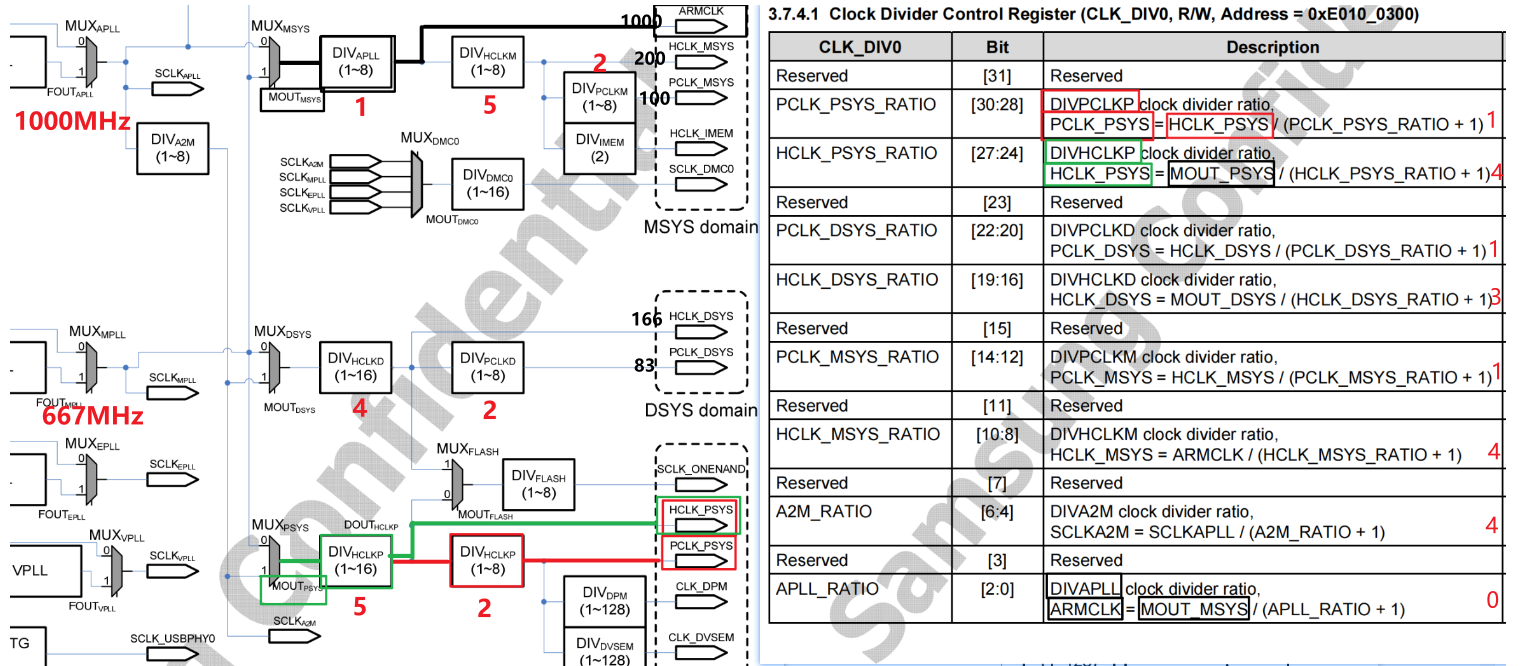

第3步:CLK_DIV 寄存器的设置分析

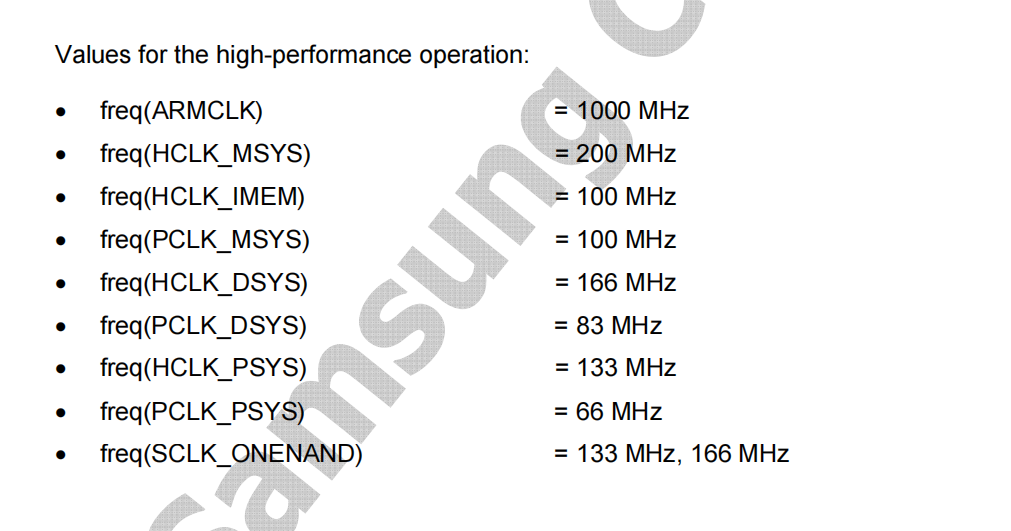

0x14131440 这个值的含义分析:

PCLK_PSYS = HCLK_PSYS / 2

HCLK_PSYS = MOUT_PSYS / 5

PCLK_DSYS = HCLK_DSYS / 2

HCLK_DSYS = MOUT_DSYS / 4

·······

HCLK_MSYS = ARMCLK / 5

ARMCLK = MOUT_MSYS / 1

设置分频系统,决定由 PLL 出来的最高时钟如何分频得到各个分时钟。

下图使用 3 种颜色标签标注了详细情况。

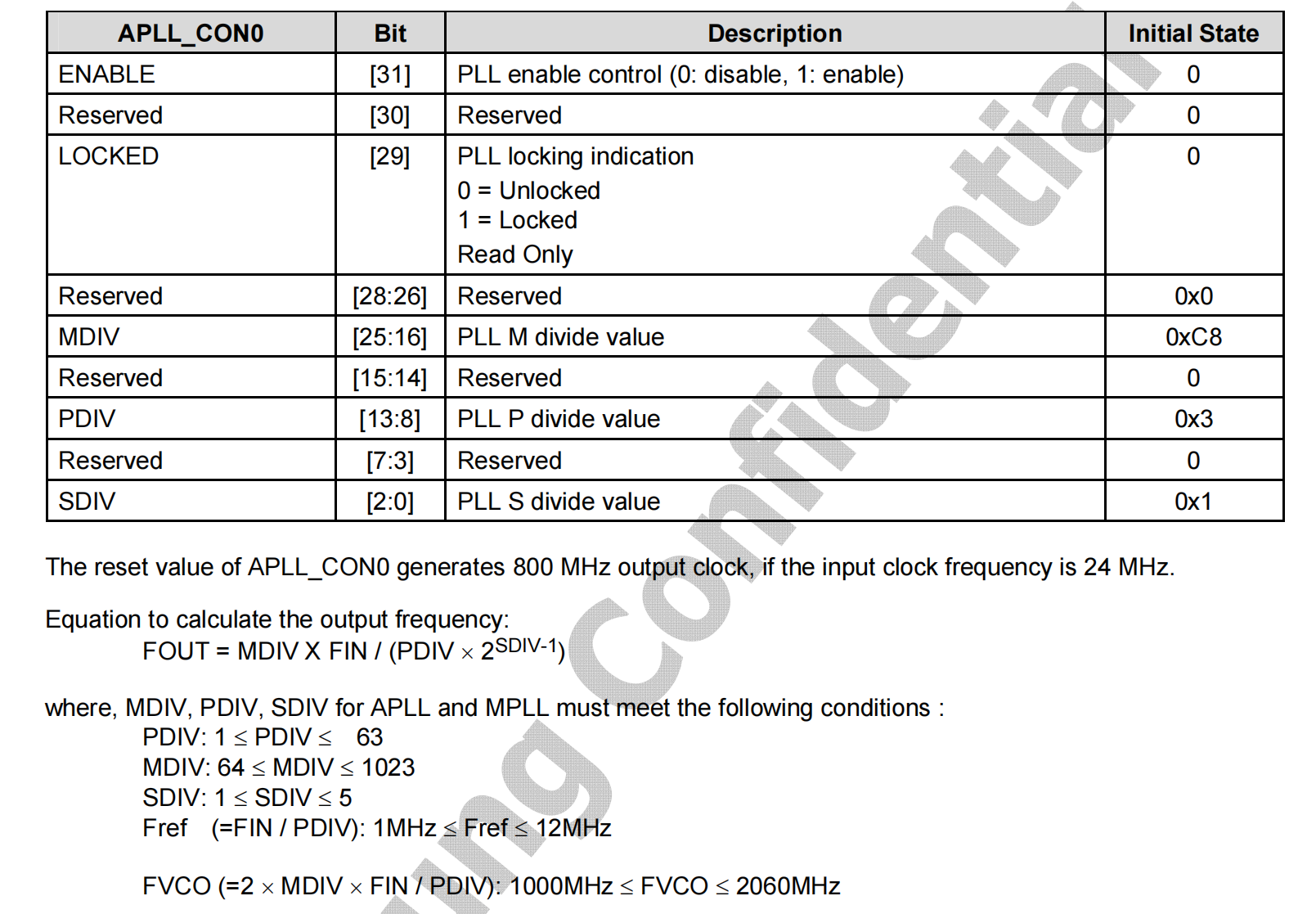

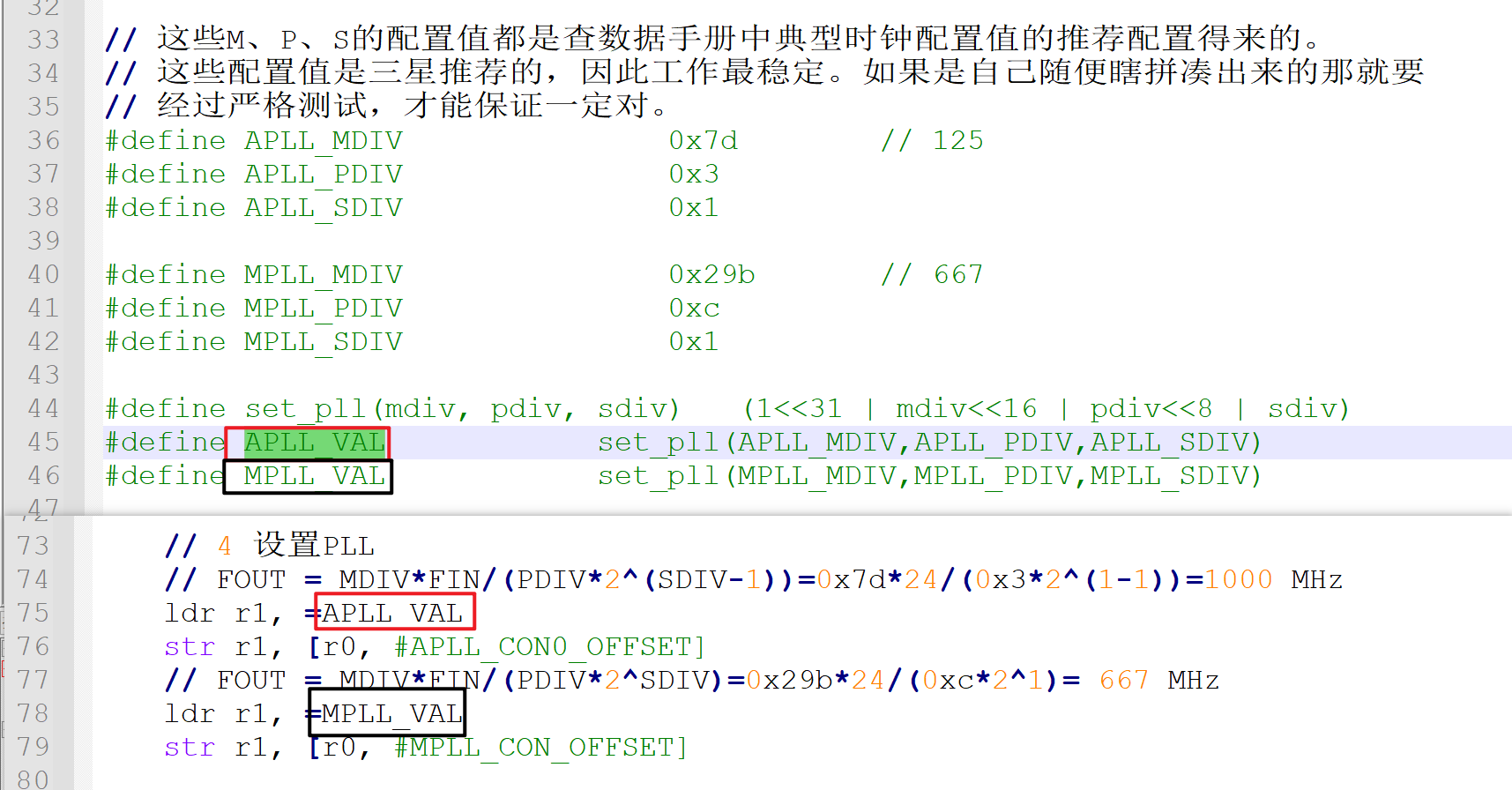

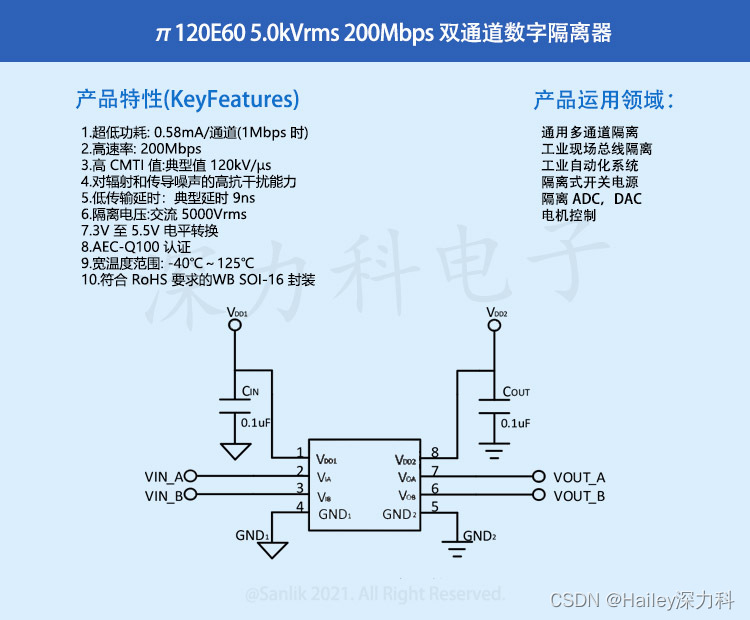

第4步:设置PLL

主要是设置 PLL 的倍频系统,决定由输入端 24MHz 的原始频率可以得到多大的输出频率。我们按照默认设置值设置输出为 ARMCLK 为 1GHz.

PLL 倍频的相关计算

(1)、我们设置了 APLL 和 MPLL 两个,其他两个没有管。

(2)、APLL 和 MPLL 设置的关键都是 M、P、S 三个值,这三个值都来自于官方数据手册的推荐值

第5步:打开PLL

前面4步已经设置好了所有的开关和分频系数,本步骤打开 PLL 后 PLL 开始工作,锁定频率后输出,然后经过分频得到各个频率。

第6步:最后可以得到时钟频率图

可以看到,我们配置的跟用户手册要求的频率是相同的。

总结:以上 5 步,其实真正涉及到的寄存器只有5个而已。

源自朱有鹏老师.

![[激光原理与应用-60]:激光器 - 光学 - 光的四大理论框架与其层次:几何光学、波动光学、电磁光学、电子光学](https://img-blog.csdnimg.cn/255216ad005943f9a16ba679b7bb17d8.png)

![[附源码]Node.js计算机毕业设计个人资金账户管理Express](https://img-blog.csdnimg.cn/e13f48f86ad64c27a5804c72a772de81.png)