一、前言

嵌入式硬件平台调试中常用的debug方法是看串口打印定位问题,但有时候会遇到单片机没有串口外设或者串口引脚被占用的情况,这时候也可以在代码里操作空闲的IO输出不同个数的脉冲来达到调试的效果,但是要用逻辑分析仪抓线逐个看波形比较费劲。既然都IO抖线了,干脆抖个串口协议出来算了,通过控制IO口电平变化模拟串口协议。

二、串口协议

1、协议介绍

UART作为异步串口通信协议的一种,工作原理是将传输数据的每个字符一位接一位地传输。其中每一位(Bit)的意义如下:

起始位:先发出一个逻辑”0”的信号,表示传输字符的开始。

数据位:紧接着起始位之后。数据位的个数可以是4、5、6、7、8等,构成一个字符。通常采用ASCII码。从最低位开始传送,靠时钟定位。

奇偶校验位:数据位加上这一位后,使得“1”的位数应为偶数(偶校验)或奇数(奇校验),以此来校验数据传送的正确性。

停止位:它是一个字符数据的结束标志。可以是1位、1.5位、2位的高电平。由于数据是在传输线上定时的,并且每一个设备有其自己的时钟,很可能在通信中两台设备间出现了小小的不同步。因此停止位不仅仅是表示传输的结束,并且提供计算机校正时钟同步的机会。适用于停止位的位数越多,不同时钟同步的容忍程度越大,但是数据传输率同时也越慢。

空闲位:处于逻辑“1”状态,表示当前线路上没有数据传送。

2、传输过程

发送数据过程:空闲状态,线路处于高电位;当收到发送数据指令后,拉低线路一个数据位的时间T,接着数据按低位到高位依次发送,数据发送完毕后,接着发送奇偶校验位和停止位(停止位为高电位),一帧数据发送结束。

接收数据过程:空闲状态,线路处于高电位;当检测到线路的下降沿(线路电位由高电位变为低电位)时说明线路有数据传输,按照约定的波特率从低位到高位接收数据,数据接收完毕后,接着接收并比较奇偶校验位是否正确,如果正确则通知后续设备准备接收数据或存入缓存。

由于UART是异步传输,没有传输同步时钟。为了能保证数据传输的正确性,UART对RX线上的数据采样时通常取中间的采样值或者是从中间取多个点的值然后取出现次数最多的电平值,以保证采样不会滑码或误码。

之前也写过一篇FPGA实现串口协议的文章《FPGA专题——串口通信》

三、代码实现

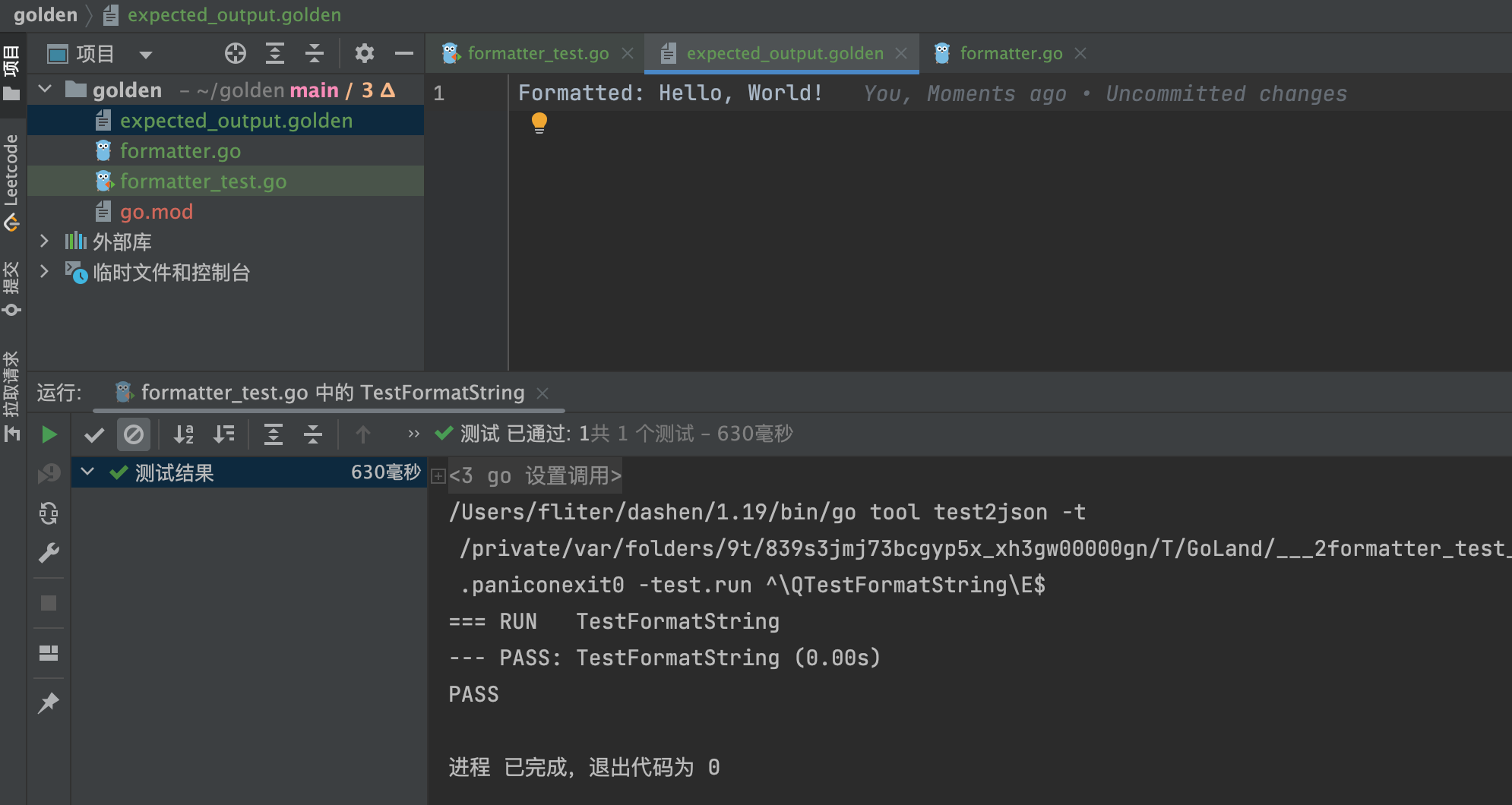

基于STM32实现代码如下

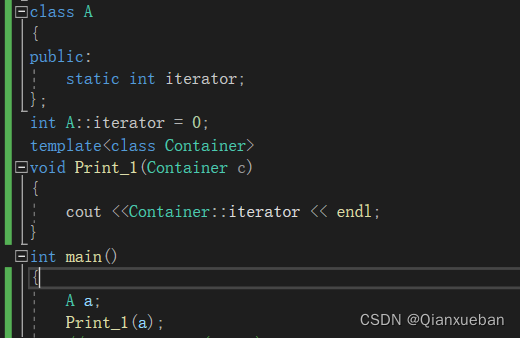

#define sw_tx_io_high GPIO_SetBits(GPIOB, GPIO_Pin_1)

#define sw_tx_io_low GPIO_ResetBits(GPIOB, GPIO_Pin_1)

void delay(u32 i)

{

while(i--)

{

__NOP();

}

}

void sw_uart_init(void)

{

sw_tx_io_high;

}

void sw_uart_putchar(u8 ch)

{

u8 dat[10]; // 1 start bit + 8 data bit + 1 stop bit

u8 i;

// start bit

dat[0] = 0;

// data bit

for (i = 0; i < 8; i++)

{

if (ch & 0x01)

{

dat[i + 1] = 1;

}

else

{

dat[i + 1] = 0;

}

ch >>= 1;

}

// stop bit

dat[9] = 1;

for (i = 0; i < 10; i++)

{

if (dat[i])

{

sw_tx_io_high;

}

else

{

sw_tx_io_low;

}

delay(64); // 8.68 us, 115200 baudrate

}

}

void sw_uart_putStr(u8* str)

{

while (*str != 0)

{

sw_uart_putchar(*str);

str++;

}

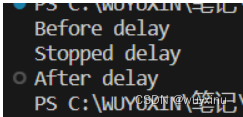

}sw_uart_putchar 控制单次输出一个字符,测试中定波特率为115200,那么停止位(即最小脉冲宽度)为1 / 115200 = 8.68us,使用逻辑分析仪或者示波器,调整delay函数传入的参数,我这边测试是给64的时候可以调整到8.68us左右,当然大概调到这个时间就行了不需要很准,串口协议本身可以容忍一定的误差。

delay函数使用MCU空等待来实现延时效果。

最后使用 sw_uart_putStr("Hello CSDN \r\n"); 可以在串口助手上显示“Hello CSDN”。