AD绘制四层板

- 前言

- 一、正片层和负片层介绍

- 二、PCB板的叠层设计

- 1.两层板的叠层

- 2.四层板的叠层

- 三、规则设计

- 参考资料

前言

1、用 Altium Designer 软件绘制电路时,通常2层板能实现设计需求。遇到板框固定,元器件密集的情况下,2 层板无法实现预期功能,考虑设计多层板;

2、本文主要介绍AD四层板的设计流程,其中PCB的叠层设计、内缩设计及DRC设计规则是关键。

3、软件版本:Altium Designer 19.0.4

一、正片层和负片层介绍

1、正片层(Signal)

正片就是平常用在走线的信号层,即走线的地方是铜线,用Polygon Pour进行大块敷铜填充。

2、负片层(Plane)

负片正好相反,即默认敷铜,走线的地方是分割线,也就是生成一个负片之后整一层就已经被敷铜了,要做的事情就是分割敷铜,再设置分割后的敷铜网络。

3、内电层的分割实现

AD中直接用Line,快捷键P+L,来分割,分割线不宜太细,用15mil及以上。

要分割敷铜时,只要用Line画一个封闭的多边形框,在双击框内敷铜设置网络即可。

正负片都可以用于内电层,正片也可通过走线和敷铜实现。

负片的好处:默认大块敷铜填充,在添加过孔,改变敷铜大小等等操作都不需要Rebuild,这样省去了PROTEL重新敷铜计算的时间。中间层用于电源层和GND层时候,层面上大多是大块敷铜,这样用负片的优势就很明显。

建议信号层采取“正片”的方式处理,电源层和GND层采取“负片”的方式处理,可以很大程度上减小文件数据量的大小和提高设计的速度。

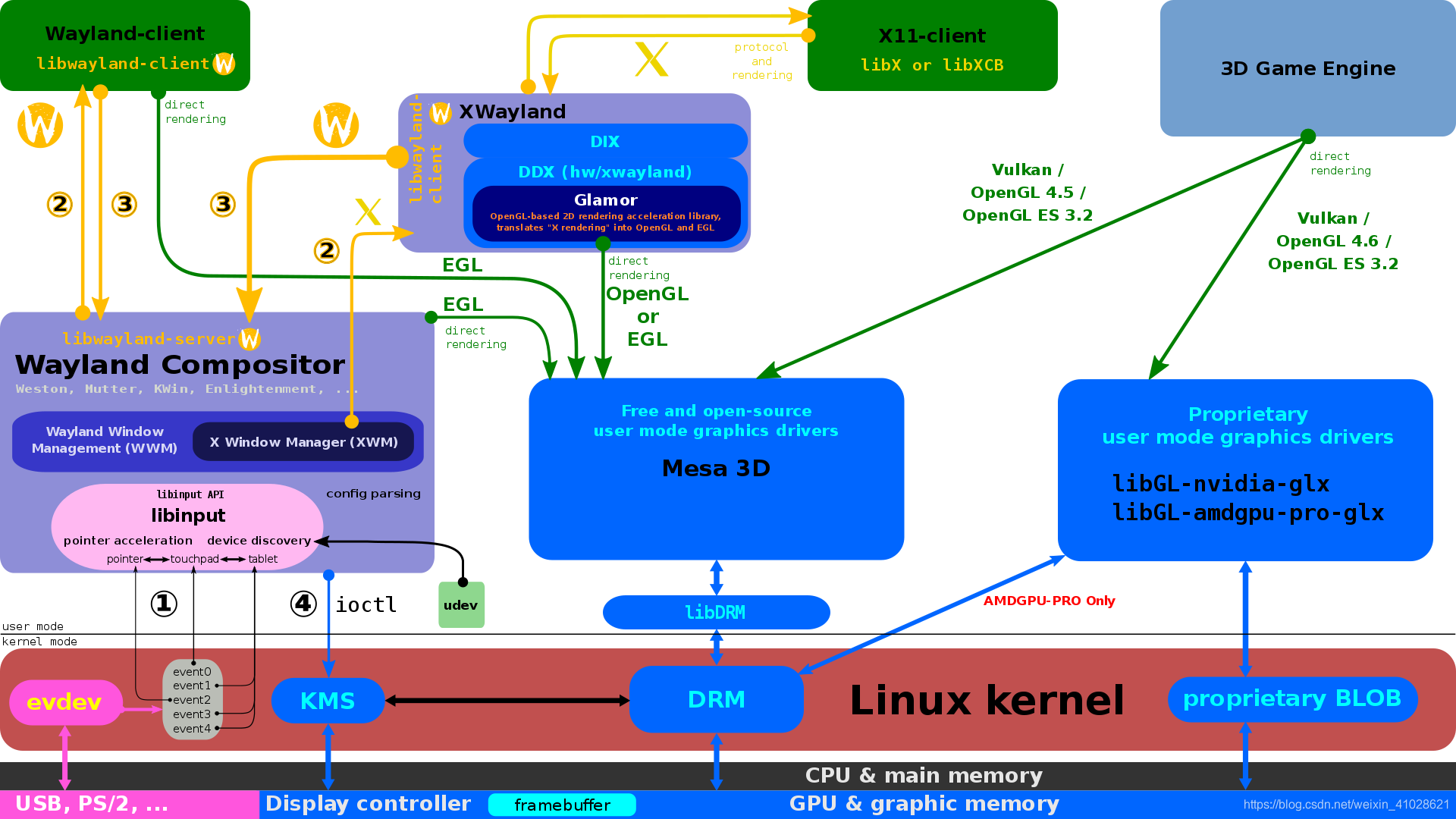

二、PCB板的叠层设计

- 叠层设计遵从以下规定:

- ① 每个走线层都必须有一个邻近的参考层(电源或地层);

- ② 邻近的主电源层和地层要保持最小间距,以提供较大的耦合电容。

1.两层板的叠层

对于两层板来说,由于板层数量少,已经不存在叠层的问题。控制EMI辐射主要从布线和布局来考虑;

单层板和双层板的电磁兼容问题越来越突出。造成这种现象的主要原因就是因是信号回路面积过大,不仅产生了较强的电磁辐射,而且使电路对外界干扰敏感。

要改善线路的电磁兼容性,最简单的方法是减小关键信号的回路面积。

关键信号:从电磁兼容的角度考虑,关键信号主要指产生较强辐射的信号和对外界敏感的信号。能够产生较强辐射的信号一般是周期性信号,如时钟或地址的低位信号。对干扰敏感的信号是指那些电平较低的模拟信号。

单、双层板通常使用在低于10KHz的低频模拟设计中:

- ① 在同一层的电源走线以辐射状走线,并最小化线的长度总和;

- ②走电源、地线时,相互靠近;在关键信号线边上布一条地线,这条地线应尽量靠近信号线。这样就形成了较小的回路面积,减小差模辐射对外界干扰的敏感度。当信号线的旁边加一条地线后,就形成了一个面积最小的回路,信号电流肯定会取道这个回路,而不是其它地线路径。

- ③ 如果是双层线路板,可以在线路板的另一面,紧靠近信号线的下面,沿着信号线布一条地线,地线尽量宽些。这样形成的回路面积等于线路板的厚度乘以信号线的长度。

2.四层板的叠层

(1)PCB层介绍

- AD19默认的Layer(层)有13个,层介绍如下表:

| Layer | 含义 |

|---|---|

| Top Layer | 顶层,该层通常用于布线 |

| Bottom Layer | 底层,该层通常用于布线 |

| Mechanical 1 | 机械层1,该层可用于设计PCB的机械外形 |

| Top Overlay | 顶层丝印层,顶层元器件丝印、字符 |

| Bottom Overlay | 底层丝印层,底层元器件丝印、字符 |

| Top paste | 顶层助焊层,一般用于贴片元件的SMT回流焊过程时上锡膏 |

| Bottom Paste | 底层助焊层,一般用于贴片元件的SMT回流焊过程时上锡膏 |

| Top Solder | 顶层阻焊层,敷设阻焊绿油,以防止铜箔上锡,保持绝缘 |

| Bottom Solder | 底层阻焊层,敷设阻焊绿油,以防止铜箔上锡,保持绝缘 |

| Drill Guide | 钻孔定位层,焊盘及过孔的钻孔的中心定位坐标层 |

| Keep-Out Layer | 禁止布线层,可用于设计PCB机械外形 |

| Drill Drawing | 钻孔图纸层,焊盘及过孔的钻孔孔径尺寸描述层 |

| Multi-Layer | 通孔层,抽象的层,仅显示过孔和焊盘 |

- 四层板,顾名思义就是有四层的电路板,它通常由顶层信号层、中间层(内电层)Power层、中间层GND层和底层信号层组成。顶层信号层Top Layer和底层信号层Bottom Layer已经存在,中间层的两层需要添加。

(2)四层板的层叠顺序:SIG-GND-PWR -SIG

- 这种层叠顺序通常应用于板上芯片较多的情况。此方案可得到较好的SI性能,但对于EMI性能来说并不是很好,主要通过走线及其他细节来控制。

- 注意:地层放在信号最密集的信号层的相连层,有利于吸收和抑制辐射;增大板面积,体现20H规则。

(3)层叠设计步骤:

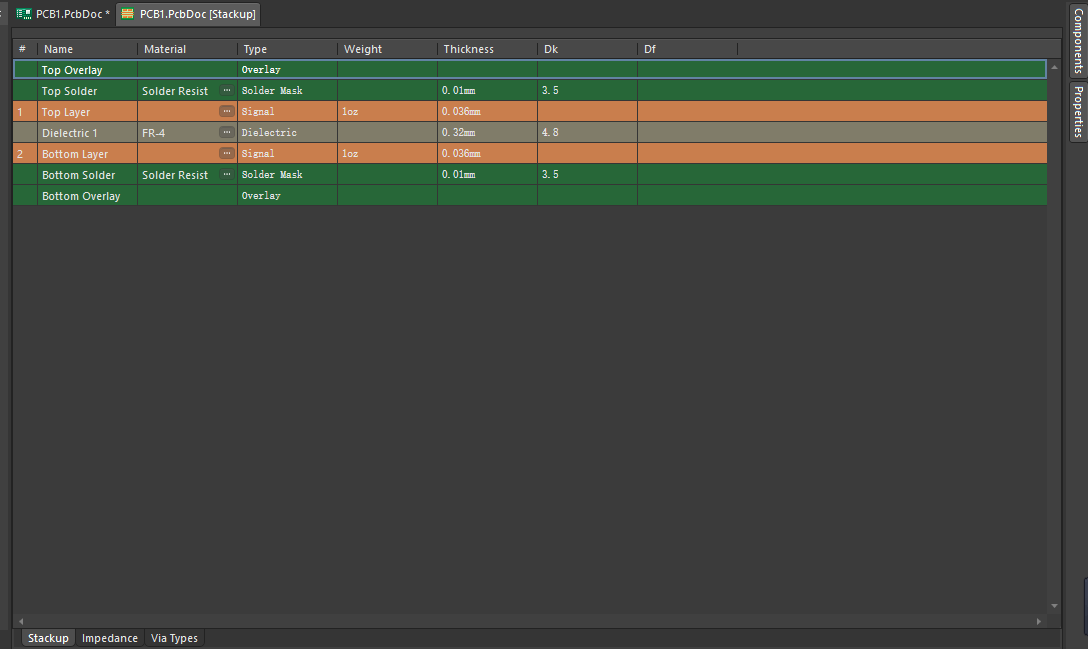

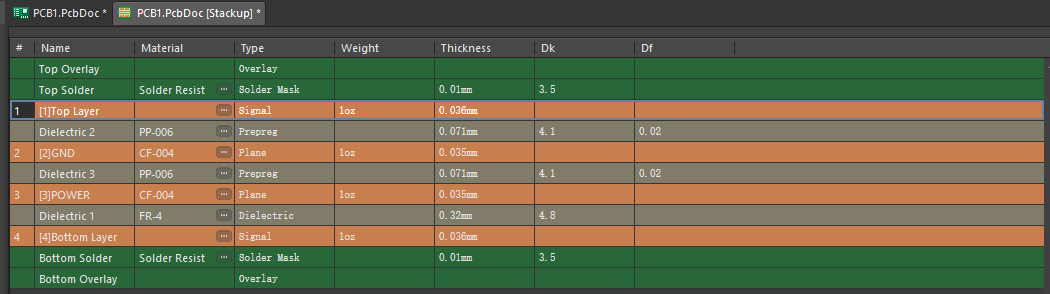

- 步骤1:快捷键D+K,打开层叠管理器

注意:Dielectric 是电介质,介于Top Layer与Bottom Layer之间的绝缘材料,不用进行操作。四层板设计需要在Top Layer与Bottom Layer之间添加两层中间层。

- 步骤2:如下图所示,创建第一个负片层,①选择Top Layer所在行 → ②右键选择Insert layer below → ③选择Plane

中间层选择类型,见下表:

| 可选类型 | 含义 |

|---|---|

| Signal | 信号层,又叫正片层,同Top Layer和Bottom Layer |

| Plane | 负片层,专用于4层板以上的电源或地走线 |

| Core | 制作板的基础材料,双面包铜,具有一定的硬度及厚度 |

| Prepreg | 用于多层印制板的内层导电图形的粘合材料及绝缘材料 |

| Copper plating | 镀铜(不选) |

注意:通常,四层板的GND层选择负片层,POWER层选择负片层或信号层。

- 步骤3:重复步骤2,创建第二个负片层,选中Top Layer双击,重命名,重命名结果如下图。

- 步骤4:设置GND层和POWER层的内缩值,GND层内缩20mil,POWER层内缩60mil;

GND层内缩设置:

① 选择GND层 → ② 单击Panels → ③ 选择Properties → ④ 取消勾选Stack Symmetry → ⑤ 设置Pullback distance值为20mil。

同理,POWER层内缩:

- 步骤5:四层板布线

① 与两层板布线方式相同,在Top层和Bottom层布线,而GND层和POWER层禁止布线,需要连接对应的地和电源网络;

② 层与层之间的连接是通过过孔/焊盘实现的,多层板同样如此。放置元器件的Top Layer或Bottom Layer先把电源和GND(或其他的走线)通过过孔引出;

③ 通过过孔/焊盘引出的电源和地网络,在Top和Bottom不需要走线,此处不需要走线的电源和地,指的是POWER层网络和GND层网络连接的电源和地。

三、规则设计

- 画好的四层板外发打板时,规则设计可参考嘉立创4层板的板层及板厚设计:

- ① 通常四层板板厚设置为1.6mm或2mm;

- ② 板材设置为FR-4;

- ③ 层压顺序选择“按原单处理”;

- ④ 层压结构参考下图:

- ⑤ 其余选项参照两层板打板选项设置。

参考资料

参考资料1: Altium Designer(AD)软件使用记录05-PCB叠层设计

参考资料2: AD_PCB:四层或多层板最优层叠顺序选择

参考资料3: 从零开始的硬件之路20:使用AD绘制四层板的主要步骤