Verilog中的条件语句\多分支语句\循环语句

文章目录

- Verilog中的条件语句\多分支语句\循环语句

- 一、背景

- 二、if-else

- 2.1 标准结构

- 2.2 例子

- 三、case-endcase

- 3.1 标准结构

- 3.2 例子

- 3.2.1 三路选择器的`case`部分,如下:

- 3.2.2 `casez`的四路选择器,如下:

- 四、for

- 4.1 标准结构

- 4.2 例子

- 五、repeat

- 5.1 标准结构

- 5.2 例子

- 5.2.1 循环11次

- 5.2.2 存储8个数据

- 六、forever

- 6.1 标准结构

- 6.2 例子

- 6.2.1 产生一个时钟

- 6.2.2 实现一个时钟边沿控制的寄存器间数据传输功能

一、背景

由于初学Verilog,故写篇笔记记录Verilog中的 if-else、case-endcase、for、while、repeat、forever语法,以及例子。

二、if-else

定个标准,每个if-else的出现都要有begin-end语句。

2.1 标准结构

条件语句标准使用结构:

if (condition1) begin

true_statement1 ;

end

else if (condition2) begin

true_statement2 ;

end

else if (condition3) begin

true_statement3 ;

end

else begin

default_statement ;

end

2.2 例子

二输入选择器:

if(en) begin

if(sel == 2'b1) begin

sout = p1 ;

end

else begin

sout = p0 ;

end

end

三、case-endcase

case 语句是一种多路条件分支的形式,可以解决 if 语句中有多个条件选项时使用不方便的问题。casex、 casez 语句是 case 语句的变形,用来表示条件选项中的无关项。

3.1 标准结构

case(case_expr)

condition1: true_statement1 ;

condition2: true_statement2 ;

……

default: default_statement ;

endcase

casex 用 “x” 来表示无关值,casez 用问号 “?” 来表示无关值。

两者的实现的功能是完全一致的,语法与 case 语句也完全一致。

但是 casex、casez 一般是不可综合的,多用于仿真。

例如用 casez 语句来实现一个 4bit 控制端的 4 路选择选择器。

3.2 例子

3.2.1 三路选择器的case部分,如下:

case(sel)

2'b00: sout_t = p0 ;

2'b01: sout_t = p1 ;

2'b10: sout_t = p2 ;

default: sout_t = p3 ;

endcase

3.2.2 casez的四路选择器,如下:

module mux4to1(

input [3:0] sel ,

input [1:0] p0 ,

input [1:0] p1 ,

input [1:0] p2 ,

input [1:0] p3 ,

output [1:0] sout);

reg [1:0] sout_t ;

always @(*)

casez(sel)

4'b???1: sout_t = p0 ;

4'b??1?: sout_t = p1 ;

4'b?1??: sout_t = p2 ;

4'b1???: sout_t = p3 ;

default: sout_t = 2'b0 ;

endcase

assign sout = sout_t ;

endmodule

四、for

4.1 标准结构

for 循环语法格式如下:

for(initial_assignment; condition ; step_assignment) begin

…

end

4.2 例子

// for 循环语句

integer i ;

reg [3:0] counter2 ;

initial begin

counter2 = 'b0 ;

for (i=0; i<=10; i=i+1) begin

#10 ;

counter2 = counter2 + 1'b1 ;

end

end

五、repeat

repeat的功能是执行固定次数的循环,它不能像 while循环那样用一个逻辑表达式来确定循环是否继续执行。repeat循环的次数必须是一个常量、变量或信号。如果循环次数是变量信号,则循环次数是开始执行 repeat循环时变量信号的值。即便执行期间,循环次数代表的变量信号值发生了变化,repeat执行次数也不会改变。

5.1 标准结构

repeat循环语法格式如下:

repeat (loop_times) begin

…

end

5.2 例子

5.2.1 循环11次

// repeat 循环语句

reg [3:0] counter3 ;

initial begin

counter3 = 'b0 ;

repeat (11) begin //重复11次

#10 ;

counter3 = counter3 + 1'b1 ;

end

end

5.2.2 存储8个数据

always @(posedge clk or negedge rstn) begin

j = 0 ;

if (!rstn) begin

repeat (8) begin

buffer[j] <= 'b0 ; //没有延迟的赋值,即同时赋值为0

j = j + 1 ;

end

end

else if (enable) begin

repeat (8) begin

@(posedge clk) buffer[j] <= counter3 ; //在下一个clk的上升沿赋值

j = j + 1 ;

end

end

end

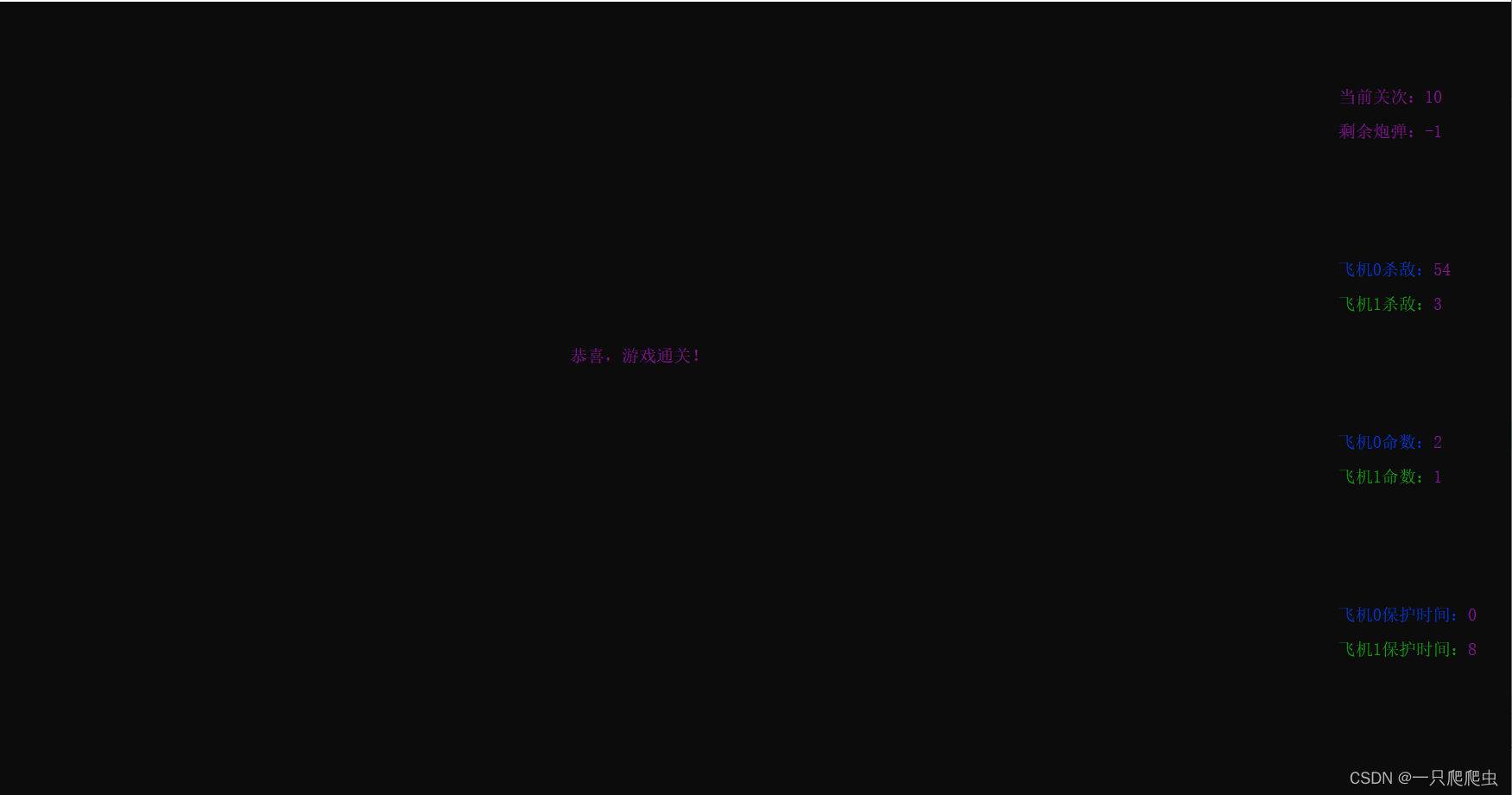

仿真结果如下图。

由图可知,rstn 拉高时,buffer的 8 个向量同时赋值为 0。

第二个时钟周期后,buffer依次被counter3赋值,实现了连续存储 8 个数据的功能。

六、forever

forever语句表示永久循环,不包含任何条件表达式,一旦执行便无限的执行下去,系统函数$finish可退出forever。

forever相当于while(1)。

通常,forever 循环是和时序控制结构配合使用的。

6.1 标准结构

forever循环语法格式如下:

forever begin

…

end

6.2 例子

6.2.1 产生一个时钟

reg clk ;

initial begin

clk = 0 ;

forever begin

clk = ~clk ;

#5 ;

end

end

6.2.2 实现一个时钟边沿控制的寄存器间数据传输功能

reg clk ;

reg data_in, data_temp ;

initial begin

forever @(posedge clk) data_temp = data_in ;

end