文章目录

- 一、概念

- 1.0、计算机通讯框架OSI 7层模型

- 1.1、根据数据排布传输方式---并行通信 / 串行通信

- 1.2、根据数据传输方向与时间关系分类----单工通信/半双工通信/全双工通

- 1.3、半双工通信的 应答与流控机制----如I2C,通过开漏线与特性 实现

- 1.4、根据收发方时间基准是否相同 ----异步传输(如Uart)/同步传输(如I2C)

- 二、通讯协议演变分析

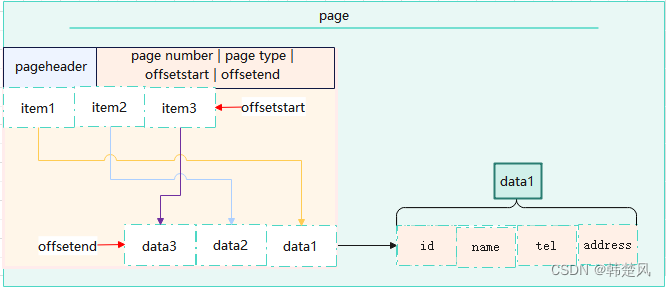

- 2.1 阶段一、最基础的版级器件通信

- 单线Data传输,最多实现半双工,速率提前约定(举例Swire)

- 双线Data传输(Uart协议)实现全双工,速率提前约定

- 一根Data+一根CLK线(I2C协议)实现 半双工 可变速率 多对多

- 两个Data线+一个CLK线+一个CS片选(SPI)实现全双工 速率可变 简化寻址

- 2.1 阶段二、长距离&高速&高稳定性&抗干扰 通讯机制

- 长距离传输抗干扰方案----同轴电缆(屏蔽层) 与 双绞线(差分消除)

- 长距离传输降低成本,消除时钟线方案----CDR时钟恢复 与 4B/5B、8B/10B编码

- 长距离传输 提升传输速率方案----信号调制技术RAM(千兆以太网)

- 高速传输 EMI(电磁干扰)降低方案----信号加扰与解扰

- 参考

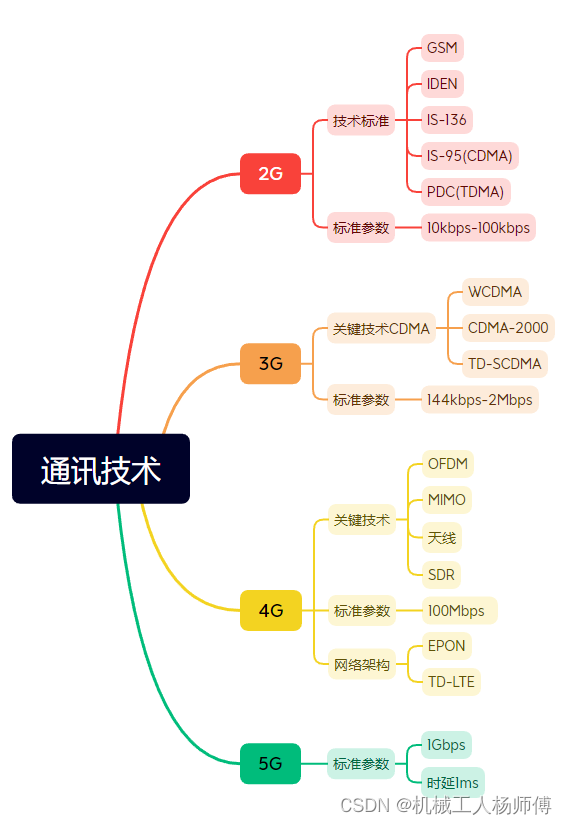

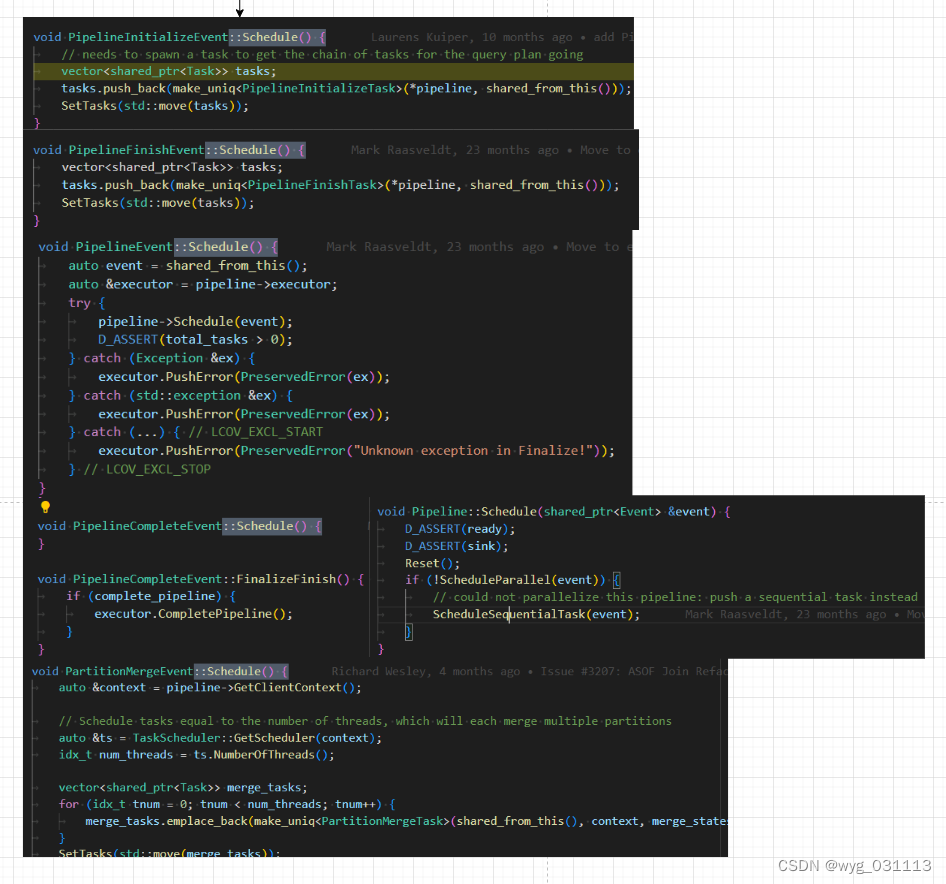

嵌入式开发经常会接触各种通讯协议,如I2C、Uart、SPI等,梳理协议的演变过程;这里我们主要讨论的是 OSI 7层模型 中的 物理层(如通讯速率、电压范围、包含几根线)和 数据链路层(关于一帧数据内部结构定义 与 数据拆分)演变思路 ;

一、概念

1.0、计算机通讯框架OSI 7层模型

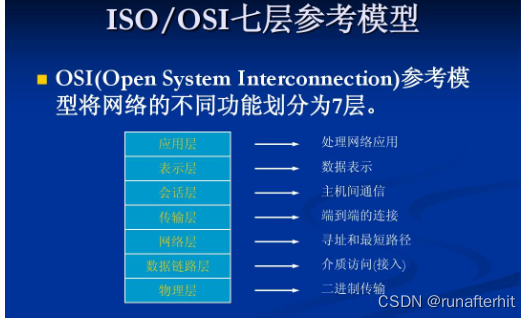

开放系统互联(OSI)模型是由国际标准化组织(ISO)于1984年提出的一种标准参考模型,是一种关于由不同供应商提供的不同设备和应用软件之间的网络通信的概念性框架结构。它被公认为是计算机通信和 internet 网络通信的一种基本结构模型。

1.1、根据数据排布传输方式—并行通信 / 串行通信

典型通信方式可以分为并行通信和串行通信。串行通信定义:串行通信是指利用一条传输线将数据一位位地顺序传送。传输一个字节(8个位)的数据时,串口是将8个位排好队,逐个地在1条连接线上传输。并行通信定义:并行通信是指利用多条传输线将一个数据的各位同时传送。并行通信8个位)的数据时,并口是将8个位一字排开,分别在8条连接线上同时传输。

1.2、根据数据传输方向与时间关系分类----单工通信/半双工通信/全双工通

数据在线路上的传送方式可以分为单工通信、半双工通信和全双工通信三种。

单工通信:是指消息只能单方向传输的工作方式,发送端和接收端的身份是固定的。

半双工通信:是指数据可以沿两个方向传送,但同一时刻一个信道只允许单方向传送,因此又被称为双向交替通信。

全双工 :是指在通信的任意时刻,线路上可以同时存在A到B和B到A的双向信号传输,通信系统的每一端都设置了发送器和接收器。

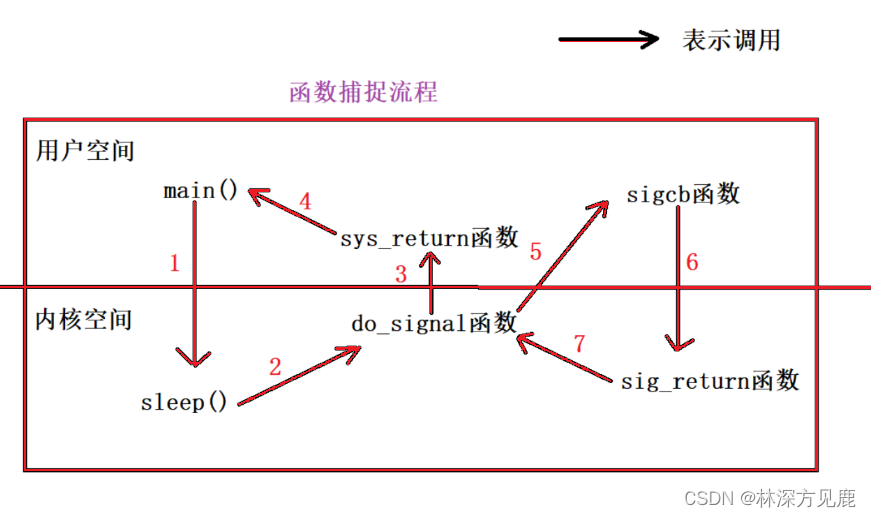

1.3、半双工通信的 应答与流控机制----如I2C,通过开漏线与特性 实现

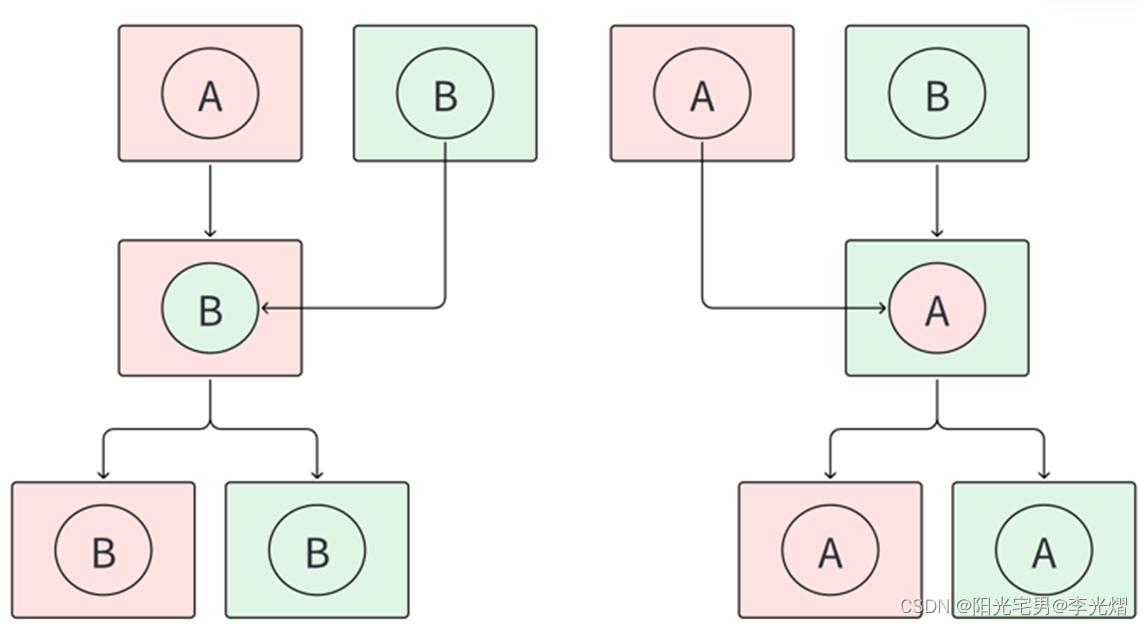

在半双工通讯场景,由于数据发送方向在变化,需要进行 流控(谁来发)和 应答(是否受到)来保证数据传输正确。I2C总线是使用的两个双向开漏线DATA/CLK(可以简单理解 为 线上电平 通过上拉电阻默认拉高,Slave和Master两边谁都可以把线拉低),通过线与的方式决定电平,当Master在Data线上发送完一个字节后,Slave主动拉低Data线来传输Ack表示接受到了,如果Slave通过Data线回传一个字节Master也通过拉低Data线来Ack表示接受,如果没有做好接受数据准备,Slave可以拉低CLK来表示没有准备好。

1.4、根据收发方时间基准是否相同 ----异步传输(如Uart)/同步传输(如I2C)

同步就是双方有一个共同的时钟,当发送时,接收方同时准备接收(比如I2C、SPI)。当时钟线一直拉高时可视为无数据发送,为了表示数据开始和结束,通常可以按时钟线和数据线配合来描述标志,比如I2C约定了 帧数据开始(时钟SCL高 SDA下降沿)、结束(时钟SCL高 SDA上升沿)。异步双方不需要共同的时钟,也就是接收方不知道发送方什么时候发送,所以在发送的信息中就要有提示接收方开始接收的信息,如开始位,结束时有停止位(如UART约定了 从持续高电平到第一个拉低谷底周期为开始位)。

二、通讯协议演变分析

备注:在讨论数据线路时不计算地线(有时地线不一定是 具体的线路)

2.1 阶段一、最基础的版级器件通信

单线Data传输,最多实现半双工,速率提前约定(举例Swire)

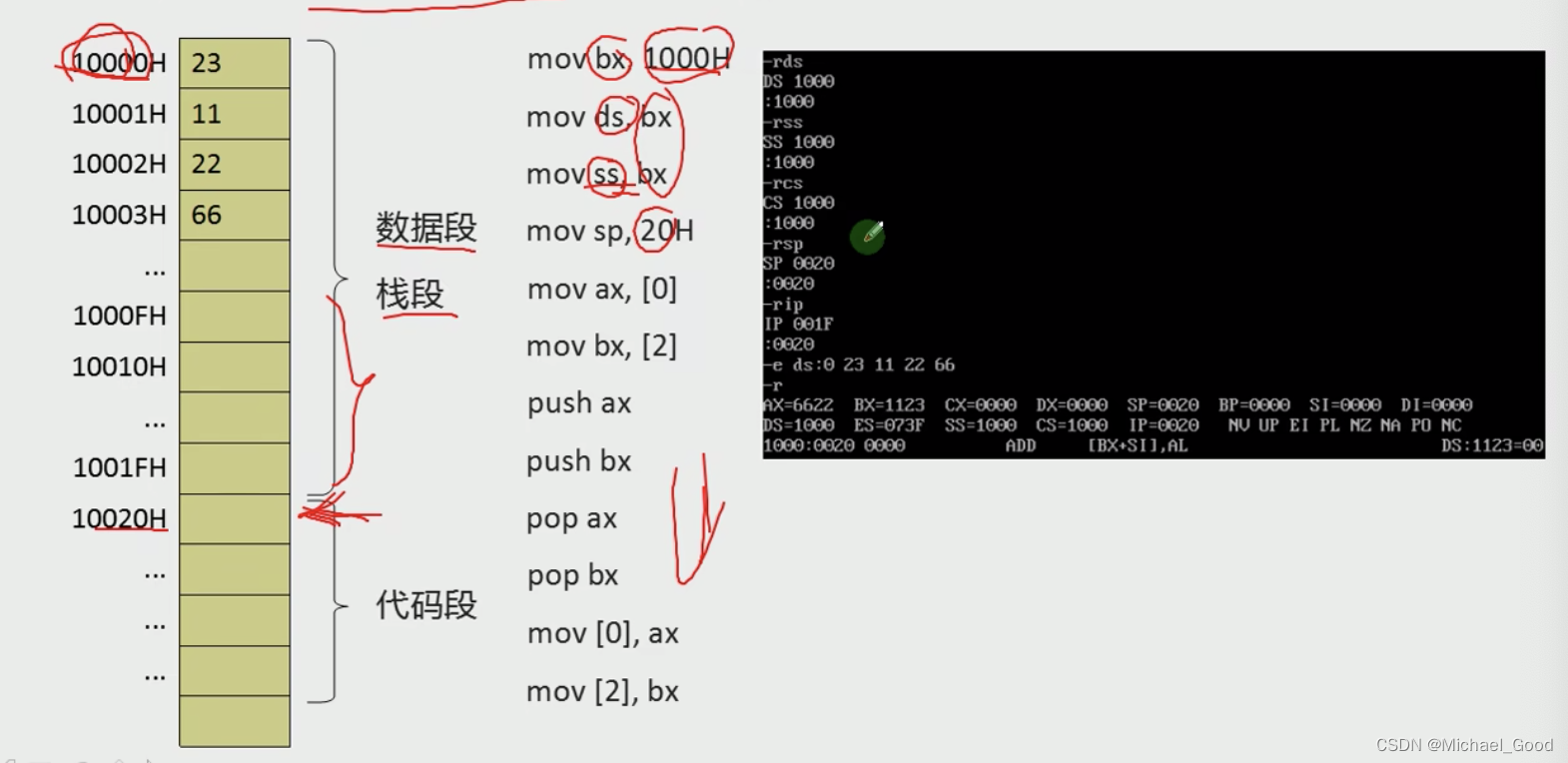

由于只有一根线,同一时刻只能有一方发数据,常用单工通信,最多实现半双工。由于没有时钟线,速率只能提前约定好,接受方以什么样的时钟频率采样 线上的电平,并且由于没有时钟同步信号,需要约定好什么时候算帧数据开始和结束。

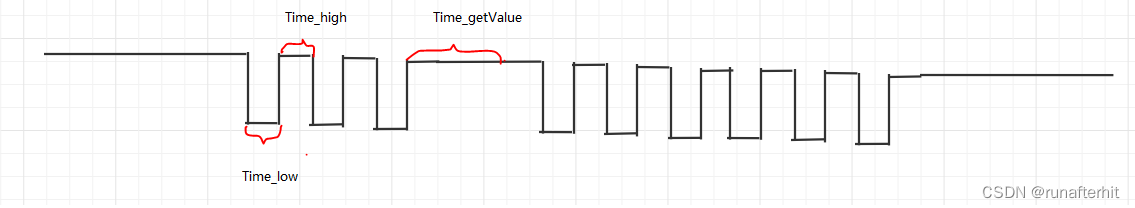

以单线传输Swire协议(基于SC6104一款PMIC供电IC)举例:SWIRE是单线单工通信,默认高点平,Master通过发送脉冲数 对 Slave器件进行控制,不同的脉冲个数代表不同含义(Datasheet有详细注释,比如发送4个脉冲是设置某个电压到xxx赋值) 。为了识别脉冲数量主要提前约定了3个Time,单个脉冲高低电平时间范围T_high\T_low和一次脉冲数量发送结束后最低持续高电平时间T_getValue。

如上图,当Slave设备识别到Data拉低就开始统计 拉低时间 是否为有效TimeLow,开始统计数据帧,当拉高遇到一个有效的TimeHign就累计一个脉冲数 直到遇到某次拉高超过TimeGetValue就表示一帧数据结束,这段时间累计的脉冲数就是一次命令帧。

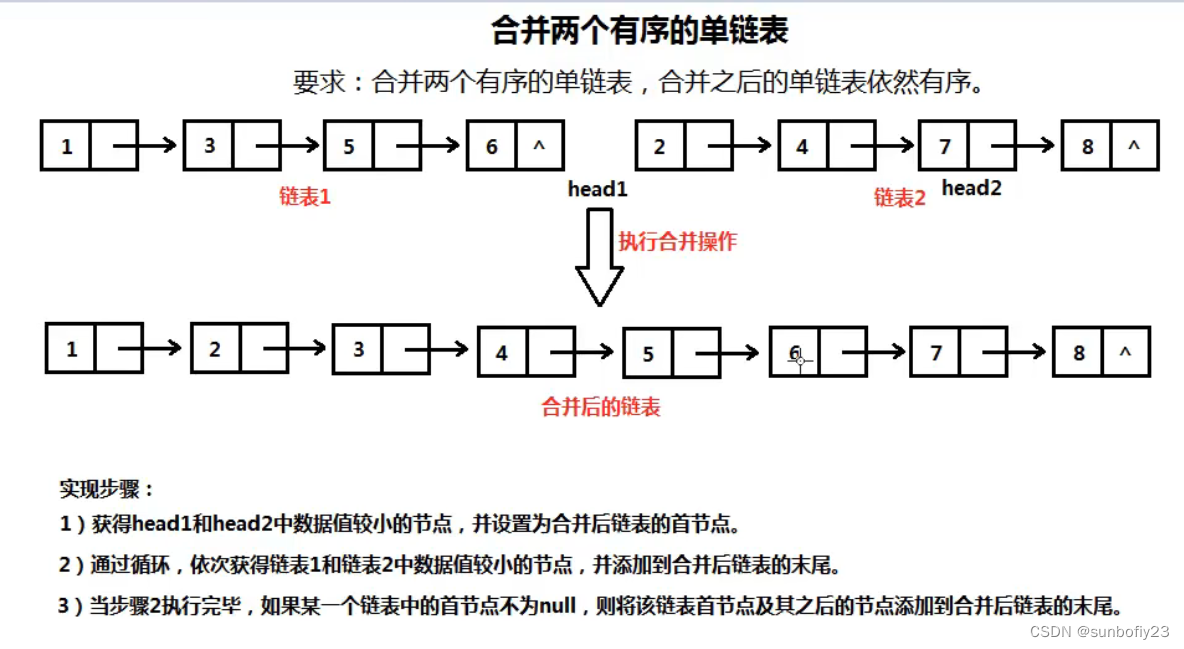

双线Data传输(Uart协议)实现全双工,速率提前约定

为了解决单线最多半双工问题,添加一个Data线可以实现全双工,但是速率仍然需要提前约定好,如Uart串口协议;

阅读:UART串口协议简单总结 https://blog.csdn.net/runafterhit/article/details/114990221

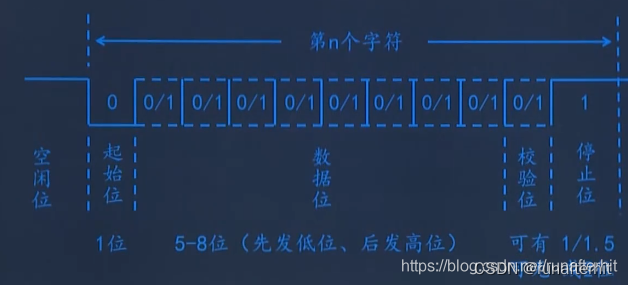

TxD、RxD数据线以位为最小单位传输数据,而帧由具有完整意义的、不可分割的若干位组成,包含开始位、数据位、校验位(需要的话)和停止位。发送数据之前,UART之间要约定好数据的传输速率(即每位所占据的时间,其倒数称为波特率)、数据的传输格式(即有多少个数据位、是否使用校验位、是奇校验还是偶校验、有多少个停止位)。

一根Data+一根CLK线(I2C协议)实现 半双工 可变速率 多对多

为了解决速率需要提前约定的问题,可以通过时钟CLK线来解决。Slave按照Master发送的时钟CLK线 边沿进行Data采样,这样速率就有了依据。当时钟线一直拉高时可视为无数据发送,为了表示数据开始和结束,通常可以按时钟线和数据线配合来描述标志,这样理论上对单次帧数据长度可以做到任意BIT。

阅读:I2C协议简单总结 https://blog.csdn.net/runafterhit/article/details/114935007

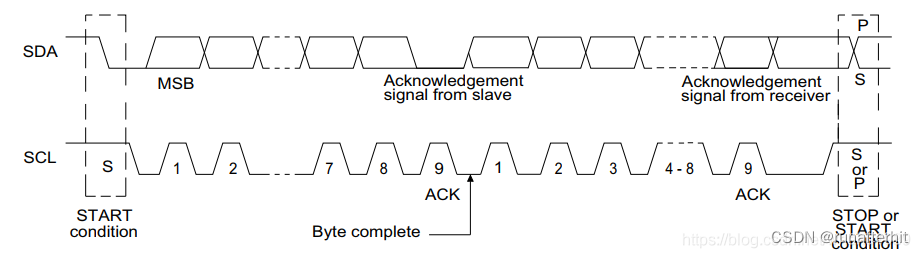

I2C约定了 如何识别帧数据开始(时钟SCL高 SDA下降沿)、结束(时钟SCL高 SDA上升沿),在开始和结束中间 读取数据,时钟SCL高电平 数据SDA读取有效,约定了 传输每次都是1个字节(8位),先传送最高位,每一个被传送的字节后面都必须跟随一位应答位(即一帧共有9位)。

由于I2C需要支持一个Master上对接多个Slave设备,因此需要传递设备地址来进行寻址。 I2C总线是使用的两个双向开漏线,通过线与的方式决定电平 完成流控和应答。当Master发送的第一个字节是目标从设备地址,当有对应地址的Slave设备在线路上时要进行拉低Data线Ack响应,建立连接(未建立连接的Slave设备忽略后续全部信息)。然后在Data线上发送完一个字节后,Slave主动拉低Data线来传输Ack表示接受到了,Slave可以拉低CLK来表示没有准备好。

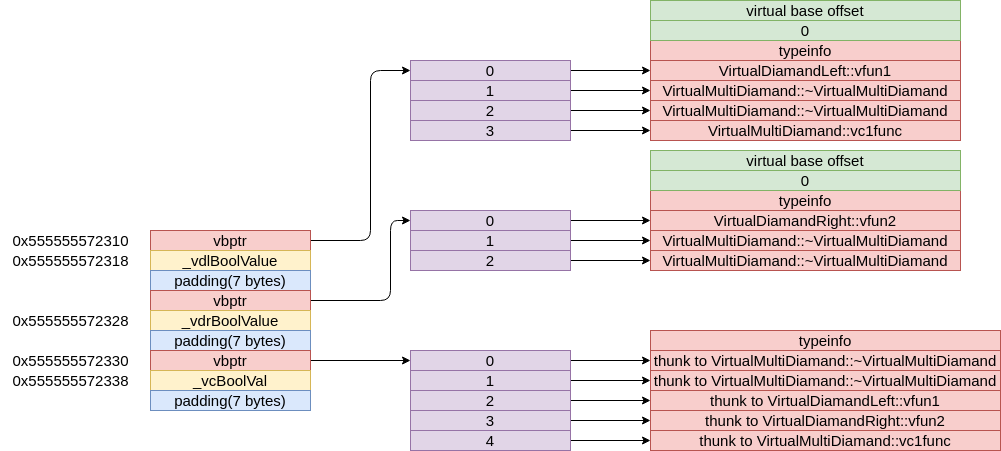

两个Data线+一个CLK线+一个CS片选(SPI)实现全双工 速率可变 简化寻址

基于I2C,我们可以再引入一个Data线来实现全双工,同时再添加一个CS片选线来使能不同的Slave设备 来省去多个Slave设备的寻址问题,让Data线的传输效率更高。

阅读:SPI协议简单总结 https://blog.csdn.net/runafterhit/article/details/115007730

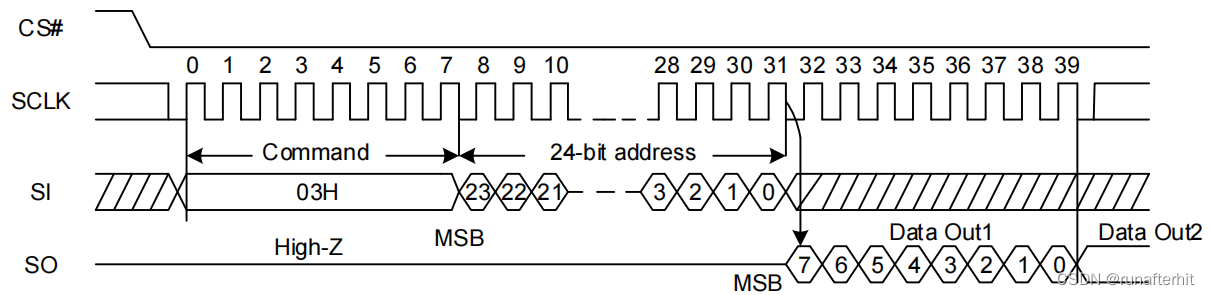

SPI 接口通常由四根线组成,分别是提供时钟的 SCLK,提供数据输出的 MOSI(Master Out Slave In),提供数据输入的MISO(Master In Slave Out)和提供片选信号的 CS。同一时刻只能有一个SPI 设备处于工作状态,即多个 CS 信号中某时间只能有一个有效。为了适配不同的外设 ,SPI 支持通过寄存器来配置片选信号和时钟信号的极性和相位。

2.1 阶段二、长距离&高速&高稳定性&抗干扰 通讯机制

上面阶段一的UART/I2C/SPI基本都是在板级的器件间通讯,实现共地简单,速率也偏低。

当传输距离超过1米以上 并且速率更高时,每个单线传输信号容易受到干扰,同时高频信号容易对外部产生电磁干扰。

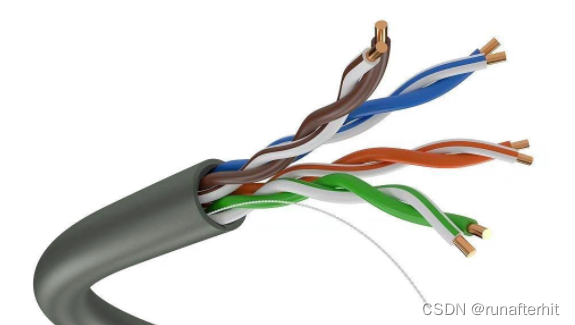

长距离传输抗干扰方案----同轴电缆(屏蔽层) 与 双绞线(差分消除)

1)同轴电缆:通过添加屏蔽层,把传输信号的电磁场全部限制在屏蔽层内部。缺点是 体积、成本、抗弯曲不够优秀;

2)双绞线 :用两根线传输极性相反的差模型号,用两根线的差分电平来表示一个信号,同时把两根线扭绞到一起。外界的干扰同时均匀作用在量根线上,被差分电平消除。同时螺旋缠绕的两根线由于极性相反,产生的磁场也会相互抵消,降低对外的干扰。

长距离传输降低成本,消除时钟线方案----CDR时钟恢复 与 4B/5B、8B/10B编码

长距离传输必须想办法减少必要的线路,消除时钟线的一种典型方案就是CDR;

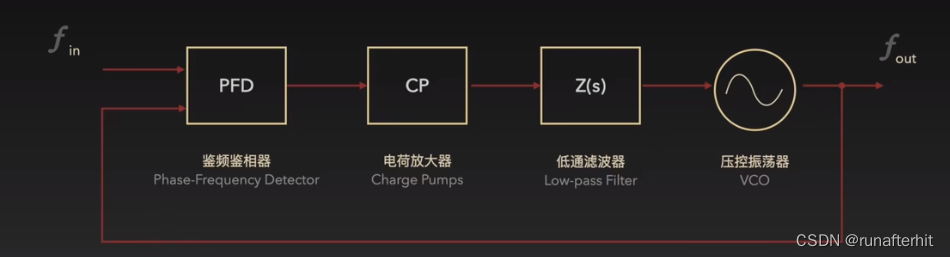

CDR:clock data recovery基本原理 可以理解为通过对Data的边沿分析出时钟CLK信号频率与相位 。 发送方把Data数据 通过特定编码方式 产生更多的边沿(01之间切换),接收方利用本地产生的多相位时钟对数据多次采样,判断数据比特的边沿,并通过PLL将时钟边沿与其对齐,从而实现与数据同频率、同相位时钟的恢复。利用已同步时钟的最优相位对输入数据采样,使其实现最高的输入信噪比,并把采样结果作为已恢复数据输出。

4B/5B、8B/10B编码 就是一种产生更多Data边沿的算法。为了避免出现连续的0导致无法解析出有效时钟,通过添加额外的BIT产生新映射方式来得到更多的数据边沿。

典型4B5B编码映射表如下,8B9B编码原理类似:

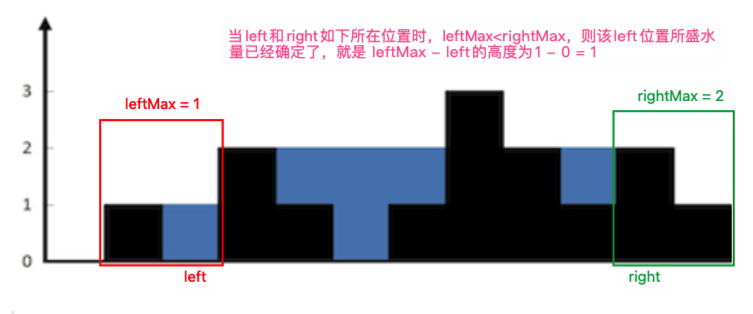

长距离传输 提升传输速率方案----信号调制技术RAM(千兆以太网)

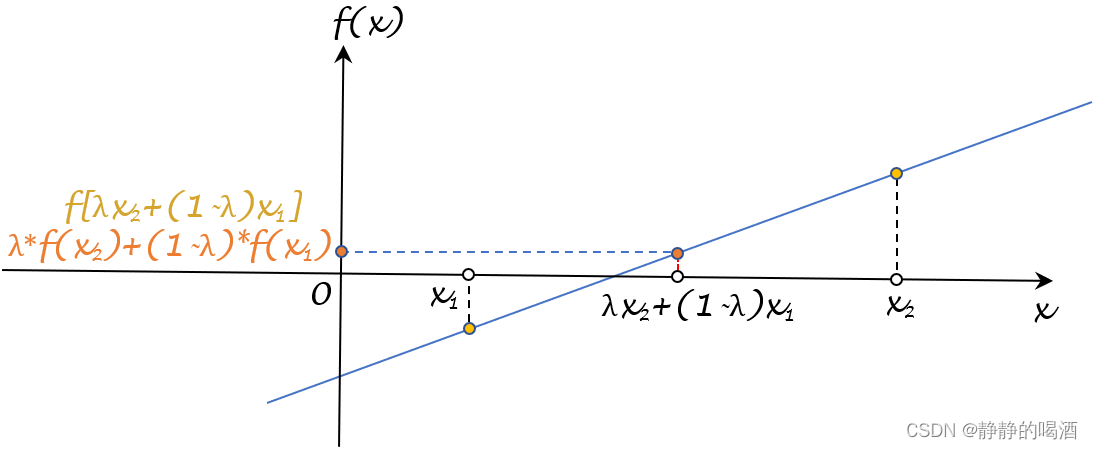

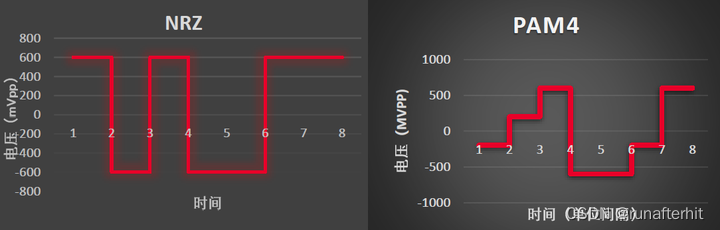

上面介绍的基本版级传输Data线只有高低两种点平,可以称之为一种NRZ 信号(不归零码):这是一种用于表示 0 和 1 比特的线路编码。

RAM信号调制技术 就是用一个电平体现多种幅度信息。PAM4信号有四个电压电平,每个幅度电平分别对应逻辑比特00、01、10和11。 换言之,PAM4编码的每个符号由2个比特组成,它们对应一个电压电平,即幅度。

在时钟速率不变的情况下,加入RAM调制技术后能传输数据带宽更大。

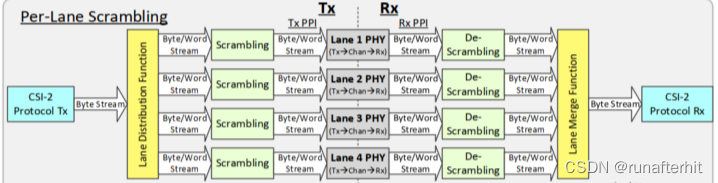

高速传输 EMI(电磁干扰)降低方案----信号加扰与解扰

在数字信号的传输中,发送端通常要加入扰码器,扰码的作用是改变数字信号的统计特性使其变成近似白噪声序列。因为输入的数字信号的频率较为集中,信号频谱的峰值过大,即能量过于集中,从而会产生电磁干扰效应。而白噪声序列的频率较为分散,相当于信号的能量较为分散,可以达到减少电磁干扰的目的。

如MIPI传输协议里面,TX端数据在分解到lane传输前都需要经过加扰器进行加扰,同理在Rx端需要解扰后使用;

参考

嵌入式通信的底层逻辑(上):https://www.bilibili.com/video/BV1ju411W7Q3

嵌入式通信的底层逻辑(下):https://www.bilibili.com/video/BV19o4y177gu

关于脉冲幅度调制(PAM)技术:https://zhuanlan.zhihu.com/p/355363778

MIPI CSI-2笔记(12) -数据加扰 :https://blog.csdn.net/vivo01/article/details/126609451