文章目录

- 一,存储器

- 1.1 概述

- 1.1.1 半导体存储器的分类

- 按制造工艺:

- 易失性或挥发性存储器 / 不易失性或不挥发性存储器

- 按制造工艺:

- 1.1.2 半导体存储器的性能指标

- 1.1.3 半导体存储器的一般结构及组成

- 1.2 随机存取存储器 RAM

- 1.2.1 静态RAM

- 1.2.2 动态RAM

- 1.2.3 RAM存储容量扩展方法 ***==重点==

- 位扩展

- 字扩展

- 字位扩展

- 1.2.4 RAM 存储器与CPU连接 ***==重点==

- (1)数据总线的连接

- (2)地址总线的连接

- (3)控制总线的连接

- 1.2.5 译码

- 1.3 只读存储器 ROM(略)

- 典型 EEPROM 芯片有:AT24系列 AT24C04

- 1.4 高速缓冲存储器 Cache(略)

一,存储器

新型计算机的存储器组成可分为:CPU寄存器,高速缓冲寄存器,主存储器(简称内存/主存),辅助存储器(简称辅存/外存)。

内存储器由半导体芯片组成,依赖于电来维持信息的保存状态。

外存储器通常是磁性介质,能长期保存信息,不依赖电。

高速缓冲(Cache),解决CPU 与内存之间的速度匹配问题。

1.1 概述

半导体存储器优点:集成度高,速度快,功耗低,价格便宜,可靠性强,使用方便

=>已成为微型计算机的最主要的存储器

使用存储器要考虑的问题:

① 易失性;

② 只读性;(ROM)

③ 存储容量;

④ 速度。

⑤ 功耗;

1.1.1 半导体存储器的分类

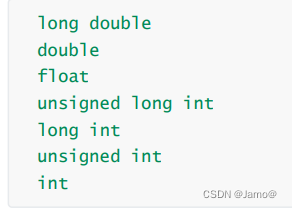

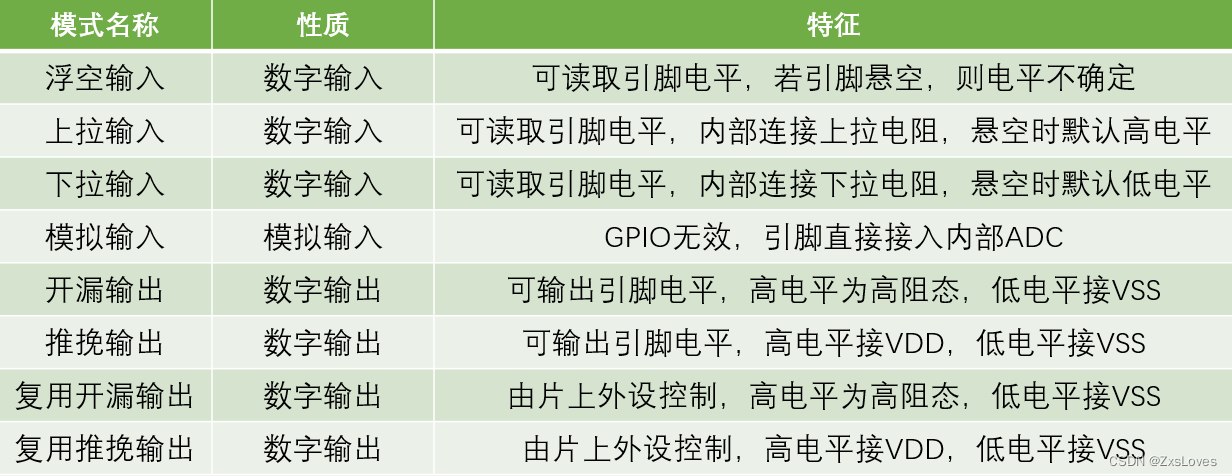

按制造工艺:

- 双极型存储器(TTL型晶体管):特点是存取速度快,但和MOS型比,集成度低,功耗大,成本高,常作为高速缓冲存储器(Cache)

- MOS型存储器

- 静态RAM

- 动态RAM

- EPROM

- E^2PROM( E 2 P R O M E^2PROM E2PROM)(EEPROM)

- Flash Memory

- 速度较双极型慢,但集成度高,功耗低,价格便宜,是构成微型机内存的主要半导体存储器件。

易失性或挥发性存储器 / 不易失性或不挥发性存储器

断电后会丢失信息,被称为易失性或挥发性存储器;

电源关闭后,存储的信息不会丢失被称为 非易失性或不挥发性存储器。

按制造工艺:

- 随机存取存储器RAM(Random Access Memory)(读写存储器)

信息可以按地址随时读出或写入。一般来说,RAM断电后会丢失信息,被称为易失性或挥发性存储器;但是现在有些RAM芯片内部带有电池,被称为 非易失性或不挥发性存储器。

RAM 分为静态RAM(SRAM)和动态RAM(DRAM):- 静态RAM 读写速度快,但集成度低,容量小,主要用作Cache或小系统的内存储器

- 动态RAM 读写速度慢于静态RAM,但集成度高,单片容量大,多用于存储量大的系统中。动态RAM利用电容的电荷存储效应来存储信息,必须周期性对其刷新。

- 只读存储器ROM(Read Only Memory)

信息是在使用前或制造时写入的,作为固定信息存储,正常运行时只能读,不能写。电源关闭后,存储的信息不会丢失,是 非易失性或不挥发性存储器。

常用来存放操作系统的核心程序(如BIOS)或用户固化的程序。

根据信息写入的方式,常用ROM类型有:- 掩膜式ROM(Masked ROM),简称ROM

- 可编程ROM(Programmable ROM),简称PROM

- 可擦除ROM(Erasable ROM),简称EPROM

- 电可擦除ROM(Electrically Rrasable ROM),简称 EEPROM 或 E 2 P R O M E^2PROM E2PROM

- 闪速存储器(Flash Memory)

1.1.2 半导体存储器的性能指标

存储容量,存取速度,功耗,可靠性,性能/价格比,功耗

存储容量表示方式:N * M:N表示存储单元数(也是地址线根数),M每单元的存储位数(也是数据线根数)

存储容量

=

2

M

×

N

存储容量 = 2^M×N

存储容量=2M×N

1.1.3 半导体存储器的一般结构及组成

- 存储矩阵

- 地址译码器

- 三状态双向缓冲器

- 控制逻辑电路

1.2 随机存取存储器 RAM

- 主要用来存放当前运行的程序,各种输入输出数据,中间运算结果,堆栈等

- 随时可读可写

- 掉电后内容全部丢失

- 静态RAM 和 动态 RAM

1.2.1 静态RAM

静态RAM以触发器为基本存储单元。

只需要写入一次,就能一直在,除非被重新写入覆盖

电路结构 P220 略

静态RAM 芯片举例:SRAM 2114,SRAM 6264

1.2.2 动态RAM

利用电容存储电荷的原理来保存信息,它将晶体管结电容的充电状态和放电状态分别作为1和0。DRAM的基本存储单元是单个场效应管及其极间电容

电路结构 P222 略

- 必须配备“读出再生放大电路”进行刷新(2ms内必须都被刷新一次),刷新按行进行。刷新方式有三:定时集中刷新,非同步的刷新,同步刷新方式。

- 每个基本存储单元存储二进制数一位

动态RAM 芯片举例:DRAM 2164

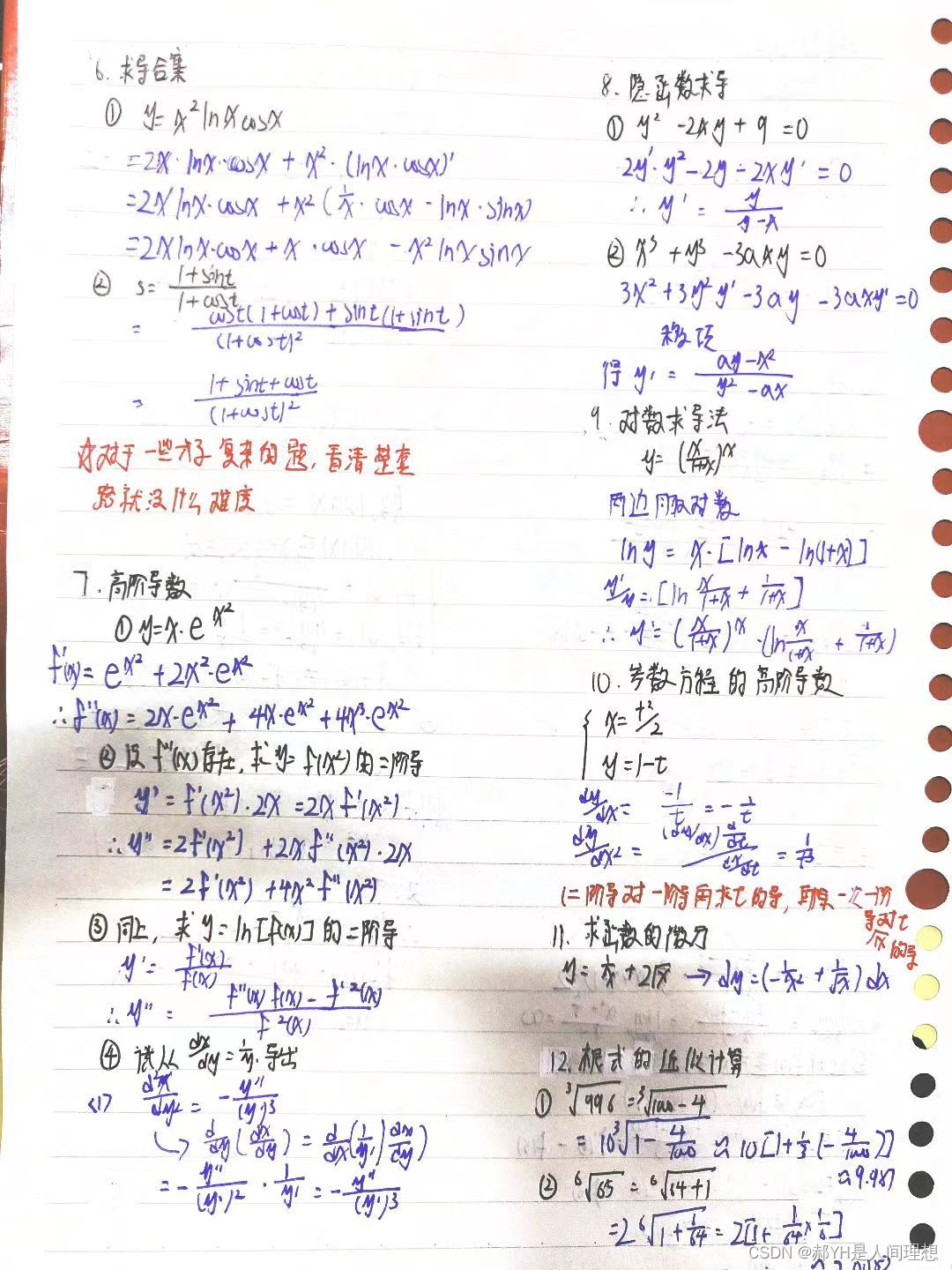

1.2.3 RAM存储容量扩展方法 ***重点

使用存储器需要考虑的两个问题:

- 使存储单元的位满足要求

- 使存储单元的个数满足要求

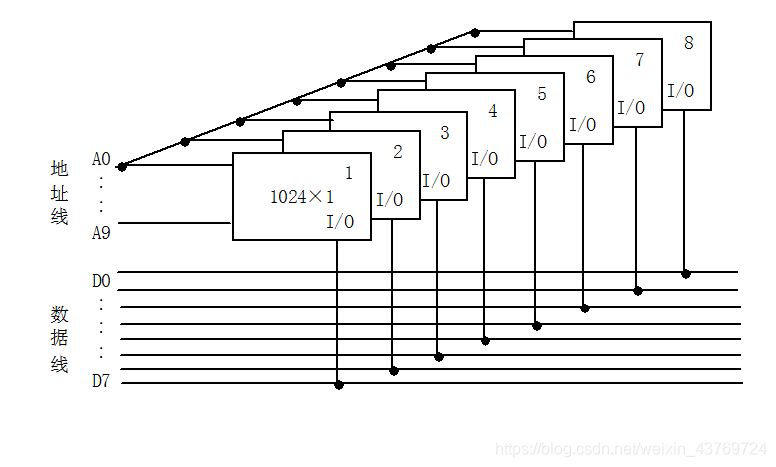

位扩展

只进行存储单元位数扩充。

把各存储芯片的地址线,片选信号线和读/写控制信号线相应地并联,各芯片数据线分别接到系统的数据线上。

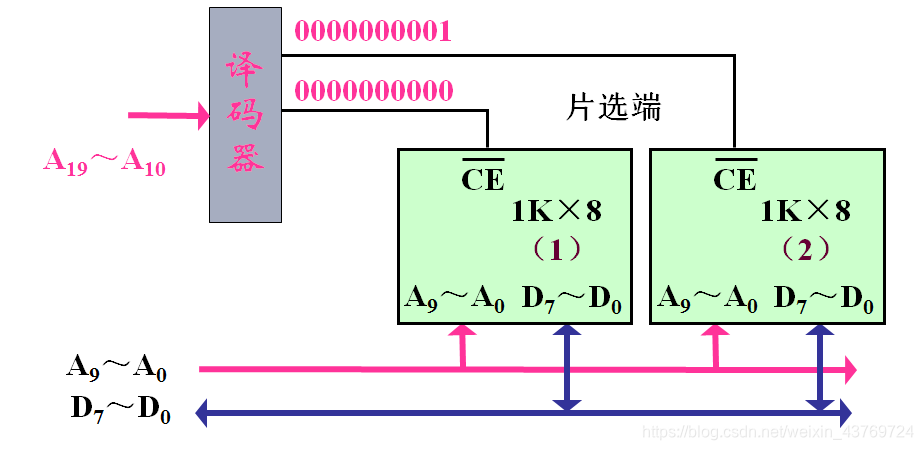

字扩展

只进行存储单元(字)数目的扩展

将存储芯片的所有地址输入端,I/O数据端 及 读/写控制端 分别连在一起,而降这些芯片的片选信号端各自分开(接到地址高位上),由片选信号来区分各片地址。

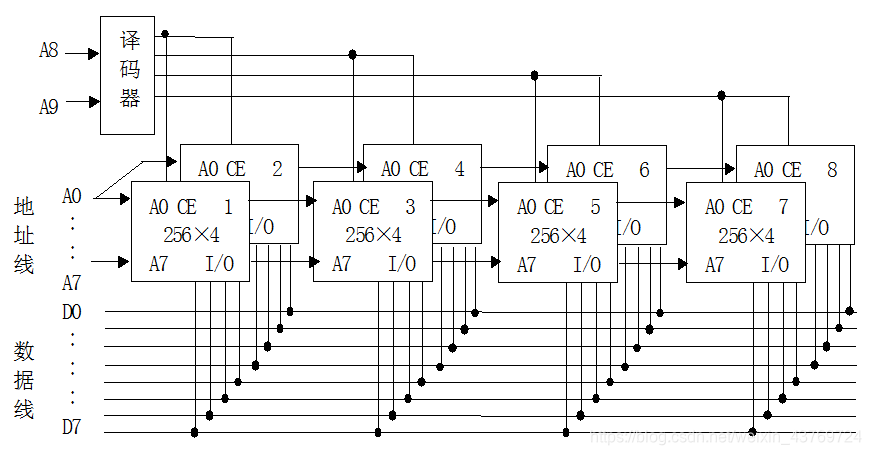

字位扩展

同时进行存储单元位数扩充 和 存储单元(字)数目的扩展。

1.2.4 RAM 存储器与CPU连接 ***重点

实质上是RAM 存储器芯片与系统总线的连接

CPU 与静态RAM存储器连接时,主要解决数据总线,地址总线和控制总线的连接问题。

存储芯片与CPU总线的连接,有两个很重要的问题:

- CPU的总线负载能力

CPU的总线驱动能力有限

单向传送的地址和控制总线,可采用三态锁存器和三态单向驱动器等来加以锁存和驱动

双向传送的数据总线,可以采用三态双向驱动器来加以驱动 - 存储芯片与CPU总线时序的配合

分析存储器的存取速度是否满足CPU总线时序的要求

如果不能满足:

考虑更换存储芯片

总线周期中插入等待状态TW

(1)数据总线的连接

- 三态缓冲器

静态RAM芯片 中的输入输出电路包含 三态缓冲驱动器时,芯片的数据线可直接挂接到 CPU 的数据总线上去,对于不含三态缓冲器的芯片构成的存储器,则须加三态缓冲驱动器,再与CPU 的数据总线相接。 - 传送方向控制门(增加灵活性)

可在CPU 数据总线与存储器数据线间加入数据传送方向控制门电路,以提高系统控制的可靠性和灵活性。在8086系统中,用8286/8287 芯片控制数据的传送方向。

(2)地址总线的连接

CPU 的地址总线通常分为两部分:

- 一部分直接与存储芯片用以片内寻址的地址线连接,通常是从 A 0 A_0 A0开始的低地址部分。(部分译码在存储芯片内部进行,即 片内译码)

- 另一部分则经译码器译码,产生的片选信号与存储器的片选端相连,一般是高地址部分的地址线。(或者不扩展时让芯片常有效)

!!!

地址重复时:地址高位对芯片的寻址无效时,即出现地址重复时,常选取其中既好用、又不冲突的一个“可用地址”,选取原则:高位全为0

(3)控制总线的连接

静态RAM存储子系统的控制信号主要有:

- 控制信号 R D ‾ \overline {RD} RD

- 写控制信号 W R ‾ \overline {WR} WR

- 以及存储器或 I/O 端口选择信号

M

/

I

O

‾

M/\overline {IO}

M/IO

- M / I O ‾ M/\overline {IO} M/IO=1,选操作对象为存储器

- M / I O ‾ M/\overline {IO} M/IO=0,选操作对象为I/O端口

可以将这些信号进行逻辑组合成不同的信号对芯片进行控制。

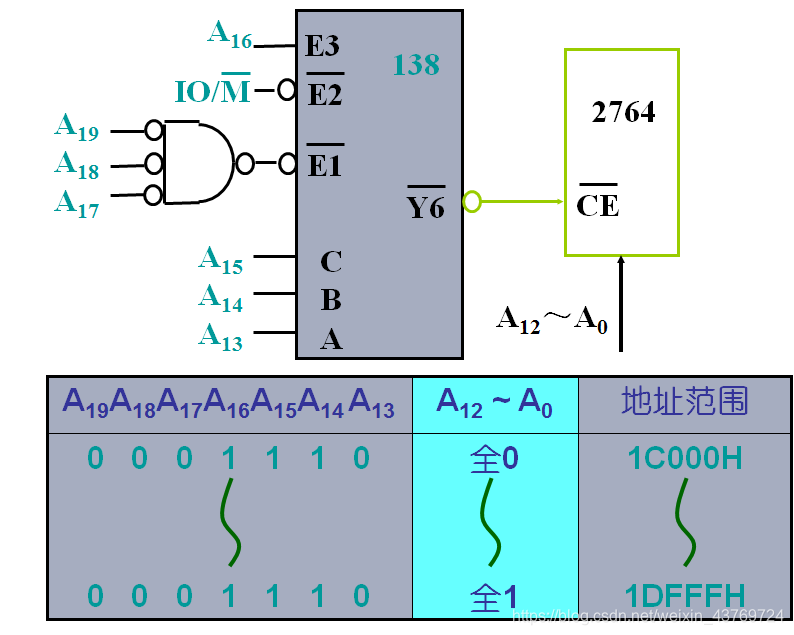

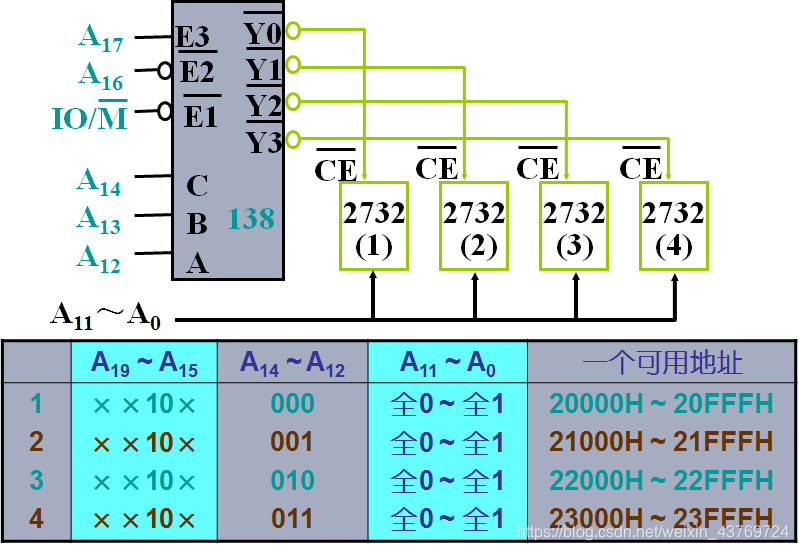

1.2.5 译码

- 门电路组合逻辑

- 采用集成译码芯片(常用):

- 常用的2:4译码器: 74LS139

- 常用的3:8译码器: 74LS138

- 常用的4:16译码器:74LS154

常用的译码方法:

-

全译码:所有的系统地址线均参与对存储单元的译码寻址,包括:

- 片内译码:低位地址线对芯片内各存储单元的译码寻址

- 片选译码:高位地址线对存储芯片的译码寻址

采用全译码,每个存储单元的地址都是唯一的,不存在地址重复

译码电路可能比较复杂、连线也较多

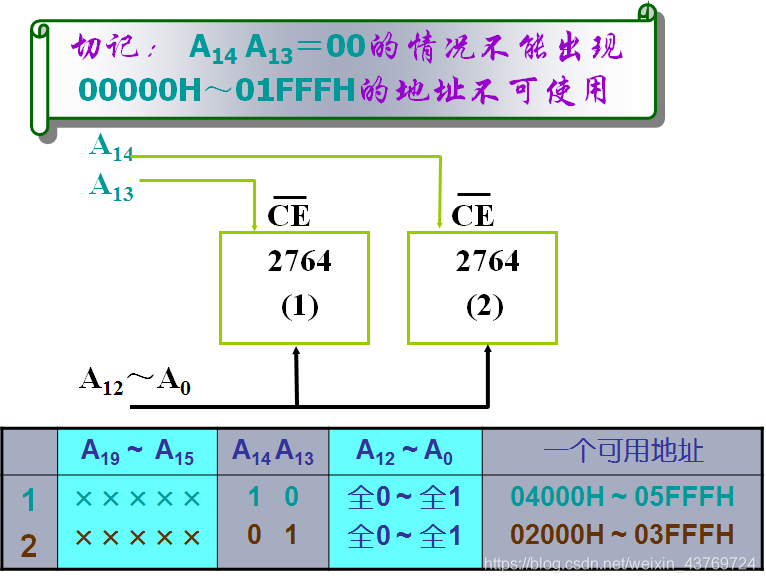

-

部分译码:只有部分高位地址线参与对存储芯片的译码

每个存储单元将对应多个地址(地址重复),需要选取一个可用地址

可简化译码电路的设计,但系统的部分地址空间将被浪费

-

线选译码:只用少数几根高位地址线进行芯片的译码,且每根负责选中一个芯片(组)

虽构成简单,但地址空间严重浪费

必然会出现地址重复(一个存储单元对应多个存储地址)

一个存储地址会对应多个存储单元

多个存储单元共用的存储地址不应使用

对一些存储芯片通过片选无效可关闭内部的输出驱动机制,起到降低功耗的作用

1.3 只读存储器 ROM(略)

典型 EEPROM 芯片有:AT24系列 AT24C04

EPROM 2716,EPROM 2764

EEPROM芯片2817A,EEPROM芯片2864A

1.4 高速缓冲存储器 Cache(略)

思路: 在引入高速缓冲存储器的系统中,内存由两级存储构成。一级是采用高速静态RAM芯片组成的小容量存储器,即Cache;另一级是用廉价的动态RAM芯片组成的大容量主存储器。

程序运行的所有信息存放在主存储器内,而高速缓冲存储器中存放的是当前使用最多的程序代码和数据,即主存中部分内容的副本。CPU访问存储器时,首先在Cache中寻找,若寻找成功,通常称为“命中”,则直接对Cache操作;若寻找失败,则对主存储器进行操作,并将有关内容置入Cache。

引入Cache是存储器速度与价格折衷的最佳方法。