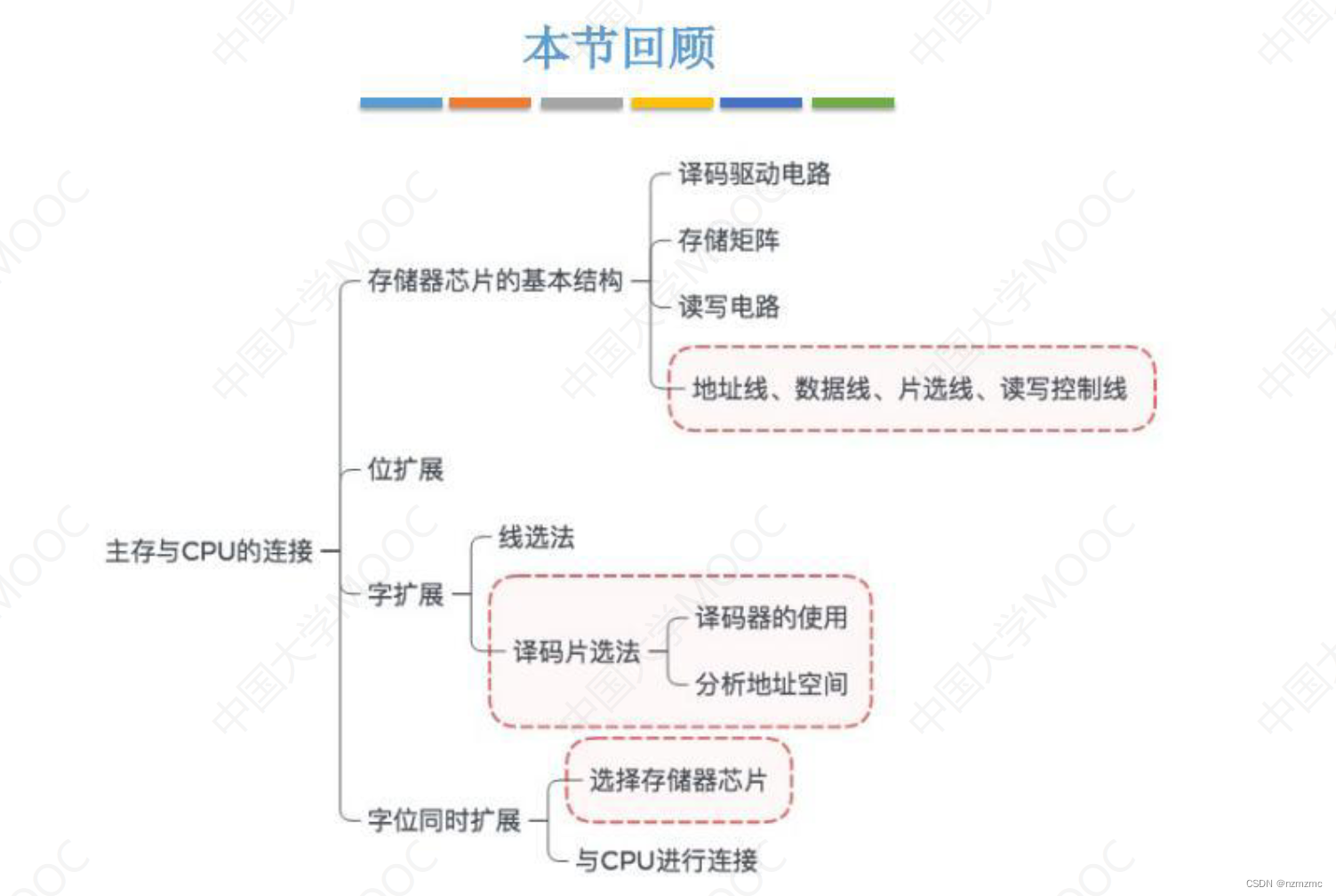

目录

3.存储系统

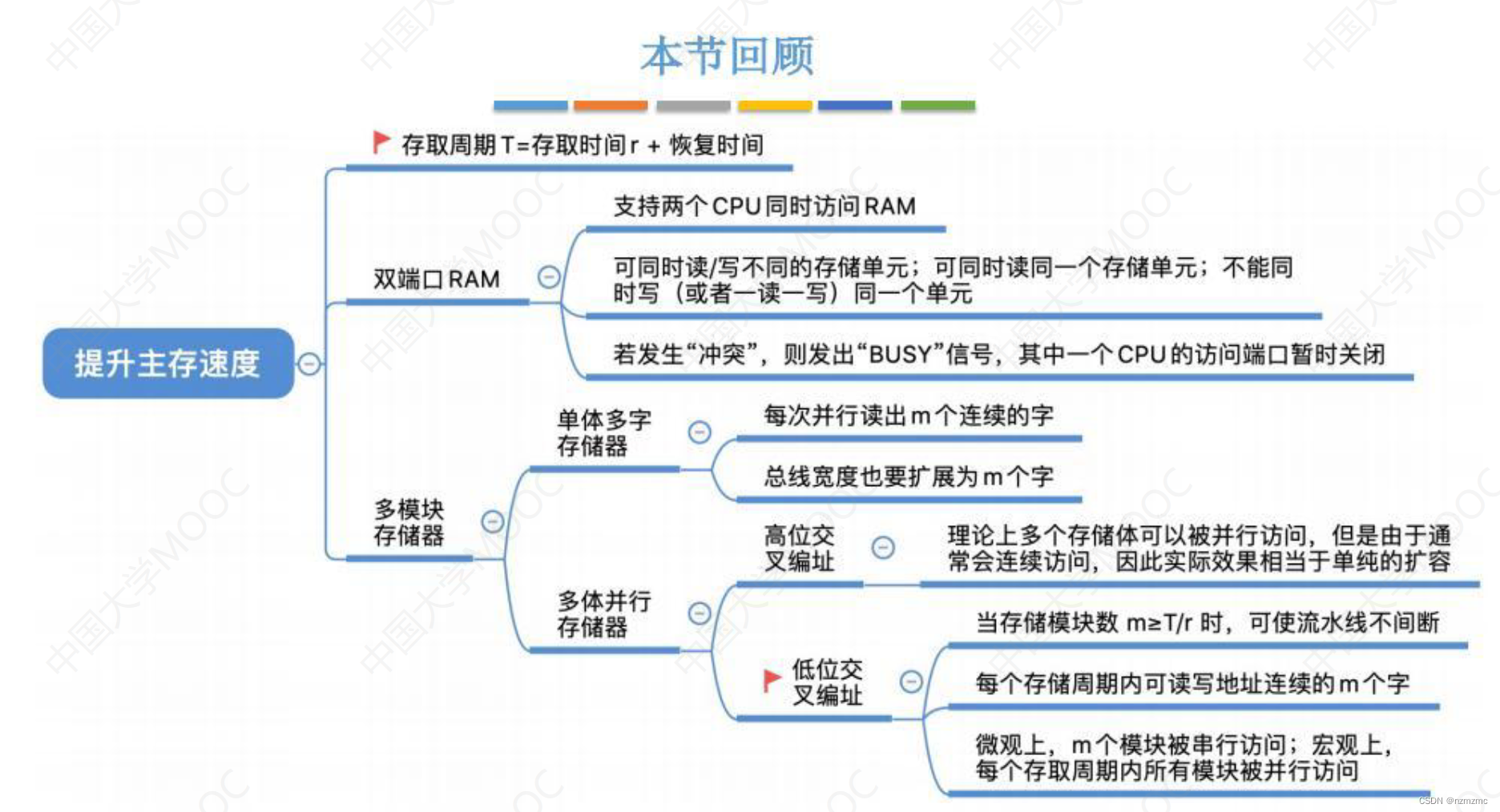

3.1存储器概述

3.2主存储器

3.3主存储器与CPU连接

部分习题

3.存储系统

3.1存储器概述

3.2主存储器

3.3主存储器与CPU连接

部分习题

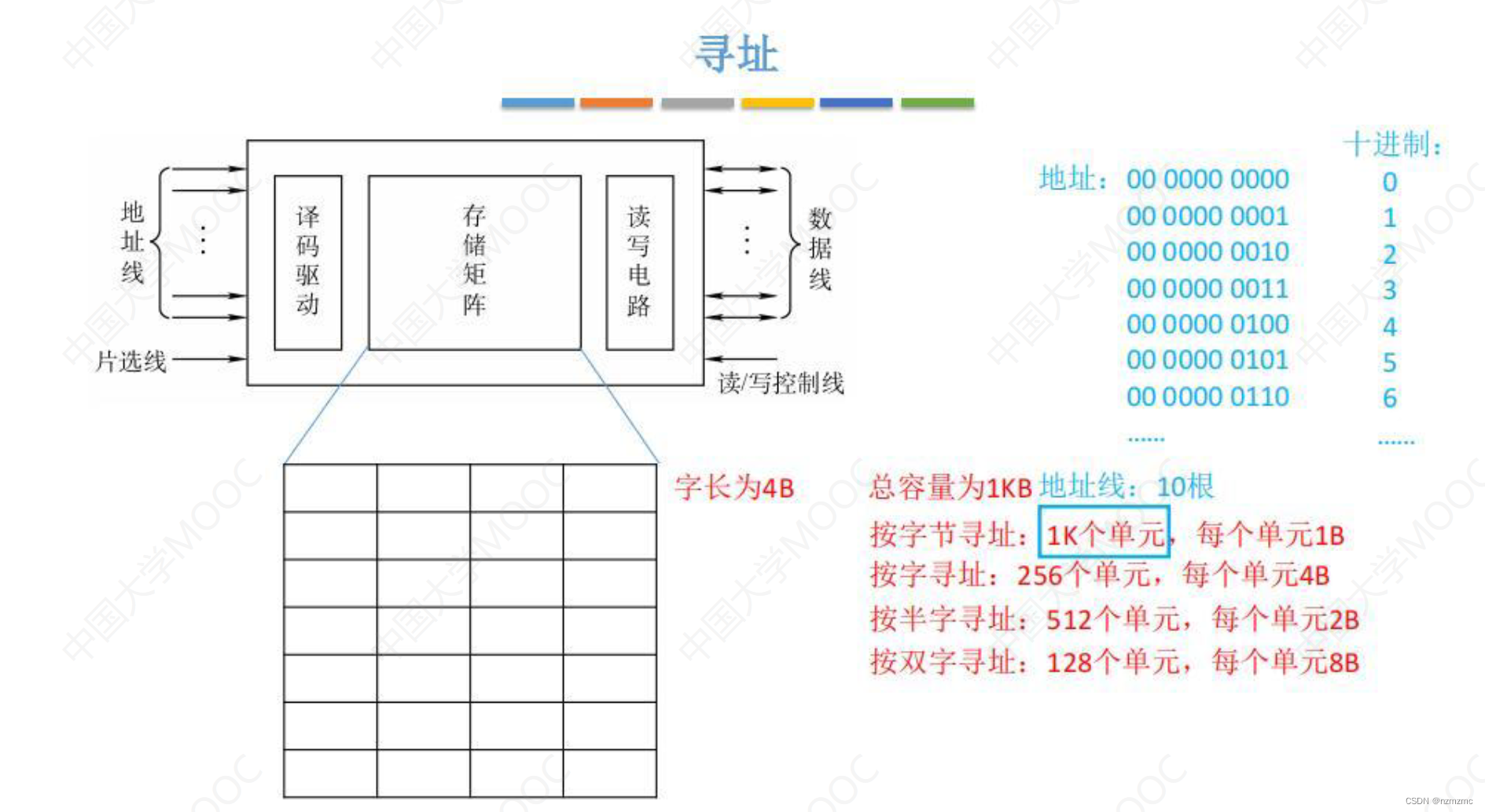

1.设机器字长32位,一个容量为16MB的存储器,CPU按半字寻址,其可寻址的单元数是()

A. B.

C.

D.

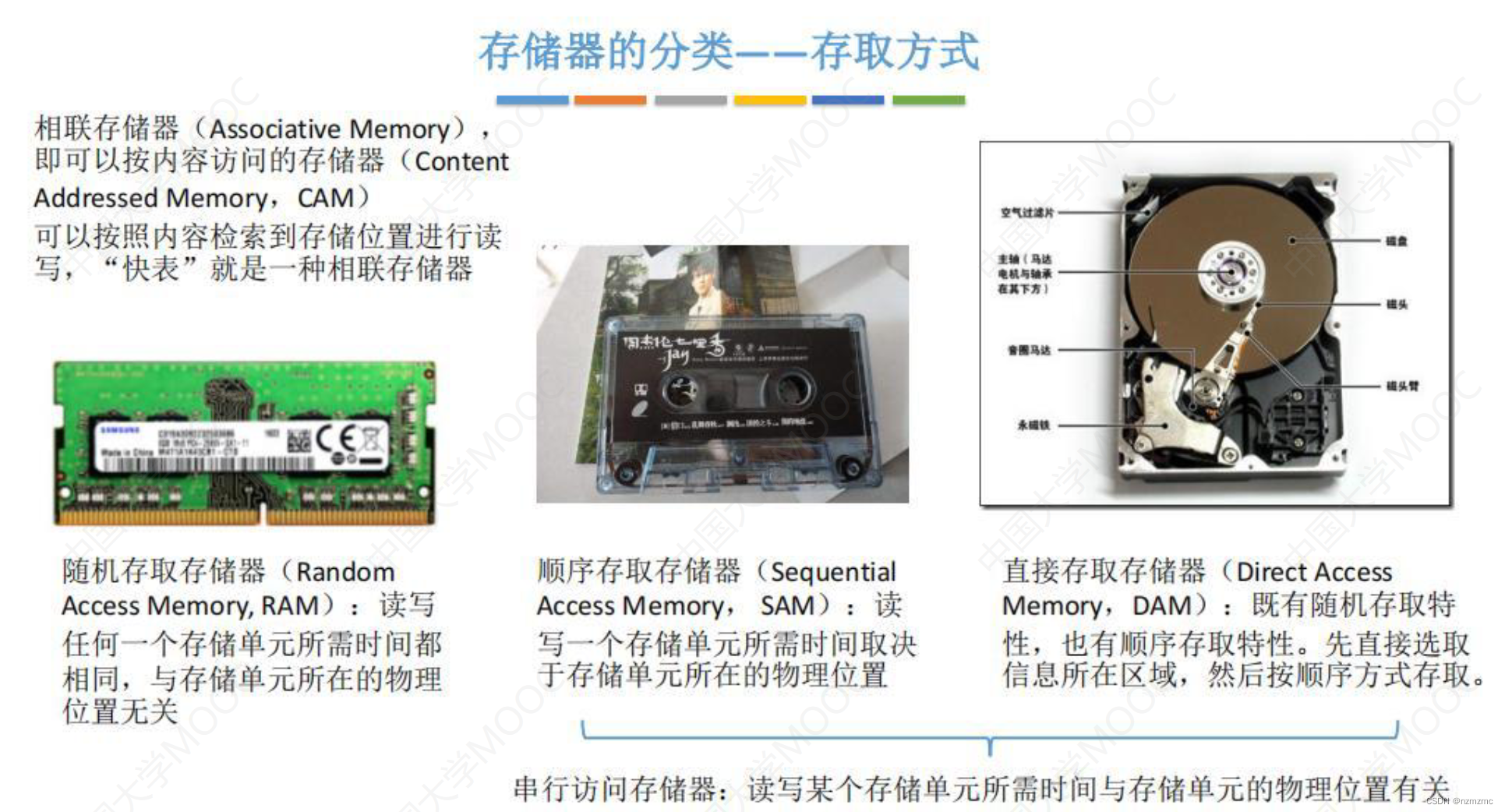

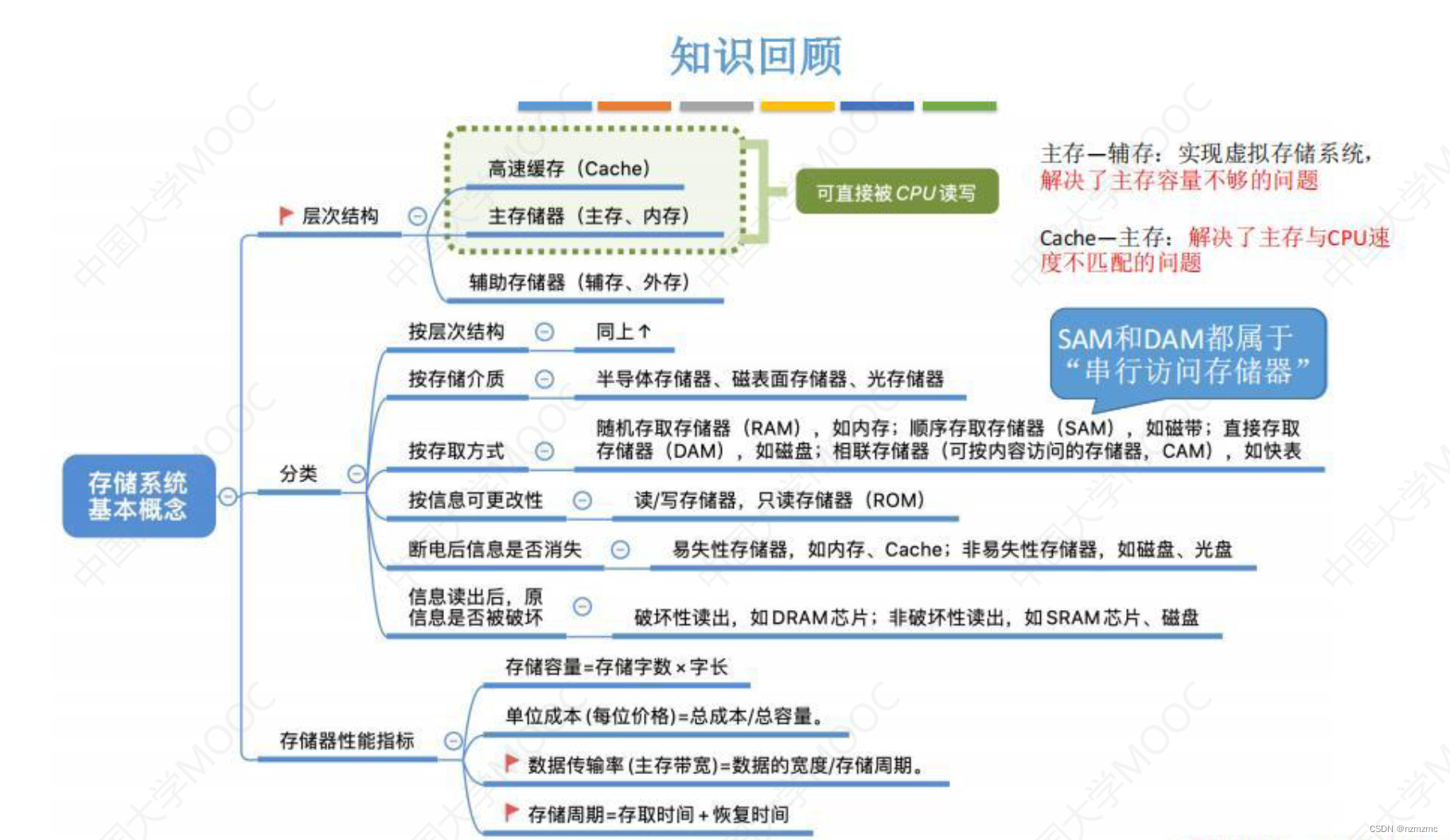

2.相联存储器是按()进行寻址的存储器

A.地址指定方式

B.堆栈存储方式

C.内容指定方式和堆栈存储方式相结合

D.内容指定方式和地址指定方式相结合

3.设机器字长64位,存储容量128MB,按字编址,可寻址单元个数是()

A.16MB B.16M C.32M D.32MB

4.在Cache和主存构成的两级存储体系中,主存与Cache同时访问,Cache的存取时间是100ns,主存存取时间是1000ns,设Cache和主存同时访问,若希望有效(平均)存取时间不超过Cache存取时间的115%,则Cache的命中率至少应为()

A.90% B.98% C.95% D.99%

5.下列各类存储器中,不采用随机存取方式的是()

A.EPROM B.CD-ROM C.DRAM D.SRAM

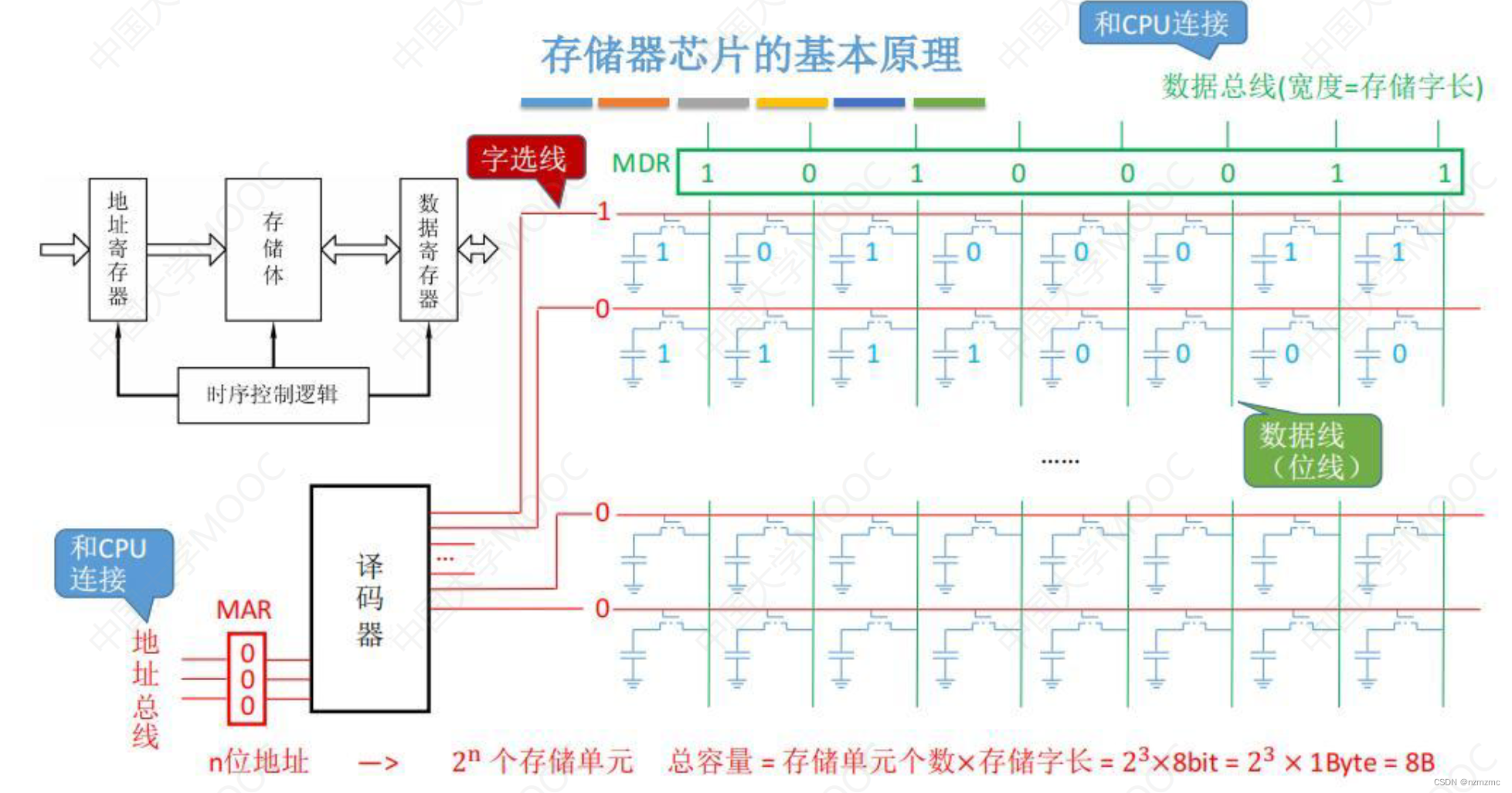

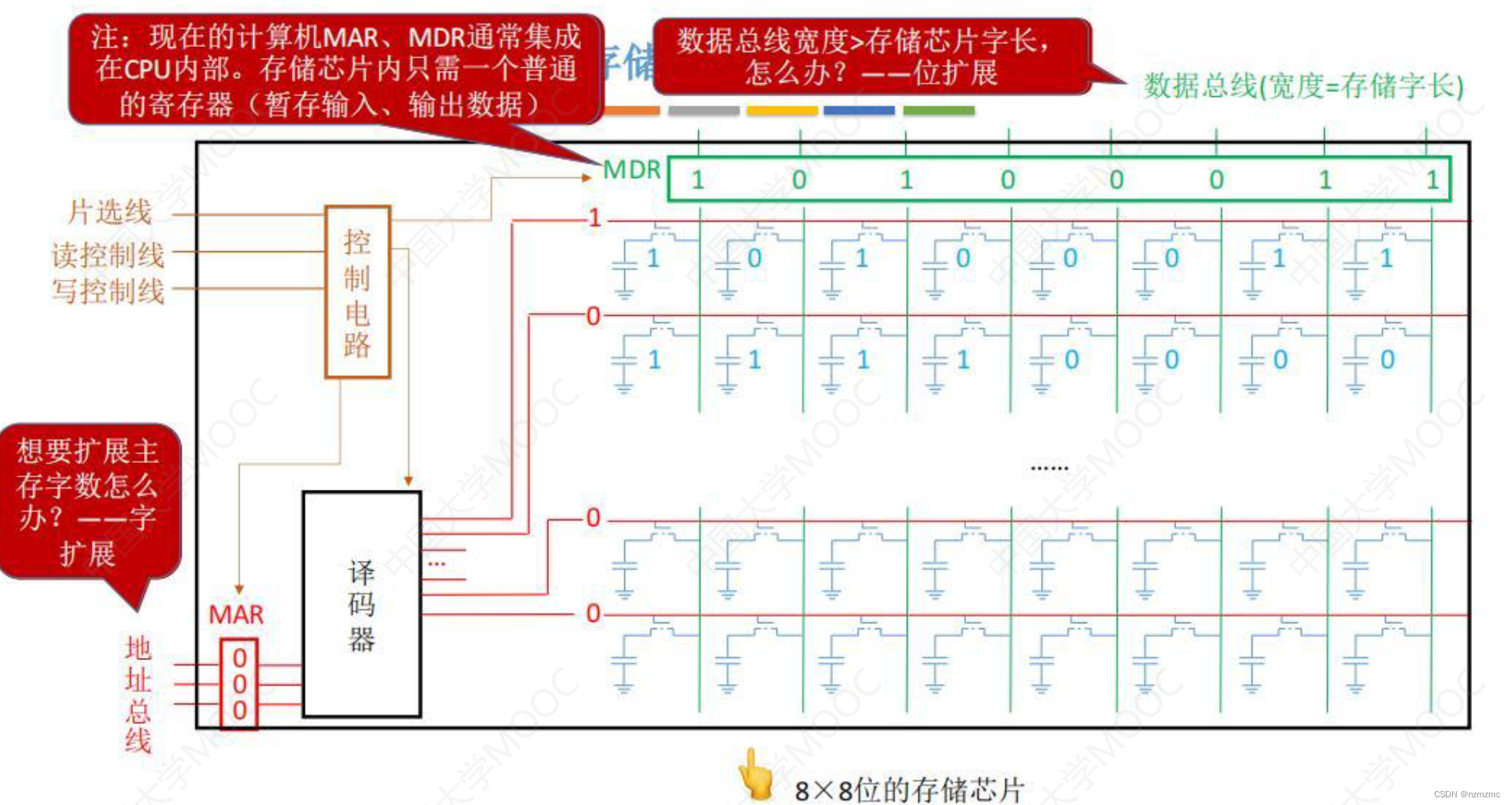

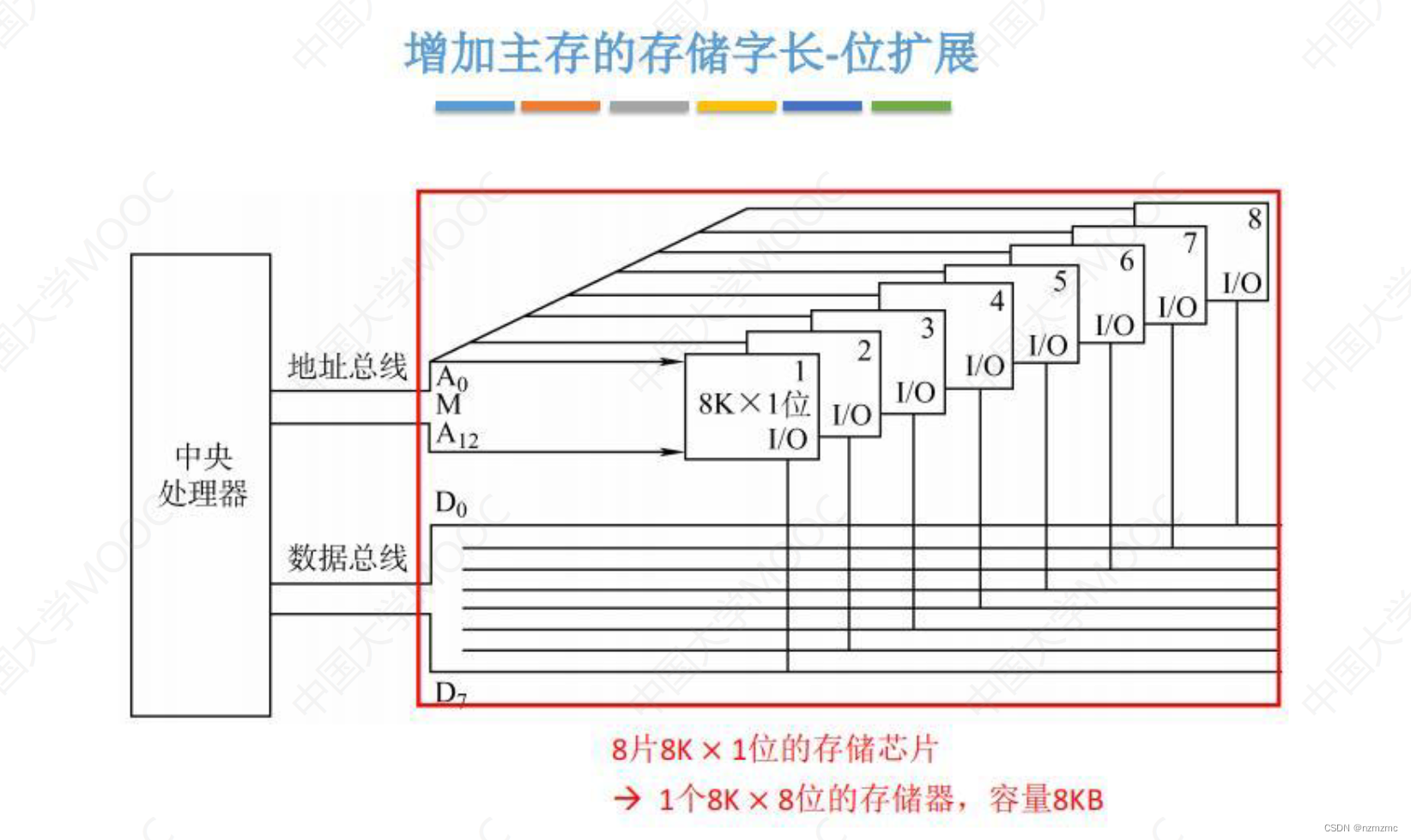

6.某一SRAM芯片,容量为1024*8位,除电源和接地端外,该芯片的引脚的最小数目为()

A.21 B.22 C.23 D.24

7.某存储器容量为32K*16位,则()

A.地址线为16根,数据线为32根 B.地址线为32根,数据线为16根

C.地址线为15根,数据线为16根 D.地址线为15根,数据线为32根

8.某一DRAM芯片,采用地址复用技术,其容量为1024*8位,除电源和接地端外,该芯片的引脚数最少是()(读写控制线为2根)

A.16 B.17 C.19 D.21

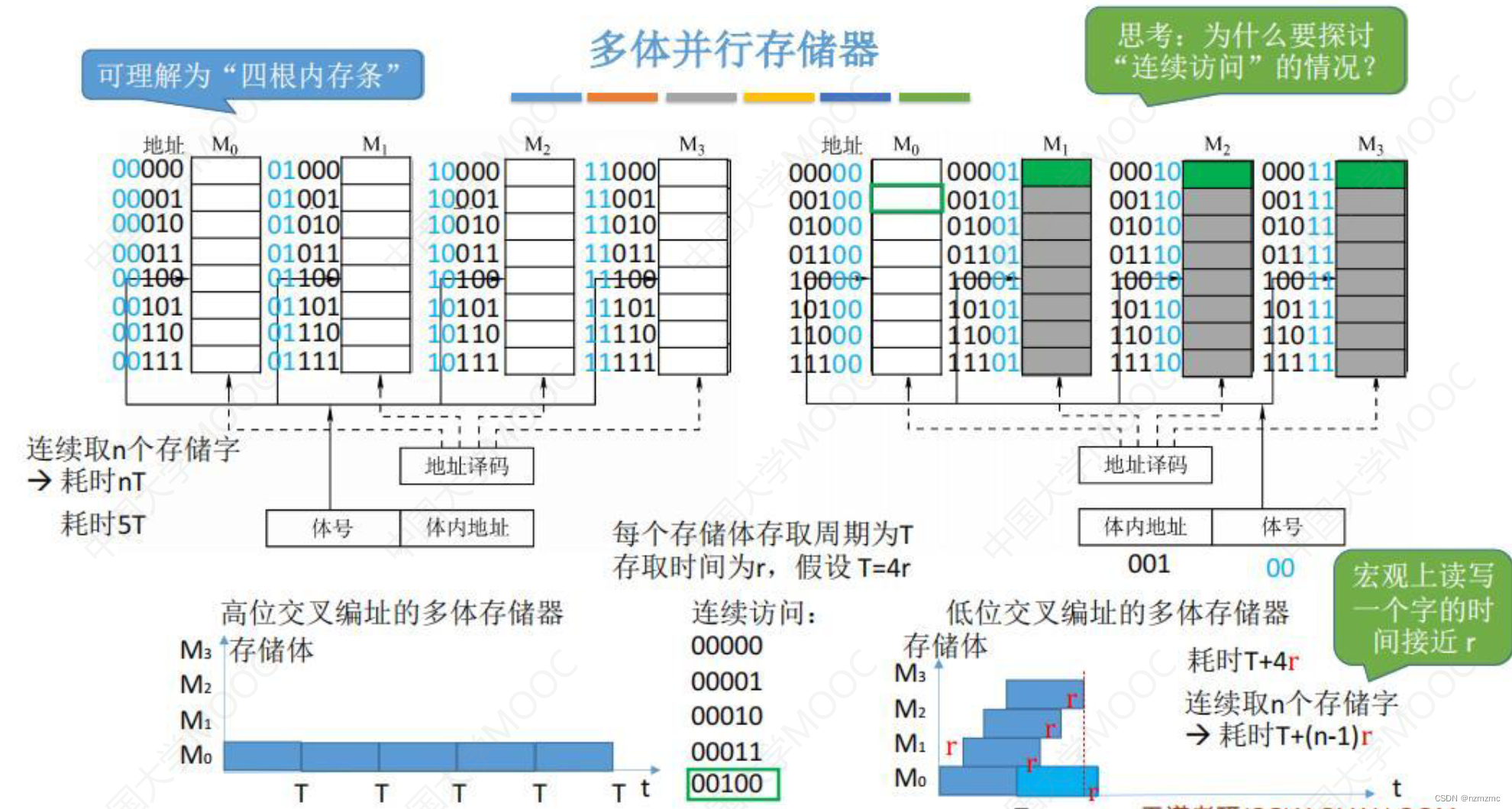

9.某机器采用四体低位交叉存储器,分别执行下列操作:1.读取6个连续地址单元中存放的存储字,重复80次;2.读取8个连续地址单元中存放的存储字,重复60次,则1.2.所花费的时间比是()

A.1:1 B.2:1 C.4:3 D.3:4

10.某计算机使用四体交叉编址存储器,假定在存储器总线上出现的主存地址(十进制)序列为8005,8006,8007,8008,8001,8002,8003,8004,8000,则可能发生访存冲突的地址是()

A.8004和8008 B.8002和8007 C.8001和8008 D.8000和8004

11.某计算机按字节编址,由4个64M*8位的DRAM芯片采用交叉编制方式构成,并与宽度为32位的存储器总线相连,主存每次最多读写32位数据,若double型变量x的主存地址为804001AH,则读取x需要的存储周期是()

A.1 B.2 C.3 D.4

12.若片选地址为111时,选定某一32K*16位的存储芯片工作,则该芯片在存储器中的首地址和末地址是()

A.00000H,01000H B.38000H,3FFFFH

C.3800H,3FFFH D.0000H,0100H

13.某计算机存储器按字节编址,主存地址空间大小为64MB,现用4M*8位的RAM芯片组成32MB主存储器,存储器地址寄存器MAR的位数至少是()

A.22 B.23 C.25 D.26

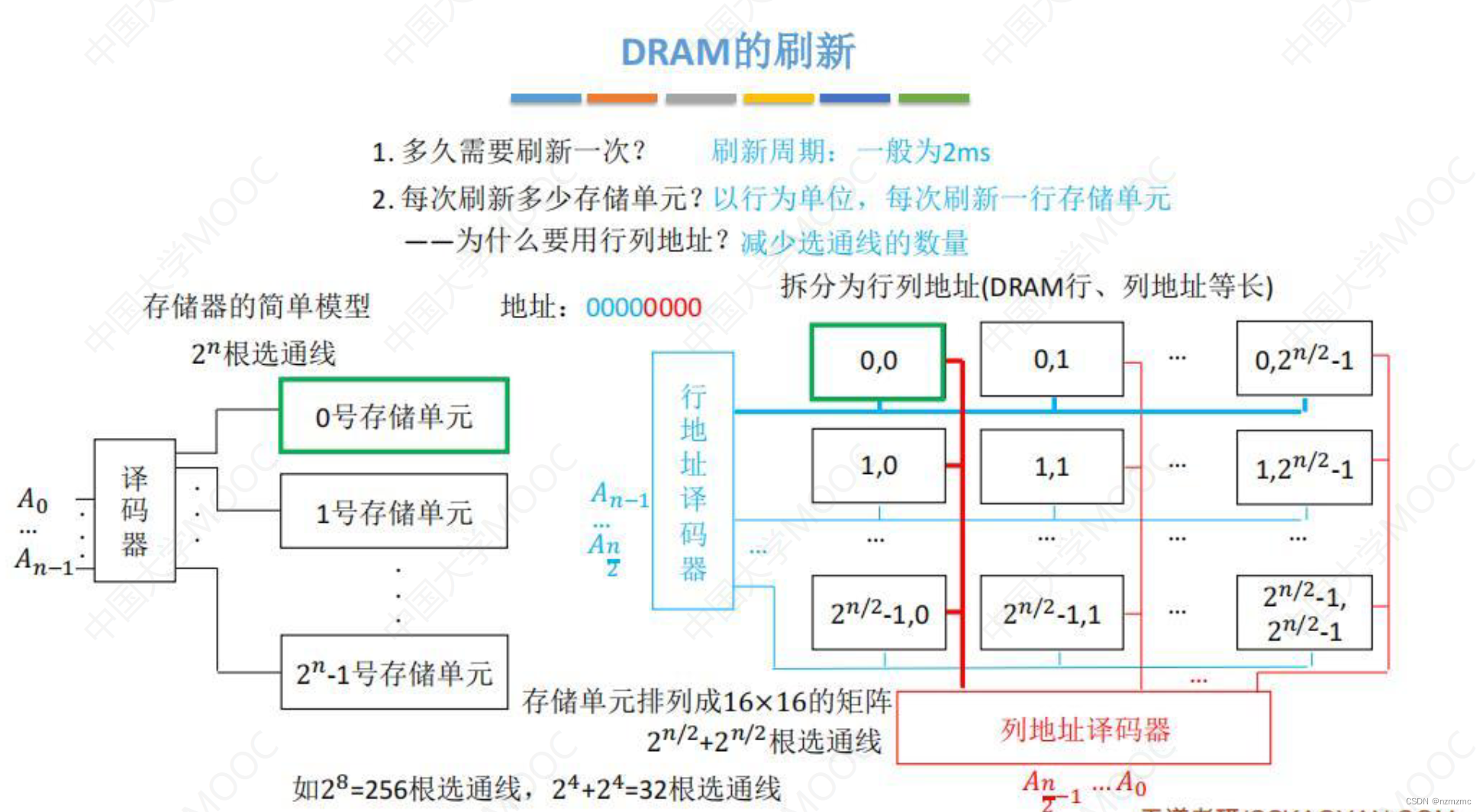

14.假定DRAM芯片中存储阵列的行数为r、列数为c,对于一个2K*1位的DRAM芯片,为保证其地址引脚数最少,并尽量减少刷新开销,则r、c的取值分别是()

A.2048,1 B.64,32 C.32,64 D.1,2048

1.B

16MB=B,字长32位,按半字(2B)寻址,单元数为

/2=

2.D

相联存储器的基本原理是吧存储单元所存内容的某一部分作为检索项(关键字项)去检索,并将存储器中与该检索项符合的存储单元内容进行读出或写入。所以它是按内容或地址进行寻址的,一般用来制作TLB、相联Cache

3.B

机器字长64位,即8B,按字编址,单元个数为128/8=16M

4.D

假设命中率为x,可得100x+1000(1-x)≤100*(1+15%),得x≥98.33%,因此命中率至少为99%

本题采用同时访问Cache和主存方式,若题设无说明,默认Cache不命中的时间为访问Cache和主存的时间之和

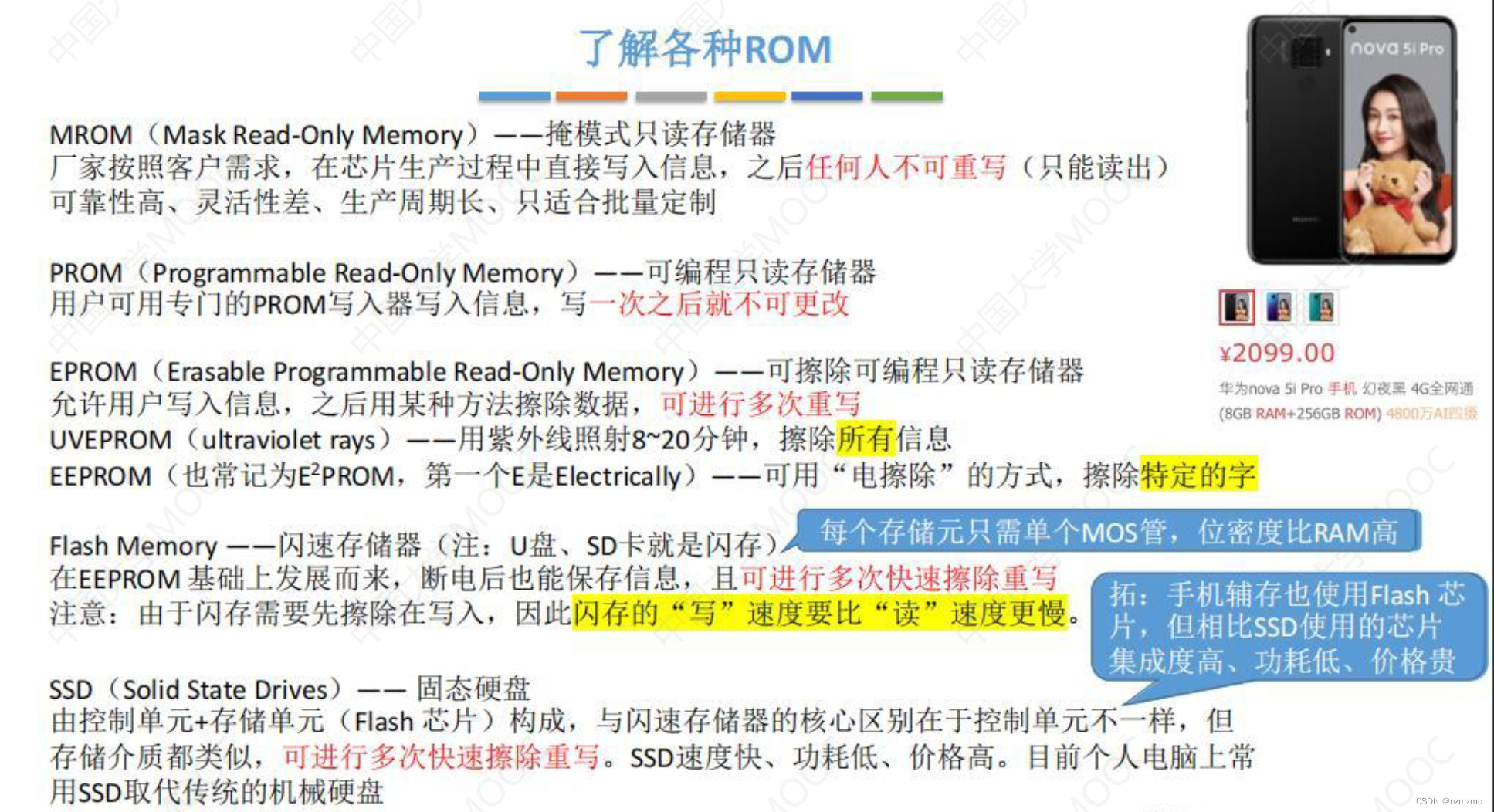

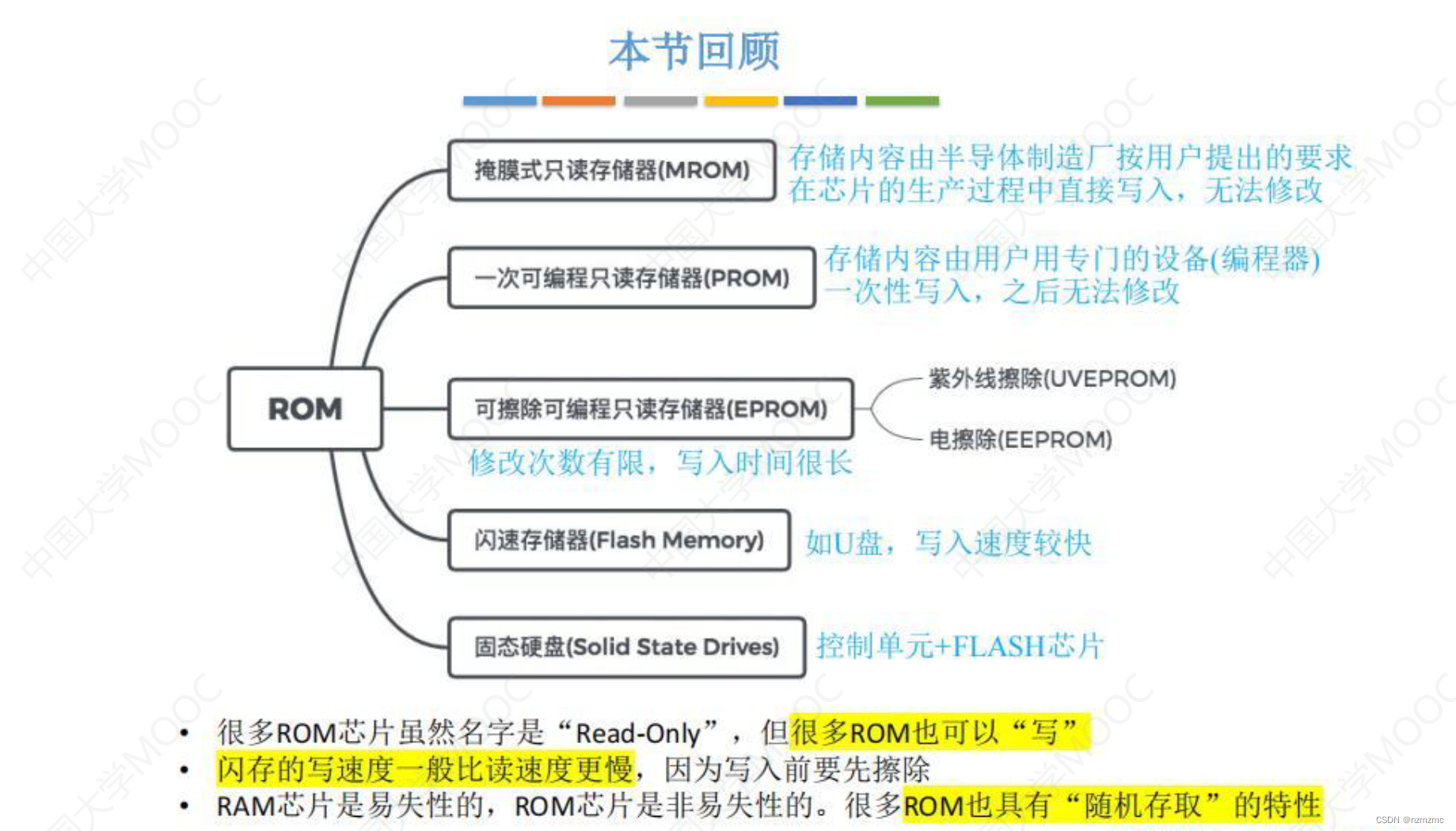

5.B

随机存取指CPU可对存储器的任意一个存储单元中的内容随机存取,存取时间与存取单元的物理位置无关。CD-ROM即光盘,采用串行存取方式(直接存取),CD-ROM是只读型光盘存储器,不属于只读存储器ROM

6.A

芯片容量为1024B,以字节为单位存取,地址线数要10根(1024B=B),8位说明数据线要8根,加上片选线和读写控制线,因此引脚数最小为10+8+1+2=21根(读写控制线也可共用一根,但题目选项中无20)

7.C

16位,数据线为16根,寻址空间32K=,地址线为15根

8.B

1024B=B,采用地址复用技术,地址线减半为5根,数据线仍为8根,加上行通选和列通选及读写控制线共4根,总5+8+4+17根

9.C

1.每轮读取存储器的前6个T/4时间(共3T/2)内,依次进入各体,下一轮欲读取存储器时,最近访问的M1还在占用(才过T/2时间),因此必须等待T/2时间才能读取,最后一轮读取结束的时间是本轮第6个字读取结束,共(6-1)*T/4+T=2.25T,总时间为(80-1)*2T+2.25T=160.25T

2.每轮读取8个存储字正好2T,每轮结束后,M1刚好经过了时间T,最后一轮读取结束时间是本轮第8个字读取结束,共(8-1)*T/4+T=2.75T,总时间为(60-1)*2T+2.75T=120.75T

因此花费时间比为4:3

10.D

模块序号=访存地址%存储器交叉模块数

| 访存地址 | 8005 | 8006 | 8007 | 8008 | 8001 | 8002 | 8003 | 8004 | 8000 |

| 模块序号 | 1 | 2 | 3 | 0 | 1 | 2 | 3 | 0 | 0 |

8004和8000对应模块号都为0,出现在同一模块内且在相邻的访问请求中,满足发生冲突条件

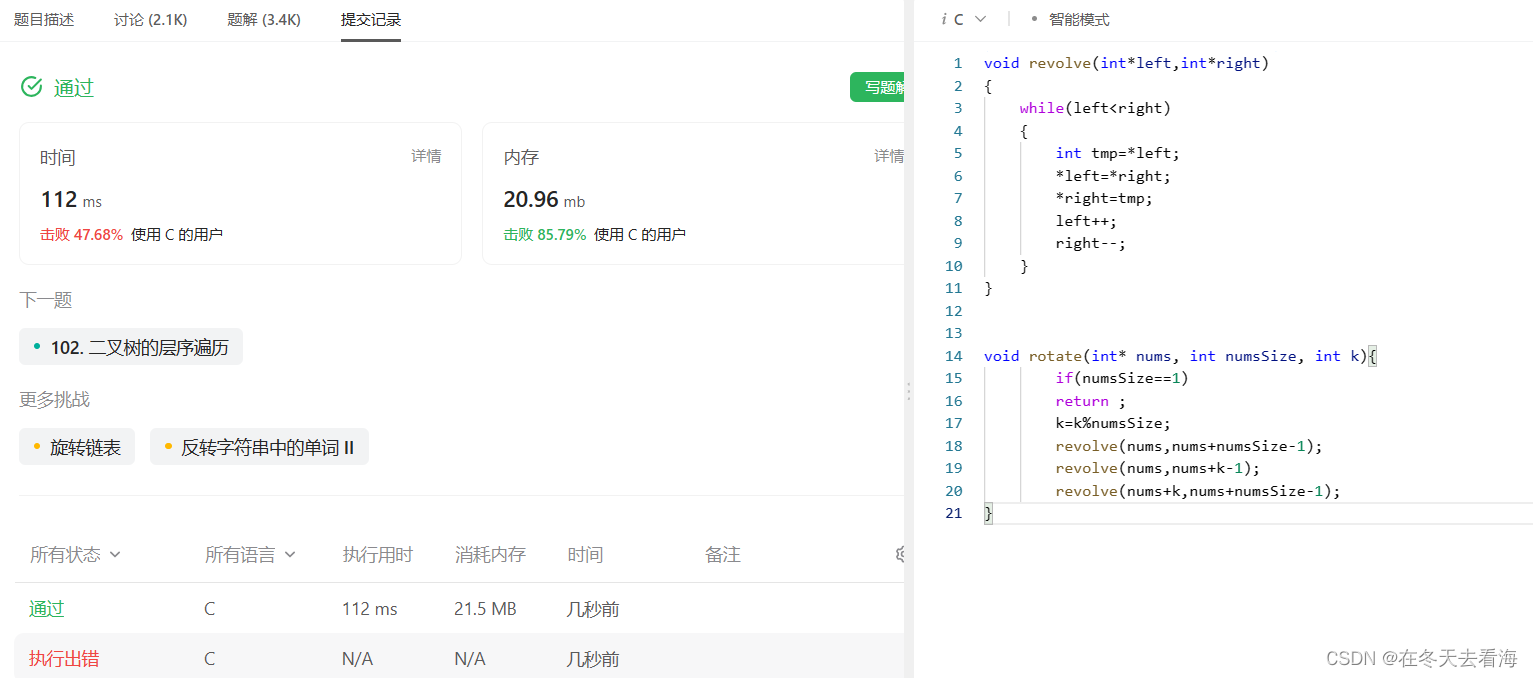

11.C

double型变量站64位(8B),交叉编址默认低位,最低两位表示体号,最低两位为10,从2开始存储,如下表,需要3轮

| 体号0 | 体号1 | 体号2 | 体号3 | |

| 第x行 | 8040018 | 8040019 | 804001A | 804001B |

| 第x+1行 | 804001C | 804001D | 804001E | 804001F |

| 第x+2行 | 8040020 | 8040021 | 8040022 | 8040023 |

12.B

32K*16地址线15根,片选地址3位,地址总位数18位,高3位为111,则首地址为0011 1000 0000 0000 0000=38000H,末地址为0011 1111 1111 1111 1111=3FFFFH

13.D

主存按字节编址,地址空间大小64MB,MAR寻址范围,因此是26位,实际主存容量32MB不能代表MAR位数

14.C

DRAM采用地址线复用技术,尽量选用行列差值不太大的,B,C选项地址线只需6根,其次为了减少刷新开销,DRAM一般按行刷新,应选行数较少的

![P1941 [NOIP2014 提高组] 飞扬的小鸟](https://img-blog.csdnimg.cn/img_convert/bc2b3fbee1f45c649a833d0e9a15d9fe.png)

![[HDLBits] Mt2015 q4b](https://hdlbits.01xz.net/mw/thumb.php?f=Mt2015_q4b.png&width=800)