🔥点击查看精选 CXL 系列文章🔥

🔥点击进入【芯片设计验证】社区,查看更多精彩内容🔥

📢 声明:

- 🥭 作者主页:【MangoPapa的CSDN主页】。

- ⚠️ 本文首发于CSDN,转载或引用请注明出处【https://mangopapa.blog.csdn.net/article/details/132179657】。

- ⚠️ 本文目的为 个人学习记录 及 知识分享。因个人能力受限,存在协议解读不正确的可能。若您参考本文进行产品设计或进行其他事项并造成了不良后果,本人不承担相关法律责任。

- ⚠️ 若本文所采用图片或相关引用侵犯了您的合法权益,请联系我进行删除。

- 😄 欢迎大家指出文章错误,欢迎同行与我交流 ~

- 📧 邮箱:mangopapa@yeah.net

- 💬 直达博主:loveic_lovelife 。(搜索或点击扫码)

文章目录

- 1. MESI 简介

- 2. MESI 状态介绍

- 3. MESI 状态转移

1. MESI 简介

目前 CPU 系统中多是基于 MESI 协议进行缓存一致性管理,CXL.cache 协议同样采用 MESI 协议来维护 Host 与 Device 的缓存一致性(Cache Coherence)。CXL 系统中,缓存一致性主要由 Host 来管理,从而减小 Device 端的设计复杂度。

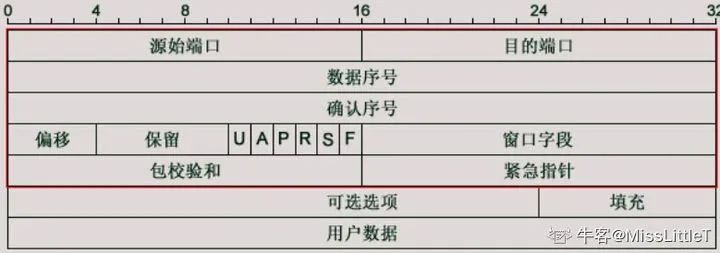

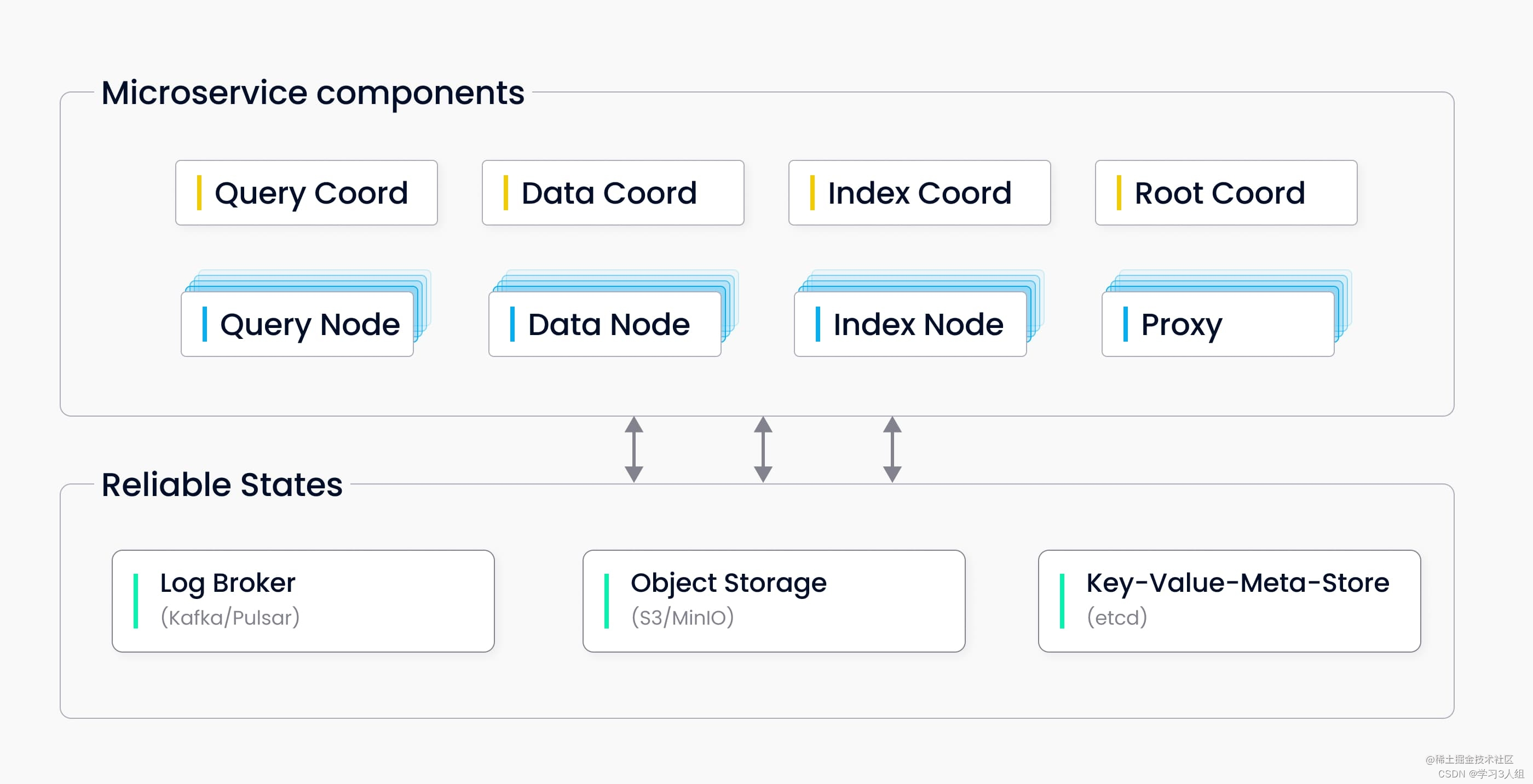

下表为 MESI 协议的简单展示。

2. MESI 状态介绍

为了支持 MESI 协议,Cache 内每一条 Cacheline 内都有一个 2b Tag 来指示其 MESI 状态,该 Tag 位于 Cacheline 的地址或数据之后。MESI 各个子状态释义如下:

- M (Modified),表示当前 Cacheline 的数据已被当前 CPU 修改。此时该 Cacheline 内数据为最新,但还没有同步到主存。处于 M 状态的 Cacheline 为当前 CPU 独享且数据为最新,当前 CPU 可以直接读,也可以直接写。其他 CPU Cache 中没有缓存该 Cacheline,若其他 CPU 要读写该 Cacheline,当前 CPU 需要将数据写回主存。

- E (Exclusive),表示当前 Cacheline 的数据为当前 CPU 独享,数据尚未被修改。处于 E 状态时,该 CPU 可以直接操作 Cacheline,不用通知其他 CPU。

- S (Shared),表示当前 Cacheline 的数据为共享状态且数据为最新,可能出现在多个 CPU 的 Cache 中。处于 S 状态的 Cacheline 数据为最新,若某 CPU 想要读该 Cacheline 数据,可以直接读;若要写该 Cacheline,需要先 Invalid 其他 CPU Cache 中的该 cacheline 数据。

- I (Invalid),表示当前 Cacheline 无效,在当前 CPU Cache 中不存在。

以下几篇博文讲 MESI 讲得蛮好:

- 带你了解缓存一致性协议MESI - 知乎 (zhihu.com)

- 并发吹剑录(一):CPU 缓存一致性协议 MESI - 知乎 (zhihu.com)

3. MESI 状态转移

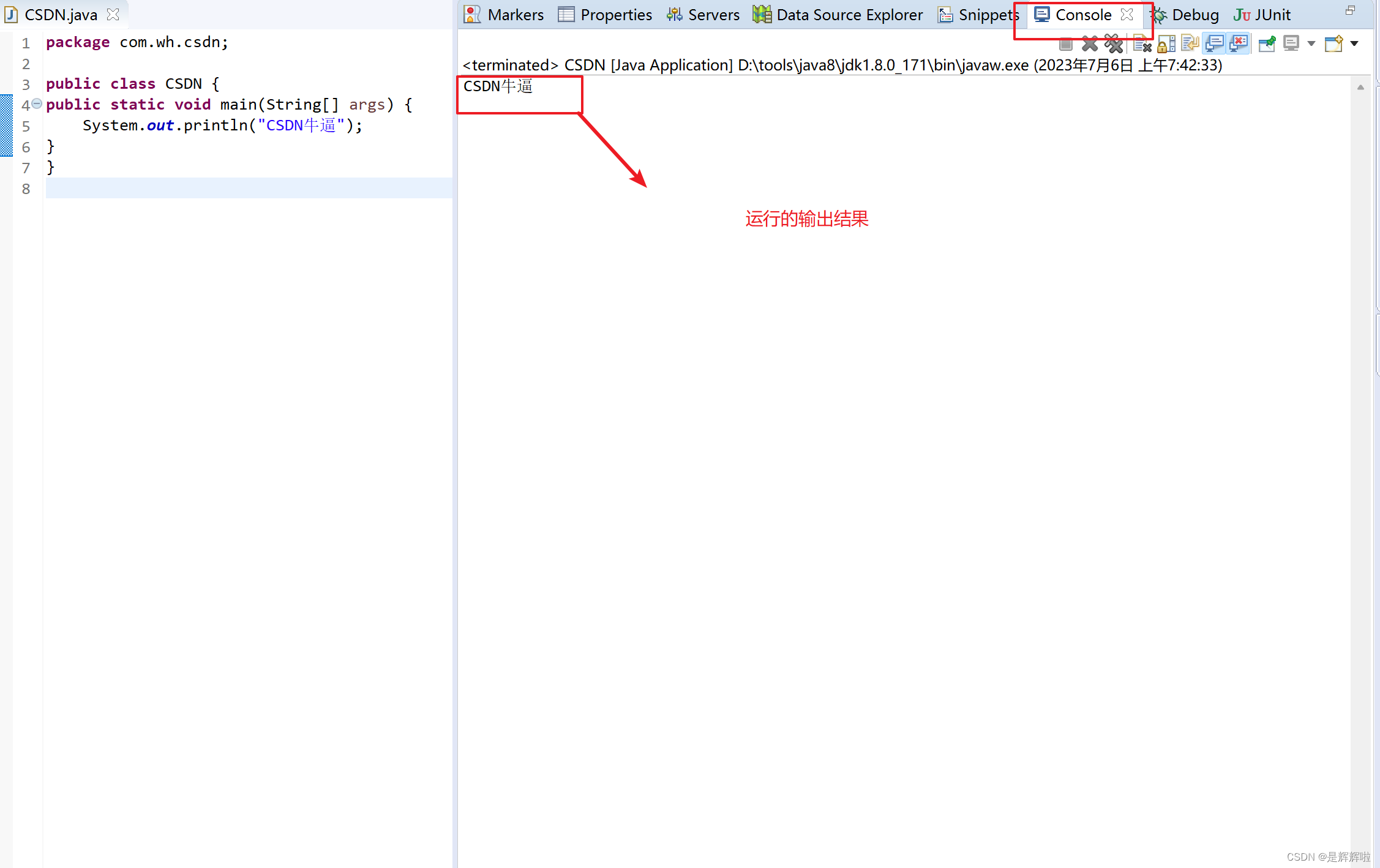

以 CPU 系统为例,当本地 CPU 或远端 CPU 对某地址的 Cacheline 进行读写操作时,该 Cacheline 状态会发生转移。MESI 状态转移图如下:

上图中,

- Local Read、Local Write,本地读写,是指本地 CPU 对本地 Cache 内相关地址 Cacheline 的读写;

- Remote Read、Remote Write,远端读写,是指远端 CPU 发起读写操作,读写的地址在本地 Cache 内存在副本;

- Silent Write 是指 Modified 状态下,当前 CPU 把其独享的 Cacheline 内的脏数据(修改后的数据)写入主存后退回到 Exclusive 状态。

从读写操作角度来看:

- 本地读,本地 MES 保持不变,I->S/E;

- 本地写,本地 M 不变,ESI->M;

- 远端读,本地 ME 变为 S,SI 不变;

- 远端写,本地 MES 会变为 I,I 不变。

几个典型状态转移的解释:

- E->S,其他 CPU 要读该数据,读完后其他 CPU Cache 也有一份该 Cacheline 副本;

- E->M,当前 CPU 写数据,修改了原来的数据;

- S->M,当前 CPU 修改处于 S 状态的 Cacheline 数据,修改之前先将其他 CPU Cache 中该 cacheline 置为 I;当前 CPU 收到 Invalid Ack 后当前 Cacheline 才能转为 M;

- S->I,收到了其他 CPU 发来的 Invalid 请求,其他 CPU 要写该 Cacheline;

- M->S,其他 CPU 要读该数据。先同步到主存再转为 S;

- M->I,其他 CPU 要写该 Cacheline,先同步到主存再转为 I;

补充总结:

- Local Read/Write 对本地 M 状态的 Cacheline 状态没有影响;

- Remote Read/Write 对本地 I 状态的 Cacheline 状态没有影响;

- 对处于 I 状态的 Cacheline 发起写操作之前要先 Invalidate 其他 Cache 中的该地址数据,比如:Remote CPU 发起写操作时,无论本地相同地址的 Cacheline 处于哪种状态,都会回退到 I 状态。

- I 状态时本地 CPU 发起 Read 操作,若外部 cache 内存在 S 状态的副本,则本地该 Cacheline 由 I 转为 S,若外部 Cache 不存在副本,则本地该 Cacheline 由 I 转为 E。

以下几篇博文讲 MESI 状态转移讲得不错:

- 并发基础理论:缓存可见性、MESI 协议、内存屏障、JMM - 知乎 (zhihu.com)

- MESI(缓存一致性协议) - 猿起缘灭 - 博客园 (cnblogs.com)

- 缓存一致性协议MESI 详解 - 掘金 (juejin.cn)

- 并发研究之CPU 缓存一致性协议(MESI) - 枫飘雪落 - 博客园 (cnblogs.com)

- 【cache 篇】MESI 协议 - 知乎 (zhihu.com)

|

|

🔥 精选往期 CXL 协议系列文章,请查看【 CXL 专栏】🔥

⬆️ 返回顶部 ⬆️