Task 1 Create a Milkyway library

先进入lab1_data_setup目录,打开icc_shell,创建项目

create_mw_lib -technology $tech_file -mw_reference_library "$mw_path/sc $mw_path/io $mw_path/ram16x128" -bus_naming_style {[%d]} -open $my_mw_lib

然后ls risc_chip.mw查看是否创建成功

Task 2 Load the Nestlist,TLU+,Constraints and Controls

import_designs $verilog_file -format verilog -top $top_design

set_tlu_plus_files -max_tluplus $tlup_max -min_tluplus $tlup_min -tech2itf_map $tlup_map

check_library

check_tlu_plus_files

list_libs

source $derive_pg_file

check_mv_design -power_nets

read_sdc $sdc_file

check_timing

report_timing_requirements

report_disable_timing

report_case_analysis

report_clock

report_clock -skew

source $ctrl_file

source sc[TAB]z[TAB]

exec cat zic.timing

remove_ideal_network [get_ports scan_en]

save_mw_cel -as RISC_CHIP_data_setup

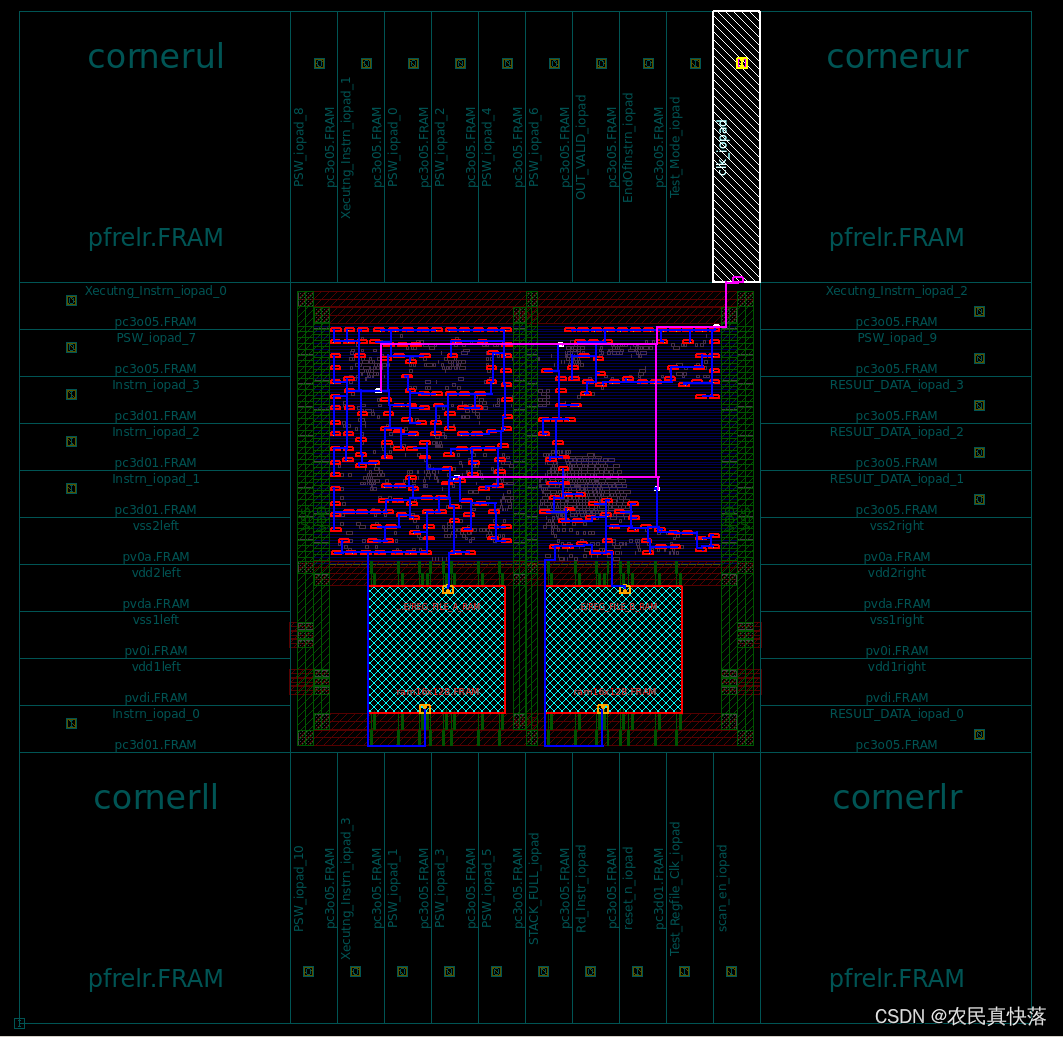

Task3 design planning

read_def $def_file

set_pnet_options -complete {METAL3 METAL4}

save_mw_cel -as RISC_CHIP_floorplanned

Task4 placement

place_opt

redirect -tee place_opt.timing {report_timing}

report_congestion -grc_based -by_layer -routing_stage global

save_mw_cel -as RISC_CHIP_placed

Task5 CTS

remove_clock_uncertainty [all_clocks]

set_fix_hold [all_clocks]

clock_opt

redirect -tee clock_opt.timing {report_timing}

save_mw_cel -as RISC_CHIP_cts

Task6 Basic Flow:Routing

File->Open design ,risc_chip.mw

Select RISC_CHIP_cts

相当于open_mw_cel RISC_CHIP_cts

source $ctrl_file

route_opt

view report_timing -nosplit

v rt

v rt -delay min

report_design -physical

save_mw_cel -as RISC_CHIP_routed

exit