👉个人主页:highman110

👉作者简介:一名硬件工程师,持续学习,不断记录,保持思考,输出干货内容

参考资料:《镁光DDR4数据手册》

目录

DDR4颗粒的内部结构

颗粒寻址和容量说明

其他颗粒的内部结构

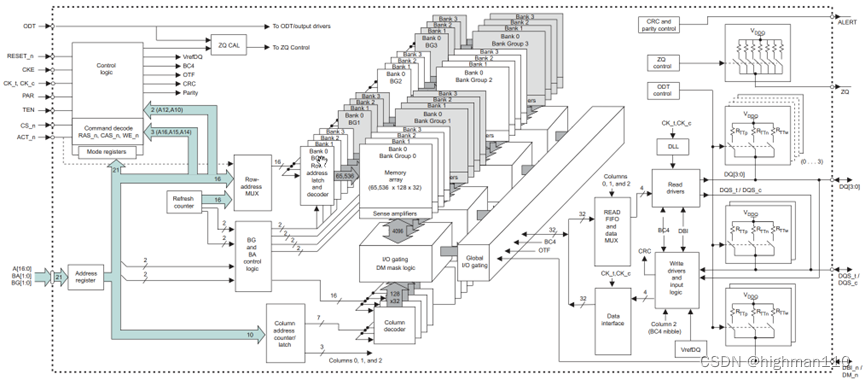

前面我们分享了基本存储阵列的读写原理,通过字线、位线选择,加上感应放大器的作用,可以访问到存储阵列中的任一bit。我们实际的应用中,DRAM颗粒的容量是很大的,所以不可能只用一个存储阵列,也不可能把大量的字线、位线都引出来去控制,除了存储阵列外,必然还需要一些行、列选择逻辑部件,今天就来研究一下颗粒内部结构,看一下存储阵列是怎么排布的,存储阵列字线、位线和颗粒封装上的地址线、数据线是怎么对应上的。

DDR4颗粒的内部结构

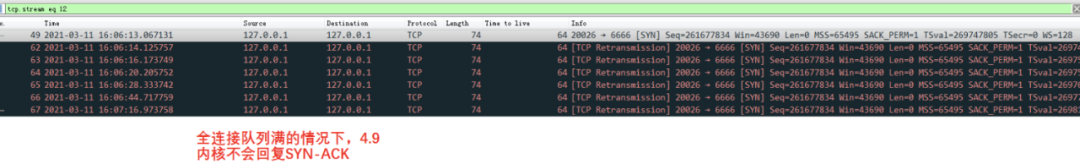

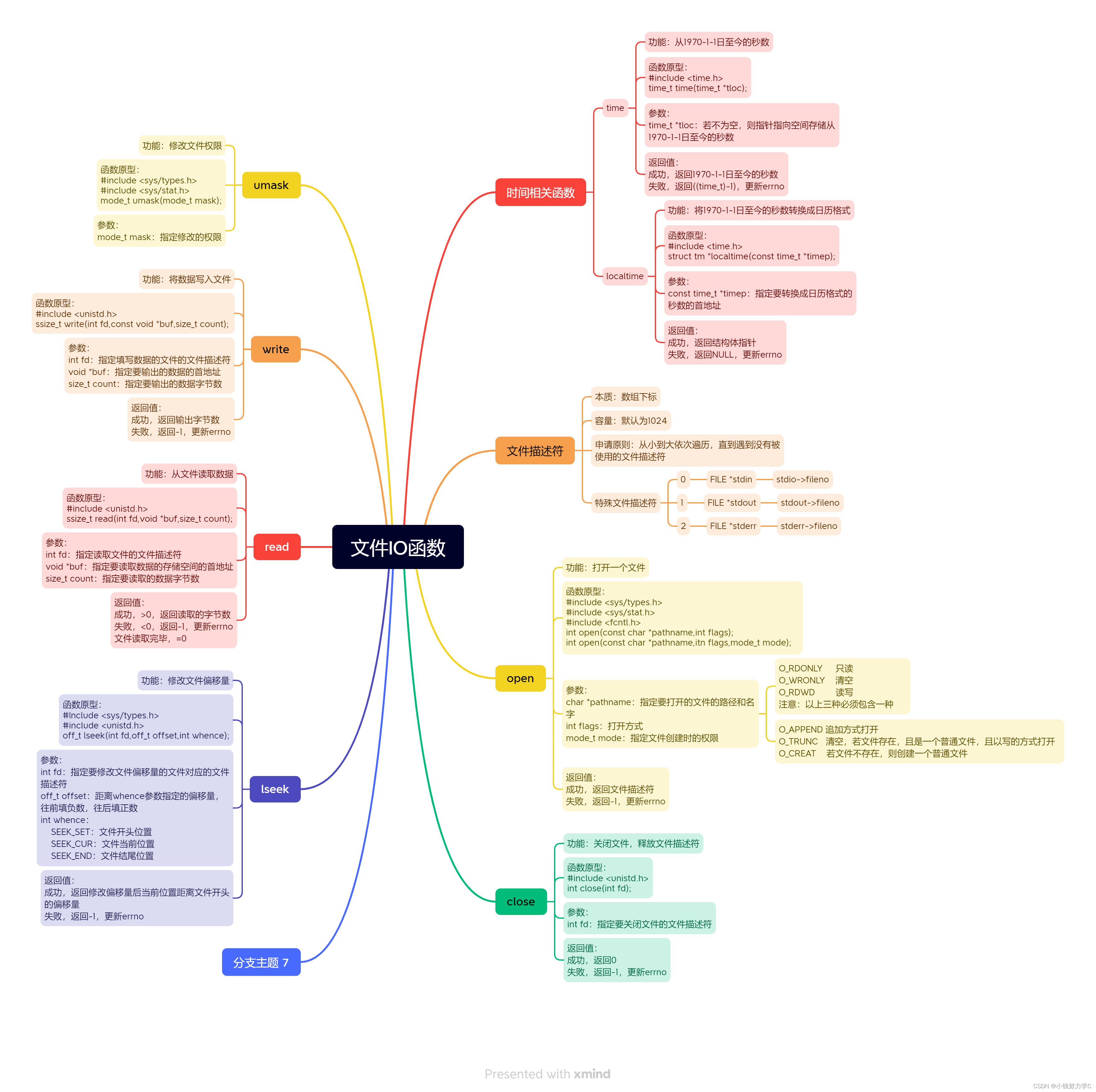

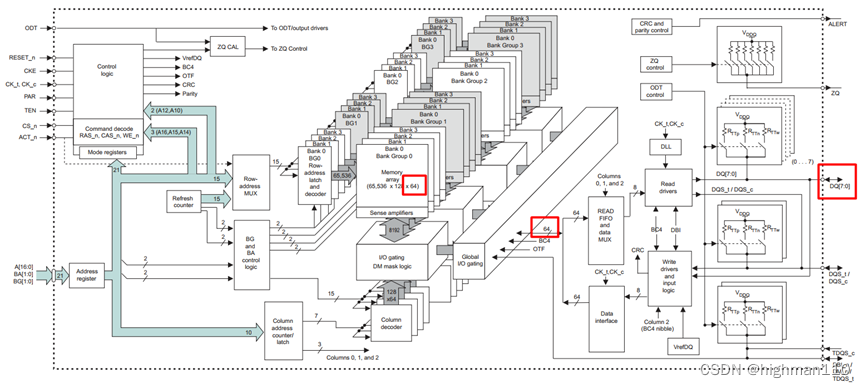

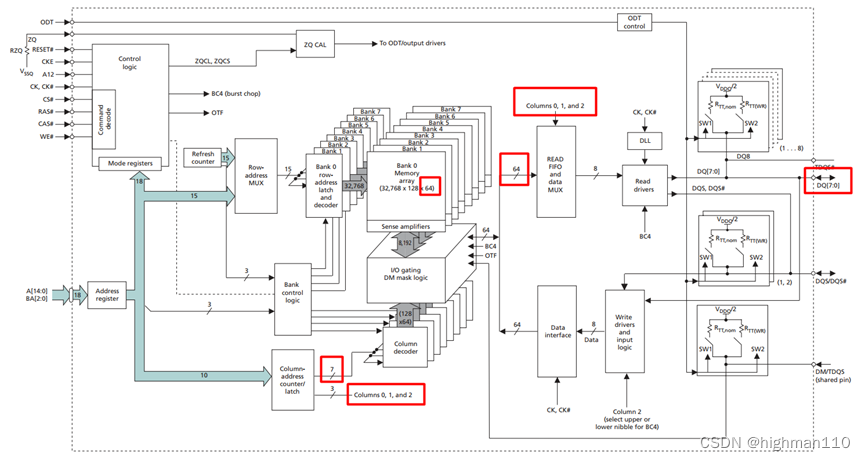

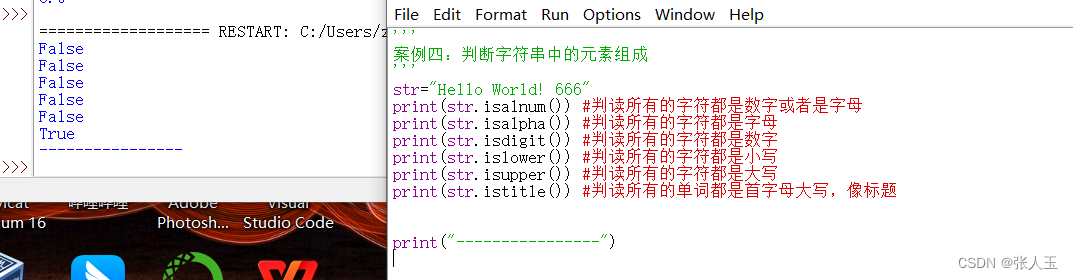

以镁光某4Gb DDR4颗粒的框图为例:

可以看到上图左侧为颗粒的外部引脚信号,包括左上部分的控制信号,左下部分的地址信号,以及右边的数据信号;外部地址信号进来后进入到bank group、bank、行地址和列地址选择控制逻辑;再往中间就是按bank group、bank组织起来的一张张存储阵列,上图一个bank中的65536 x 128 x 32表示,这一个bank由32张65536行 x 128列的存储阵列叠起来组成,这里一共有16个bank,每4个bank组成一个bank group。在访问存储阵列时,通过BG[1:0]信号选择bank group,通过BA[1:0]信号选择bank,通过分时复用的A[16:0]选择行和列,这时某个bank内的32张存储阵列同时被选中了一个行地址相同和列地址相同的存储单元,一次性就能访问32bit数据,而外部数据引脚DQ为4bit,这就是DDR4的8n预取。上图中每个bank的行地址数为2^16=65536,列地址数为2^7=128,这里留了3bit列地址没有直接映射到bank位线的选择上,原因就是DDR4的8n预取,需要一次性取出外部DQ引脚数*8这么多比特数据,同时因为存储阵列的位线不宜太多,因为每一组位线都要搭配感应放大器和位线选择等逻辑,为了使x4、x8、x16颗粒的复用度更高,所以都使用了128根位线的存储阵列,再通过在一个bank内叠不同数量的存储阵列来达成一次性预取8n bit数据的目的。

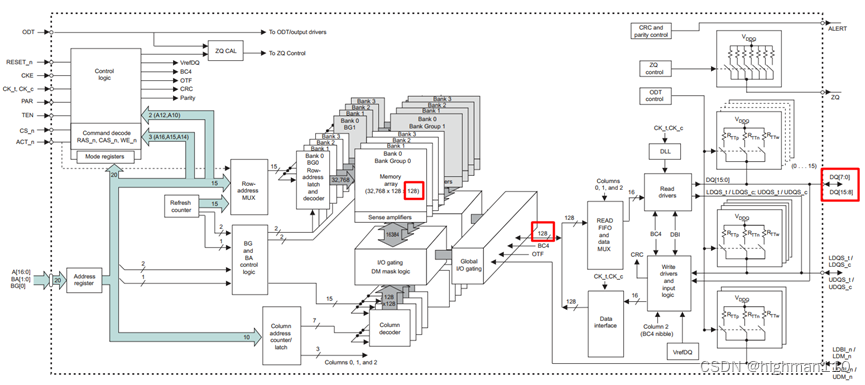

如果是x8的颗粒,就要求要预取64bit数据,也就是x8颗粒一个bank是由64张存储阵列组成,如下图(注意下图每个bank的行地址数65536应该标错了,实际应为2^15=32768):

如果是x16的颗粒,则要求要预取128bit数据,也就是x16颗粒一个bank是由128张存储阵列组成,注意,x16的DDR4颗粒只有2个bank group,x4和x8颗粒则有4个bank group,如下图:

颗粒寻址和容量说明

颗粒寻址和容量说明

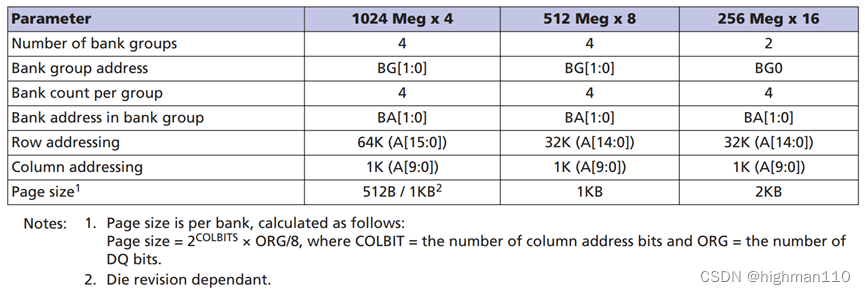

如下为该4Gb颗粒的寻址说明,一般情况下,不同容量的颗粒,列地址线是相同的10根,用高7位地址线来做存储阵列位线(128根)寻址,用低3位来做预取后的数据输出选择,bank地址线也是相同的,每个bank group固定为4个bank。其他寻址线,如行地址、bank group选择,根据容量不同有所区别。

解释一下上图中的page size,这里的page概念和我们之前讲的flash存储阵列中的page类似,都是选中的某行地址下,包含的所有存储单元,比如x4颗粒page size=128(一个存储阵列的位线数)*32(一个bank内的存储阵列数)=4096bit=521B,x8颗粒page size=128*64=8192bit=1024B,x16颗粒page size=128*128=16384bit=2048B,这样解释是不是就很清晰了,手册中的注释虽然算出来的结果是一样的,但是为什么这么算没有解释。

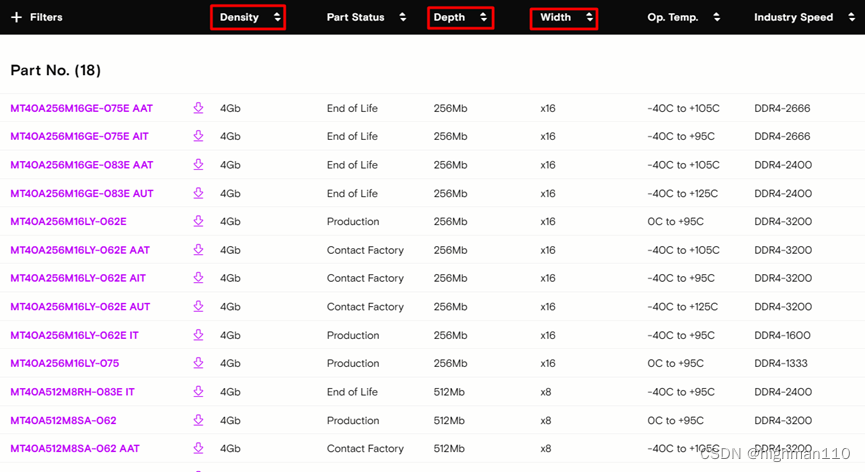

另外内存颗粒还有一个存储深度depth的概念。从计算上来说,深度=容量/数据位宽,我思考了半天,没有想出来这个深度在物理结构上是个什么概念,欢迎大佬指教。

其他颗粒的内部结构

为了映证以上所说的bank内存储阵列数量与外部数据引脚的倍数关系是不是确实就等于预取的倍数,我们继续下载了镁光DDR(2n预取)、DDR2(4n预取)、DDR3(8n预取)的数据手册查看下框图。

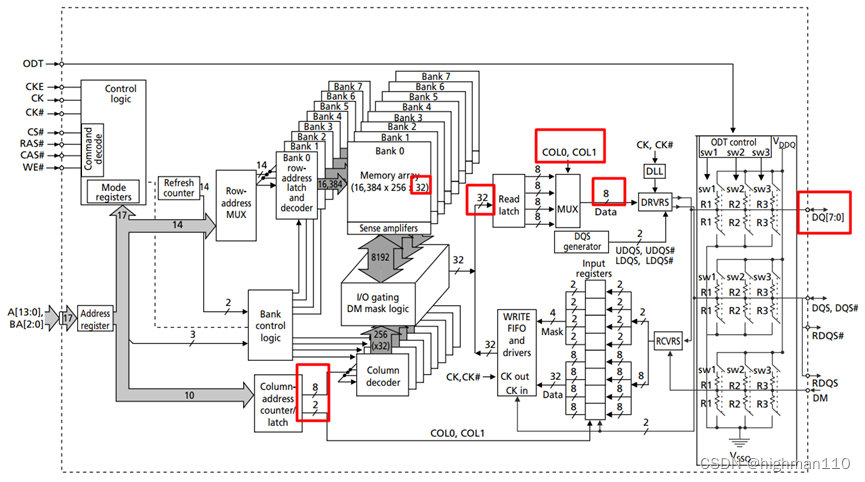

如下为x8 DDR3颗粒框图,可以看到DDR3颗粒没有bank group,每个bank的阵列数量为64,等于8倍DQ数,也就是8n预取:

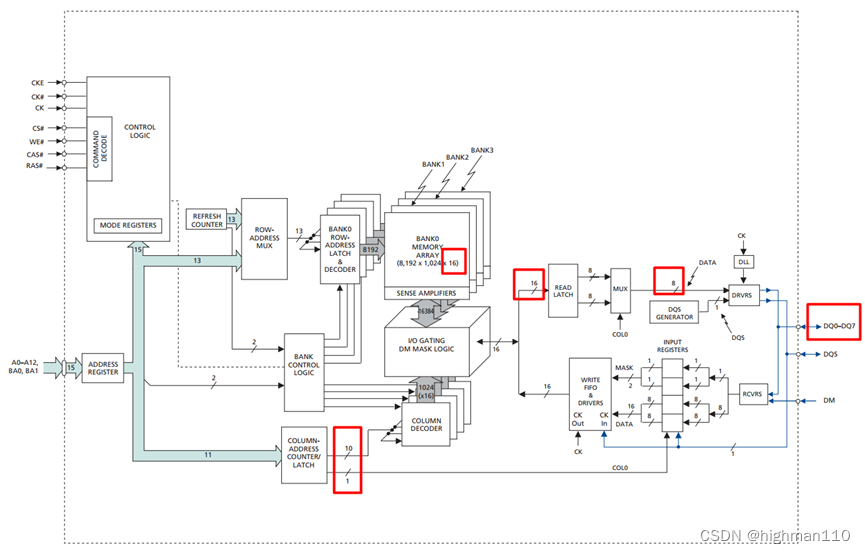

如下为x8 DDR2颗粒框图,可以看到每个bank的阵列数量为32,等于4倍DQ数,也就是4n预取:

如下为x8 DDR颗粒框图,可以看到每个bank的阵列数量为32,等于2倍DQ数,也就是2n预取:

如下为x8 DDR颗粒框图,可以看到每个bank的阵列数量为32,等于2倍DQ数,也就是2n预取:

今天的介绍先到这里。

![[SSM]Spring6整合JUnit5与集成MyBatis3.5](https://img-blog.csdnimg.cn/f31859d78ada4fba96717720bdd693f1.png)

![最适合新手的Java项目/SpringBoot+SSM项目《苍穹外卖》/项目实战、笔记(超详细、新手)[持续更新……]](https://img-blog.csdnimg.cn/9b88e095844946b8873fc535ef3e99e4.png)