MIPI协议 D-PHY基础介绍

- 前言

- 一、MIPI介绍

- 1.1 D-PHY MIPI 简单介绍

- 1.2 C-PHY MIPI 简单介绍

- 1.3 M-PHY MIPI 简单介绍

- 二、D-PHY具体介绍

- 2.1 DSI分层结构

- 2.2 D-PHY电气特性介绍

- 2.3 D-PHY 工作模

- 三、LINE线上的模式

- 3.1 line线上 state code

- 3.2 high speed data line传输

- 3.3 Low Power data line 传输

- 3.4 双向传输 Data Lane Turnaround

- 四、Data Line Escape mode

- 4.1 entry Escape mode

- 4.2 Ultra-Low Power State

- 五、D-PHY Clock Lane

- 5.1 Clock Lane High-Speed And Low-Power

- 5.2 Clock Lane 进入 Ultra-Low Power State

- 六、争用监测(Contention Detection)

前言

下面为mipi相关知识介绍,主要为D-PHY的结构分析,内容并非原创,借鉴了多位博主的分享,在此表示感谢。

MIPI协议之D-PHY协议详解

MIPI介绍(CSI DSI接口)

MIPI基础-简单介绍

一、MIPI介绍

MIPI(Mobile Industry Processor Interface)是2003年由ARM, Nokia, ST ,TI等公司成立的一个联盟,目的是把手机内部的接口如摄像头接口、显示屏接口、射频/基带接口等标准化,从而减少手机设计的复杂程度和增加设计灵活性。MIPI联盟下面有不同的WorkGroup,分别定义了一系列的手机内部接口标准,比如摄像头接口CSI、显示接口DSI、射频接口DigRF、麦克风/喇叭接口SLIMbus等。统一接口标准的好处是手机厂商根据需要可以从市面上灵活选择不同的芯片和模组,更改设计和功能时更加快捷方便。

MIPI可主要分为物理层和逻辑层两大部分:

MIPI按照物理层(Physical Standard)划分可分为:D-PHY、C-PHY、M-PHY三种

1.1 D-PHY MIPI 简单介绍

D-PHY的逻辑层主要是面向摄像头(CSI)、显示屏(DSI)等用途,D-PHY中的D是罗马数字500的意思,D-PHY最初版本是可以支持500Mbits/s。D-PHY采用差分信号传输方式(不全是差分,LP是单端传输),每条lane由2根信号线组成,分别是P和N,clock lane是必不可少的,data lane的数量可以根据数据传输的吞吐率来选择,至少要有一个data lane。

1.2 C-PHY MIPI 简单介绍

C-PHY类似于D-PHY,其逻辑层主要也是面向摄像头(CSI)、显示屏(DSI)等用途,C-PHY中的C指的是Channel-limited。C-PHY总共有3条lane,每条lane使用3根信号线,3条信号线彼此差分。C-PHY没有单独的clock,时钟信号是包含在通讯的时序中。

1.3 M-PHY MIPI 简单介绍

C-PHY类似于D-PHY,其逻辑层主要也是面向摄像头(CSI)、显示屏(DSI)等用途,C-PHY中的C指的是Channel-limited。C-PHY总共有3条lane,每条lane使用3根信号线,3条信号线彼此差分。C-PHY没有单独的clock,时钟信号是包含在通讯的时序中。

二、D-PHY具体介绍

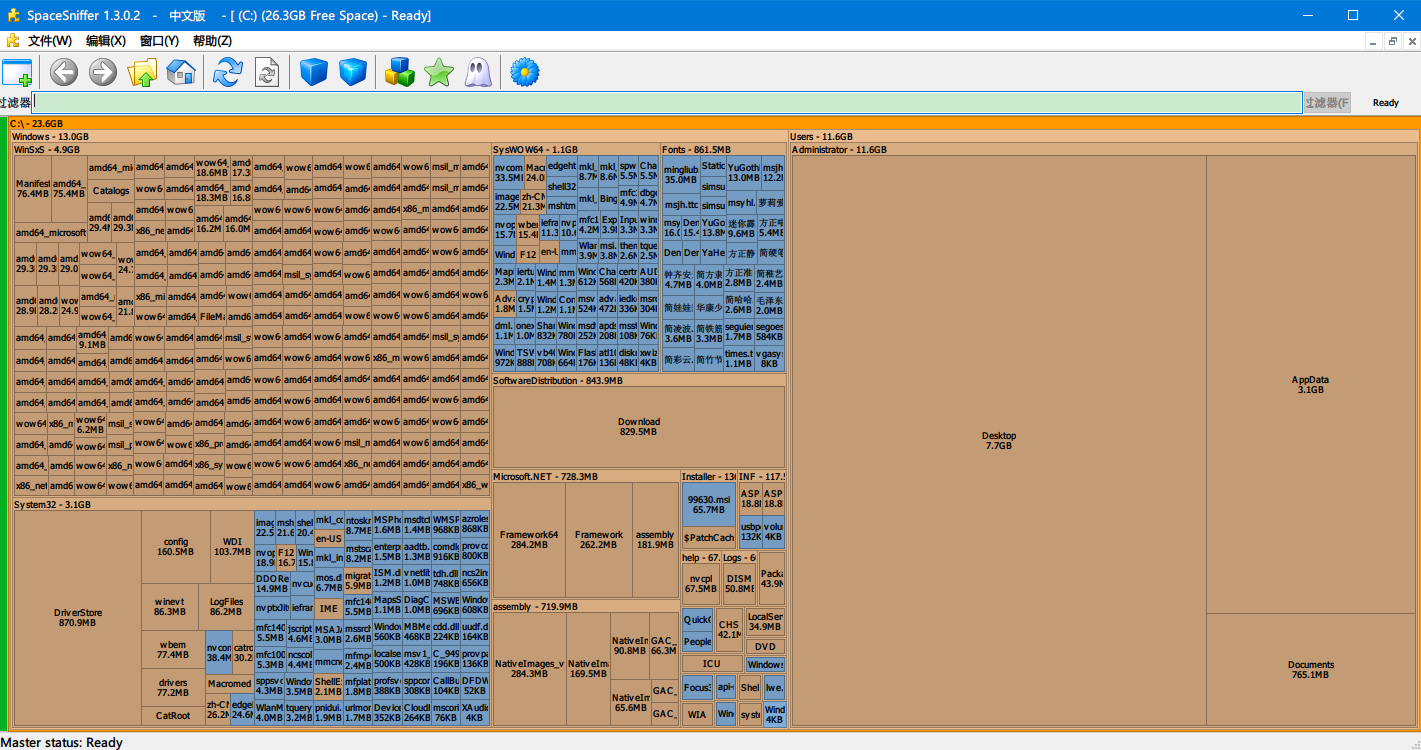

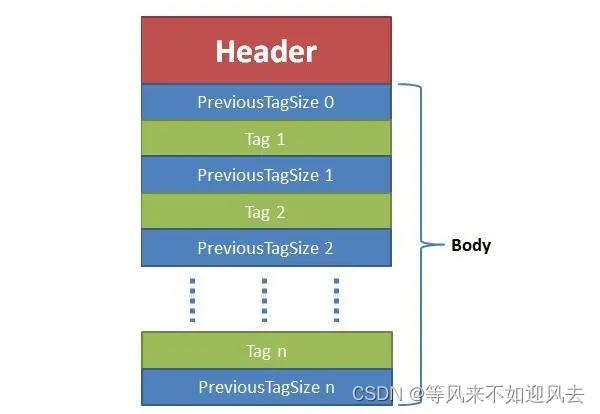

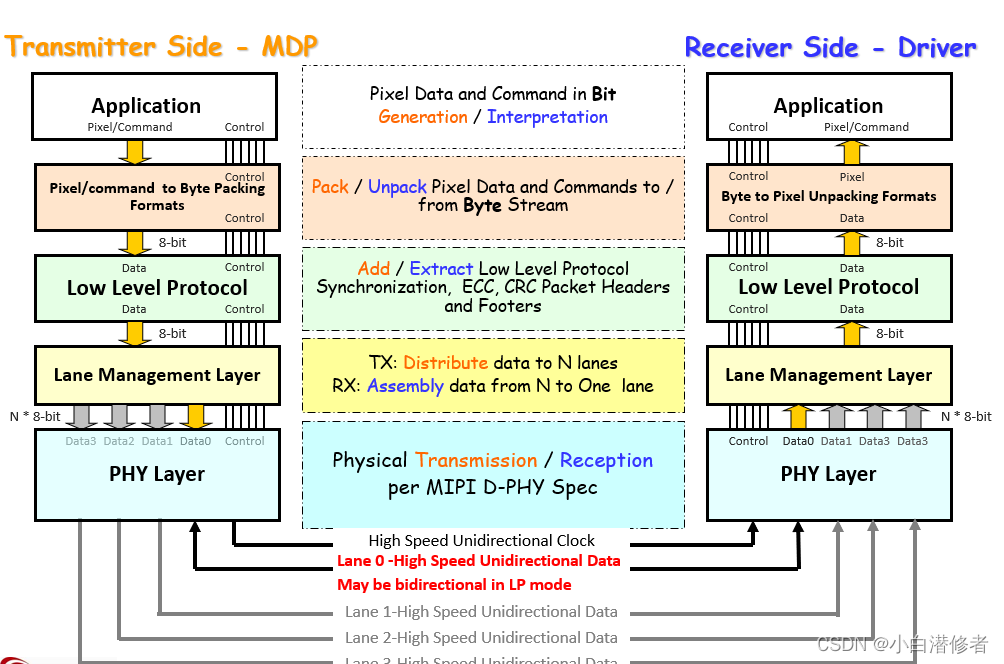

2.1 DSI分层结构

DSI可主要分为应用层、协议层、物理层这三层结构;

其中协议层包含:

1.像素/字节打包/解包层

2.LLP(Low Level Protocol)层

3.LANE管理层

下图所示,为结构图

2.2 D-PHY电气特性介绍

D-PHY包含如下几种电气功能:

1.低功耗发送器-Low Power Transmitter(LP-TX)

2.低功耗接收器-Low Power Receiver (LP-RX)

3.高速发送器-High Speed Transmitter (HS-TX)

4.高速接收器-High Speed Receiver (HS-RX)

5.低功耗竞争检测器-Low Power Contention Detector (LP-CD)Clock 信号是单向信号,只能Master向Slave提供,永远不变。

Data信号可以是单向信号,也可以是半双工信号,即可以反向传输。反向传输的本质其实是通过Master去读Slave里的数据。这种半双工的双向信号的数据传送,在反向传输数据的时候(Slave To Master),带宽只有正向传输(Master To Slave)的四分之一。

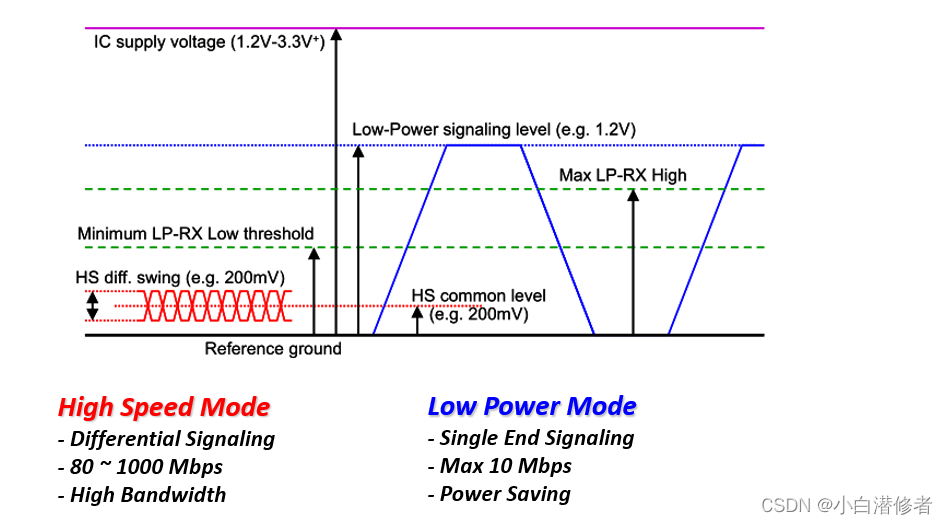

2.3 D-PHY 工作模

MIPI D-PHY的时钟工作方式类似于DDR的时钟工作方式,一个clock周期内,上升沿和下降沿都采集数据,有High speed (HS)和low power(LP)两种工作方式,HS支持的最大数据传输速率为80Mbps-4.5Gbps,LP模式最大速率到达10Mbps,这两种工作模式会混合在一起工作,有高数据量数据传输时会从LP模式转换为HS模式,当数据传输完毕会从HS模式转换到LP模式,减少功耗,一般使用1对clock lane搭配4对data lane,这里需要10个pin脚。

1.High Speed Mode (HS) 高速模式

HS高速传输模式:

用于传输突发数据,同步传输,信号为差分信号,电平范围为100mV-300mV,传输速度范围为80M-1Gbps,在该模式下传输时当差分线上正端收到300mV信号,负端收到100mV信号时,此时接收端识别为1,反之为0。

下图中左侧为发送数据端,也就是master端,有两个类似于推挽的结构,右侧为差分信号接收端,由两个端接电阻与端接使能信号组成,工作模式为:以差分的D+信号为例,当K2和K4打开之后,电压经过线连接到了端接电阻,当端接使能打开之后,上下两个端接电阻形成回路,这就形成了差分信号正的变化,当K2,K4关闭之后,形成差分信号负的变化,D-由K1和K3控制,是一个相反过程。

2.Low Power Mode (LP) 低功耗模式

LP低功耗模式:

用于传输控制指令,异步传输信号为单端信号,电平范围为0-1.2V,没有用时钟线,时钟是通过两个数据线异或而来的速度小于等于10Mbps,在该模式下传输时,当正端接收到1.2V,负端接收到0V时接收端识别为1,反之识别为0。

与HS模式不同,RX这端不需要端接,是无穷大的,只需要控制TX这端做出相应的变化即可,当需要输出LP的high,即输出1.2V,只需要控制上面的开关打开,则D+为1.2V,当需要控制输出低电平时,则需要将下面的开关打开,从而实现端点电压为低的目的,从而实现电压的高低变化,由于在LP模式下D+和D-为单端信号,所以D+和D-单独控制即可。

注意:无论是HS模式还是LP模式,都采用 LSB fisrt,MSB last 的传输方式。

三、LINE线上的模式

Line线上的模式可由下图所概括:

3.1 line线上 state code

HS-0:表示High-Speed模式下,Dp那根线的数据是0,由于High-Speed是差分信号,那么Dn就是1。

HS-1:表示High-Speed 模式下, Dp那根线的数据是1,由于High-Speed是差分信号,那么Dn就是0。

在Low-Power模式下,Lane的2根线是独立的,不代表差分信号,那么2根线就有4种表达方式:

LP-00:表示在Low-Power模式下,Dp那根线的数据是0,Dn那根线的数据是0。

LP-01:表示在Low-Power模式下,Dp那根线的数据是0,Dn那根线的数据是1。

LP-10:表示在Low-Power模式下,Dp那根线的数据是1,Dn那根线的数据是0。

LP-11:表示在Low-Power模式下,Dp那根线的数据是1,Dn那根线的数据是1

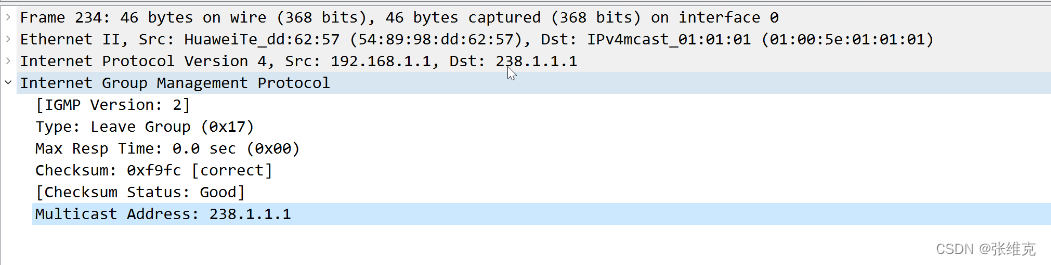

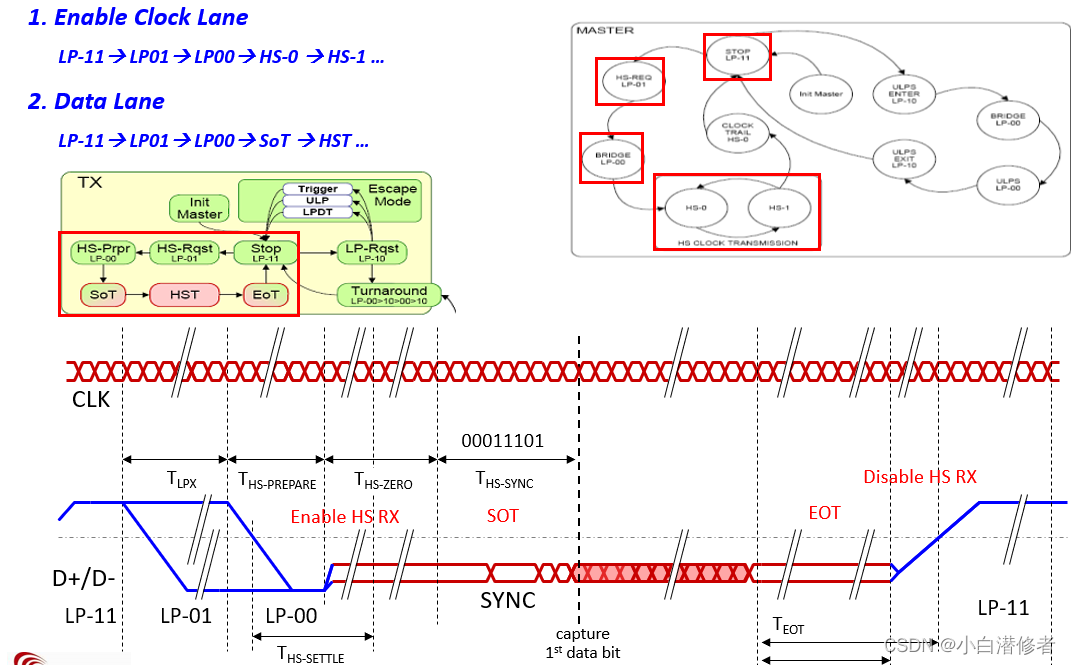

3.2 high speed data line传输

MIPI的D-PHY规定,一个Data Lane进入 High-Speed的方式为发送一个Start-Of-Transmission Sequence即 SOT 信号,这个 SOT 信号的组成如下所示:

从上面图中我们可以看出发送状态码变化为:LP-11、LP-01、LP-00、HS-0、发送 HS Sync 00011101序列,然后发送数据则进入了HS模式,发起了 High-Speed Transmission 。

3.3 Low Power data line 传输

low power data line 传输方式和HS传输类似,从发生状态码上来讲则更为简单,发送LP11则为EOT(End-of-Transmission)

3.4 双向传输 Data Lane Turnaround

注意在双向传输模式下,主从关系还是不变

状态变化为 LP-11、LP-10、LP-00、LP-10、LP-00、Wait ACK(接收 LP-00)、接收 LP-10、接收 LP-11。

四、Data Line Escape mode

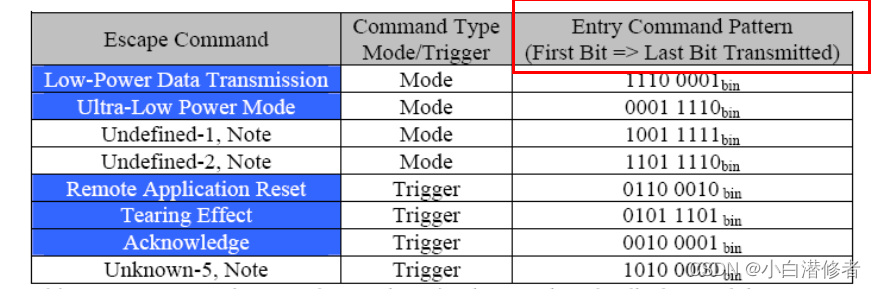

Escape Mode 是 Low-Power 的一种,针对 Escape Mode 又细分了好几种,于是我们基于之前的介绍,进行扩展:

1)Low-Power Data Transmission ,简称为 LPDT,意味在 LP 模式下进行数据传输;

2)Ultra-Low Power State:简称为 ULPS,超低功耗状态;

3)Trigger 来说的话,现在只有一个 Trigger 就是 Reset,用于触发 Reset;他们都预留了一些内容,来适应以后的标准升级。

4.1 entry Escape mode

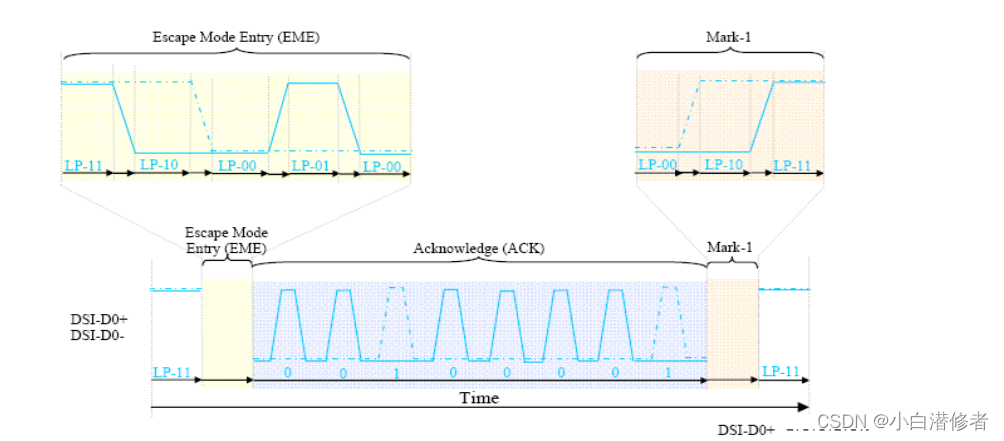

如果要进入 Escape 模式的话,需要通过一个叫 Esccape mode Entry 的流程,这个流程为:LP-11、LP-10、LP-00、LP-01、LP-00;

和之前不一样的是,由于Escape 模式下定义了一些trigger 和mode,在执行完相应的LP-xx状态码后还需在后面加上entry command。

LP-11、LP-10、LP-00、LP-01、LP-00、[Entry Command]

Example:LP11 To Escape Mode(EME)->ACK->LP11

4.2 Ultra-Low Power State

如果在进入 Escape mode 的时候 Entry Command 指定为了 Ultra-Low Power State(ULPS)的话,这个 Lane 将进入 ULPS;

五、D-PHY Clock Lane

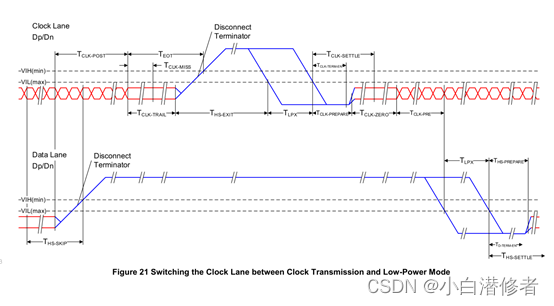

Clock Lane和Data Lane有点不一样,虽然都可以抽象为单端的高速差分信号,Clock Lane 没有Escape模式,但是Clock Lane有ULPS模式;

5.1 Clock Lane High-Speed And Low-Power

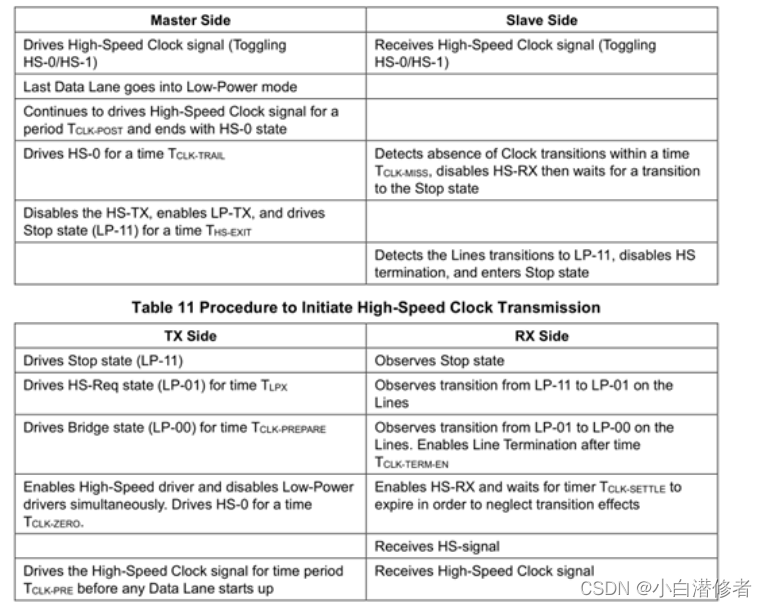

这里我们关注 Clock Lane 和 Data Lane 在进入和推出 Low-Power 的时候的时序可以看到,在 Data Lane 进入 Stop State 的时候,再经过 Tclk-post 后,Clock Lane 才进入 HS-0 的状态,然后在 HS-0 持续 Tclk-trail后,进入到 LP-11 状态;但需要发数据的时候,Clock Lane 先进入 LP-11,然后进入 LP-01 并位处 Tlpx,然后进入 LP-00 并维持一些时间 Tclk-prepare,然后维持 HS-0 ,时间为 Tclk-zero,然后 Clock Lane 就可以正常工作了,在经过 Tclk-pre 后,Data Lane 方可工作;

整个工作流程如下

5.2 Clock Lane 进入 Ultra-Low Power State

进入 Clock Lane 的 Ultra-Low Power State 的方式为:LP-11、LP-10、LP-00

六、争用监测(Contention Detection)

正常情况下,连接的两端,在给定的一个时间内,只能够有一方去驱动线上的信号,当其中一端出现了故障,比如,同一时间,两端同时尝试去驱动同一个 Lane ,或者两端都不驱动这条 Lane,D-PHY 管这种情况叫做 “争用”(Contention);

具备双向通信的 LP Lane,都必须具备 Contention Detection 的能力,并且监测出如下冲突;

1、Modules 两端同时向反向驱动一条线;

2、Modules 一端驱动一条线为 LP-high,同时另一端驱动这条线为 HS-low;

上面的第一种情况,能够被 LP-CD 和 LP-RX 组合起来监测到;

上面的第二种情况,应该能够被 LP-RX 监测到;