各位同学大家好,欢迎继续做客电子工程学习圈,今天我们继续来讲这本书,硬件系统工程师宝典。

上篇我们了解了存储器可分为RAM和ROM,根据不同特性也可以逐级细分,并且简单介绍了EEPROM。今天我们讲一讲FLASH有哪几种?

NOR FLASH

目前常用的FLASH主要有NOR FLASH和NAND FLASH两种

NOR技术(也称Linear技术)源于传统的EEPROM器件,具有高可靠性、随机读取速度快的优势,用于擦除和编程操作较少、直接执行代码的场合,如PC的BIOS固件等。

NOR技术的Flash Memory具有以下特点。

1.程序和数据可存放在同一芯片,拥有独立的数据总线和地址总线,能快速随机读取,允许系统直接从Flash中读取代码执行,无须先将代码下载至RAM中再执行。

2.可以单字节或单字编程,但不能单字节擦除,必须以块为单位或整片擦除,由于采用NOR技术的Flash Memory擦除和编程速度较慢,在纯数据存储和文件存储的应用中,NOR技术显得力不从心。

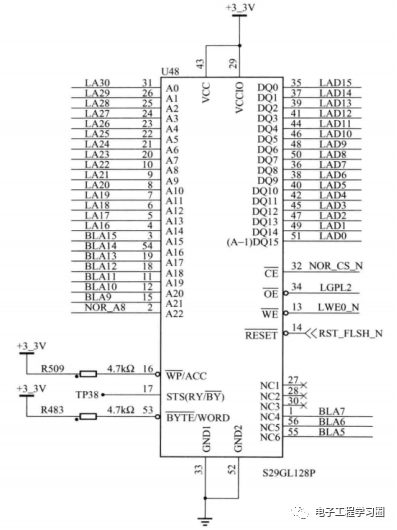

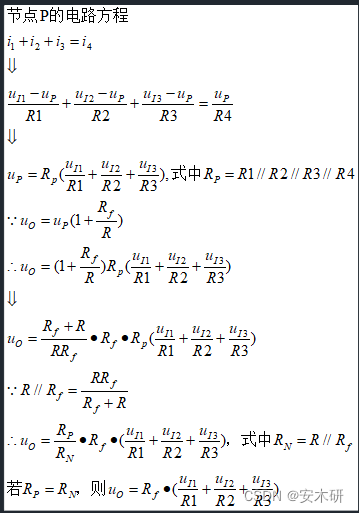

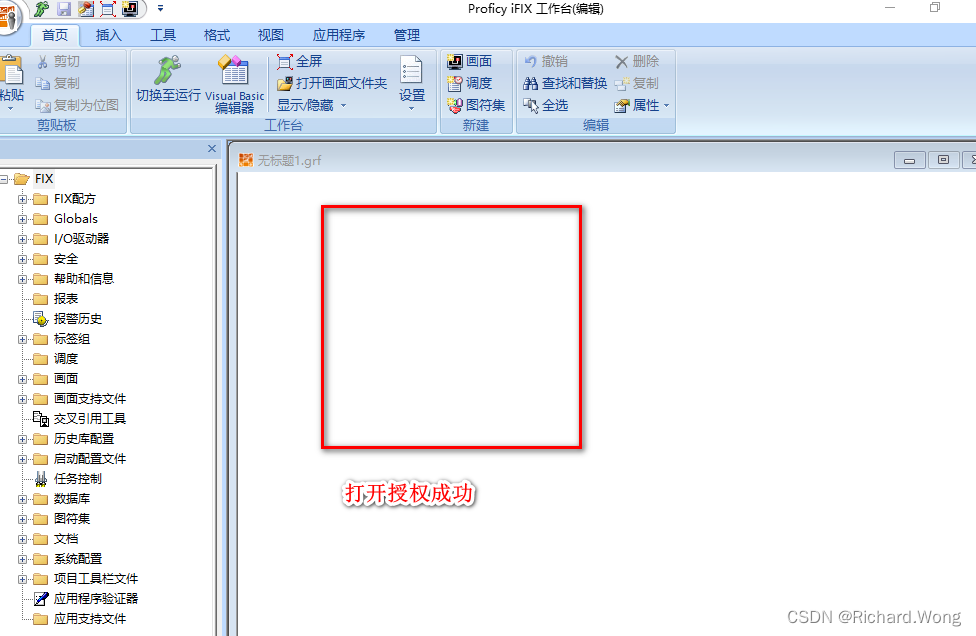

下面以S29GL128P为例说明,NOR FLASH的引脚定义和设计描述。

S29GL128P电路设计

查阅S29GL128P的Datasheet可知:

1.A25~A0是地址信号输入通道,需与CPU的存储专用地址总线相连

2.DQ15,DQ14~DQ0是数据信号,需要与CPU的存储数据总线相连

3.CE为片选信号

4.OE为输出使能信号

5.WE写使能

6.VCC电源输入引脚

7.VIO通用I/O口的供电引脚,接VCC电源输入端

8.VSS低信号引脚

9.NC为不连接的引脚

10.RY/BY为输出信号,当输出低电平时表示器件在进行写入或擦除工作,当输出高电平时表示器件已准备就绪。11.BYTE为输入信号,用于设置输入数据信号的宽度8bit或16bit

12.WP/ACC为写保护或编程加速控制,当为低电平时为写保护功能,当为高电平时为编程加速,在设计时一般都上拉处理。

13.RFU为保留引脚不连接。

NAND FLASH

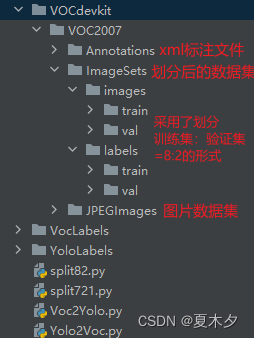

采用NAND技术的Flash Memory的特点

1.NAND FLASH以页为单位进行读和编程操作,1页为256B或512B,因此NAND FLASH不用来直接运行程序,需将代码下载到RAM中再运行。NAND FLASH以块为单位进行擦除操作,1块为4KB、8KB或16KB;具有快编程和快擦除的功能,块擦除时间是2ms,而NOR技术的块擦除时间是几百ms。

2.数据、地址采用同一总线,实现串行读取,随机读取速度慢且不能按字节随机编程。

3.芯片尺寸小,成本低4.芯片包含失效块,其最大数目可达到3~35块取决于存储器密度。失效块不会影响有效块的性能。设计者需要将失效块在地址映射表中屏蔽起来。

从存储单元的角度考虑,NAND FLASH可分为SLC(Single Level Cell,单层单元)和MLC(Multi-Level Cell,多层单元)。SLC的特点是成本高、容量小、速度快,而MLC的特点是容量大、成本低,但是速度慢。MLC由于存储单元中存放资料较多,结构相对复杂,出错的概率增加,必须进行错误修正,这个修正的动作使得MLC的性能大幅落后于SLC闪存。实际使用时,需要根据程序运行的机制及需求选择合适的Flash存储。

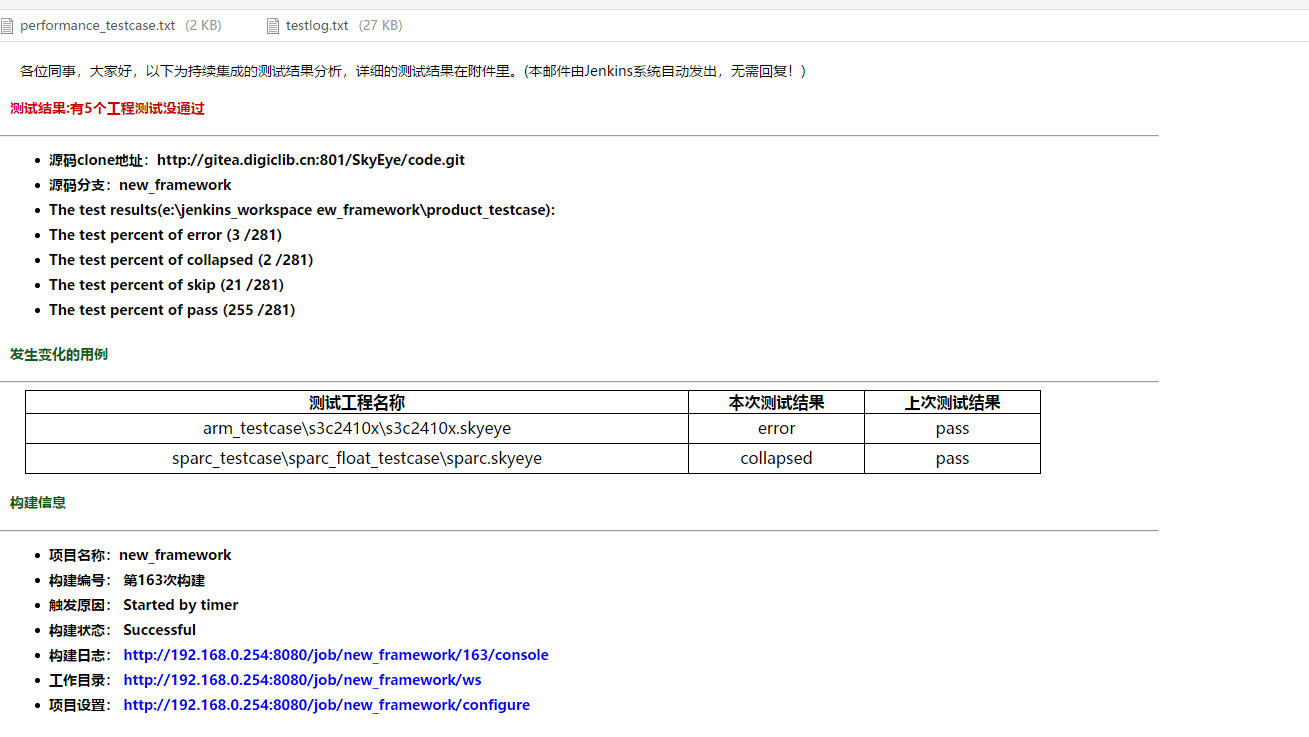

下面作者举例了K9F2G08U0C的引脚和电路设计

K9F2G08U0C-S NAND FLASH的电路设计

K9F2G08U0C是Samsung的一款采用SLC架构的2GB NAND FLASH,如上所示为K9F2G08U0C的电路设计:1.I/O[7:0]:数据的输入/输出引脚,输入数据的内容包含命令、地址和数据,当进行读取操作时向外输出数据。

2.CLE:命令加载使能,CLE高电平有效,当写使能有效时,通过I/O[7:0]将命令加载到NAND FLASH。

3.ALE:地址加载使能,CLE高电平有效,当写使能有效时,通过I/O[7:0]将地址加载到NAND FLASH。

4.CE:片选信号,低电平有效,当不片选芯片时,I/O口的逻辑状态为高阻态。

5.RE:读取数据使能,低电平有效。

6.WE:写数据使能,低电平有效。

7.WP:写保护,在电路设计中一般上拉处理。

8.R/B:可以输出两种状态,用于指示芯片工作或禁止状态。

9.VCC/VSS:电源网络/地网络10.NC:没有连接。

另外,整理了一些电子工程类的资料,分享给大家,目前有模拟电路、单片机、C语言、PCB设计、电源相关、FPGA、EMC、物联网、Linux相关学习资料,还有针对大学生的资料包,后续还会有更多资料分享给大家,助力大家学习,成就梦想~

关注同名公众号领取资料~

链接也可在往期文章中找(在文章的最后有链接)~

模拟电路设计的九个级别,你是模电几段?

![[Linux]进程间通信](https://img-blog.csdnimg.cn/img_convert/e6fe24a78706bc605f79d5dcc4e6ef9e.png)