目录

一、建立HPS硬件系统模型

1.1 GHRD

1.2 从0开始搭建HPS

1.2.1 FPGA Interfaces

1.2.1.1 General

1.2.1.2 AXI Bridge

1.2.1.3 FPGA-to-HPS SDRAM Interface

1.2.1.4 DMA Peripheral Request

1.2.1.5 Interrupts

1.2.1.6 EMAC ptp interface

1.2.2 Peripheral Pin Multiplexing

1.2.3 HPS Clocks

1.2.3.1 Input Clocks

1.2.3.2 Output Clocks

1.2.4 SDRAM

1.2.4.1 PHY Settings

1.2.4.2 Memory Parameters

1.2.4.3 Memory Timing

1.2.4.4 Board Settings

1.3 添加其他组件

1.4 产生Qsys系统

1.5 编译Quartus工程

1.6 硬件系统外设的输入/输出测试

1.7 相关代码

一、建立HPS硬件系统模型

建立HPS硬件模型有两种方式,一种是在GHRD中添加或修改,另外一种是从0开始搭建HPS

1.1 GHRD

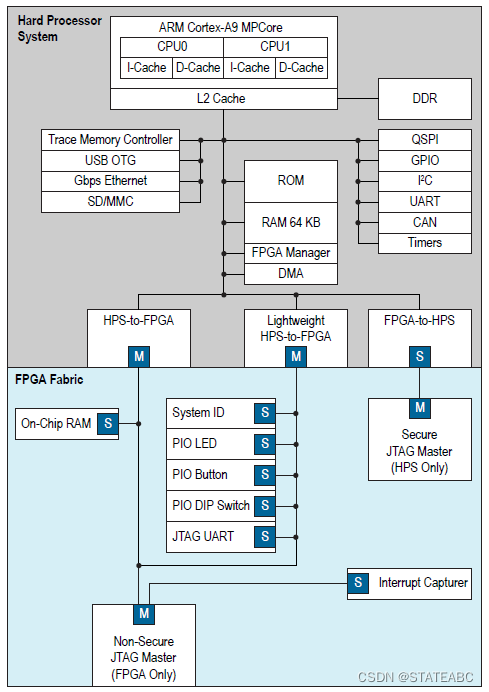

GSRD(Golden System Reference Design, 黄金系统参考设计)包含:

- GHRD(Golden Hardware Reference Design, 黄金硬件参考设计)

- 基于U-Boot的Bootloader参考

- Linux BSP参考

- Linux应用程序示例

其中GHRD包含 Cyclone V SoC / Arria V SoC Development Kit的完整HPS设计,如双核ARM Cortex-A9 MPCore HPS、用户按键输入(PIO Buttion)、用户拨码开关输入(PIO DIPSW)、LED输出(PIO LED)、64KB片上存储器、JTAG-to-Avalon主接口连接桥(JTAG Master)、JATG-UART调试模块、中断捕获器(Interrupt Capturer)及系统ID(SysID)等。使用时只需在其中添加或修改所需的内容即可。

1.2 从0开始搭建HPS

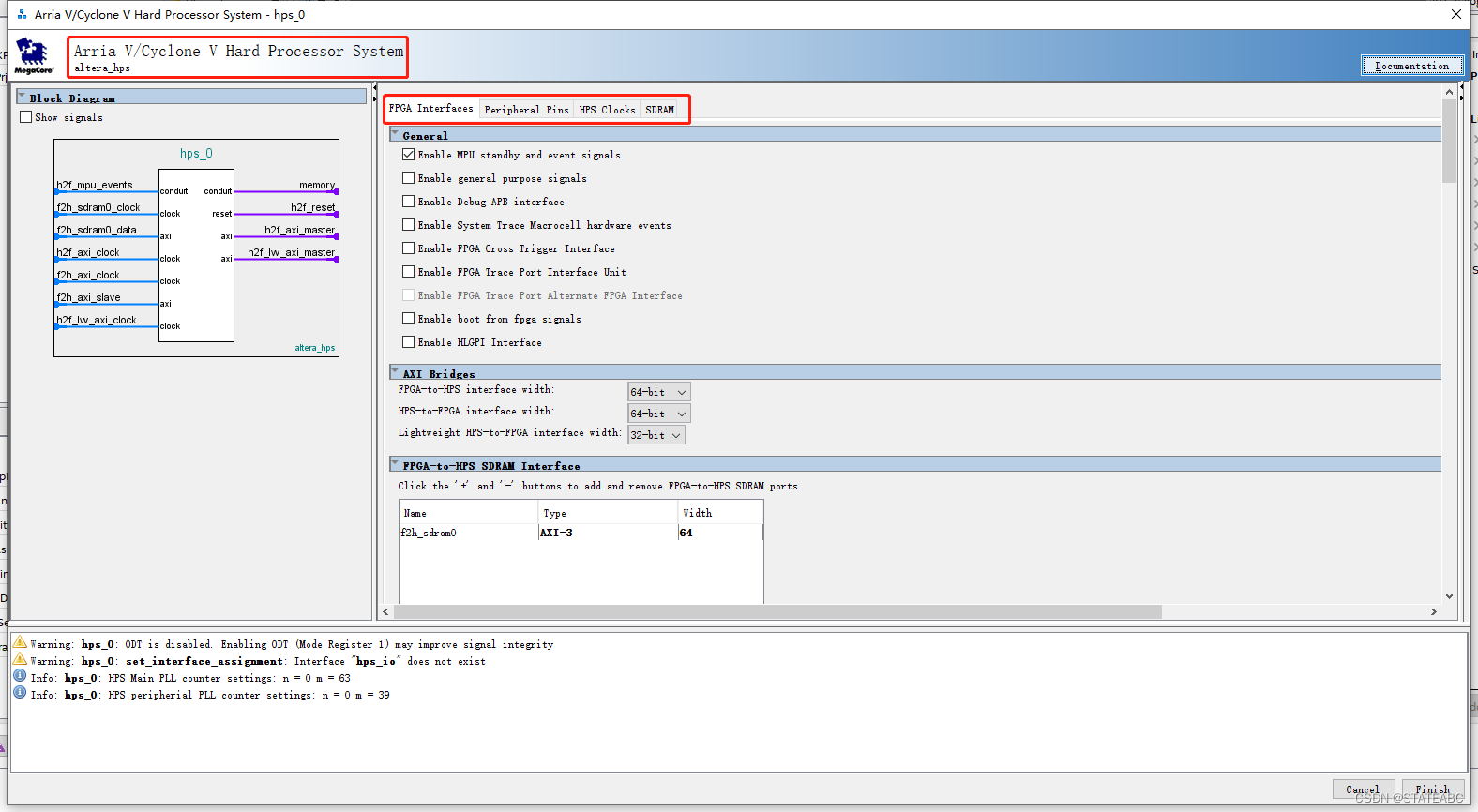

在Quartus中创建工程HPS_Qsys_Prj,进入Platform Designer,添加Hard Processor System组件

1.2.1 FPGA Interfaces

在FPGA Interfaces标签设置页有General、AXI Bridges、FPGA-to-HPS SDRAM Interface、Resets、DMA Peripheral Request、Interrupts、EMAC ptp Interface

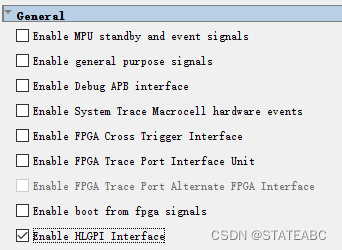

1.2.1.1 General

当General中某些选项被选中,相应的接口会出现在HPS模块中

| 参数名 | 描述 |

| Enable MPU standby and event signals | 通知FPGA接口微处理器单元(MPU)处于待机模式; 可以从等待事件(WFE)状态唤醒一个MPCore处理器 |

| Enable general purpose signals | 在SOC器件的HPS部分,启用FPGA与FPGA管理器之间的一组32位的单向普通目的接口 |

| Enable Debug APB interface | 启用对FPGA的调试接口,允许在HPS中访问调试组件 |

| Enable System Trace Macrocell hardware events | 启用系统跟踪单元(STM)硬件事件,允许FPGA中的逻辑向跟踪过程插入信息 |

| Enable FPGA Cross Trigger Interface | 启用交叉触发器接口(CTI),允许出发Source/Sink与出发的交叉触发(ECT)相连 |

| Enable FPGA Trace Port Interface Unit | 启用跟踪端口接口单元(TPIU)与FPGA逻辑之间的一个接口。TPIU是片上跟踪源与某个跟踪端口之间的桥梁 |

| Enable FPGA Trace Port Alternate FPGA Interface | 当启用跟踪端口时,会创建一个与Arria 10跟踪接口兼容的接口 |

| Enable boot from fpga signals | 启用HPS的一个输入信号,表明是否片上RAM中的preloader可以使用 |

| Enable HLGPI Interface | 启用HPS的GPIO |

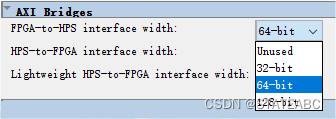

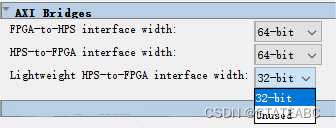

1.2.1.2 AXI Bridge

FPGA-to-HPS interface width和HPS-to-FPGA interface width可选Unused、32-bit、64-bit和128-bit,即FPGA2HPS接口位宽和HPS2FPGA接口位宽。

Lightweight HPS-to-FPGA interface width可选32-bit、Unused,即轻量级LWHPS2FPGA接口位宽。

1.2.1.3 FPGA-to-HPS SDRAM Interface

可以通过添加一个或多个SDRAM从端口(最多6个)让FPGA来访问HPS SDRAM子系统,其数据宽度可选32、64、128或256位,接口类型可选AXI-3、双向Avalon-MM、只写Avalon-MM、只读Avalon-MM。

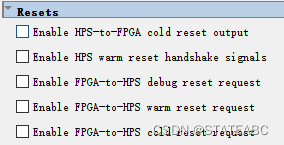

1.2.1.4 Resets

| 参数名 | 参数描述 |

| Enable HPS-to-FPGA cold reset output | 启用HPS2FPGA接口得冷启动输出 |

| Enable HPS warm reset handshake signals | 启用一组附加的复位握手信号,允许软件通知HPS在其安全时开启一个FPGA结构中的热复位信号 |

| Enable FPGA-to-HPS debug reset request | 启用FPGA2HPS调试复位请求接口 |

| Enable FPGA-to-HPS warm reset request | 启用FPGA2HPS热复位请求接口 |

| Enable FPGA-to-HPS cold reset request | 启用FPGA2HPS冷复位请求接口 |

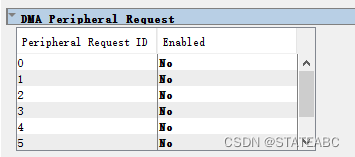

1.2.1.4 DMA Peripheral Request

单独启用每个DMA控制器外设请求ID(Peripheral Request ID),每个请求ID可以使能连接FPGA的8个逻辑DMA通道中对应的通道接口。外设请求ID[4-7]是与CAN控制器共用。

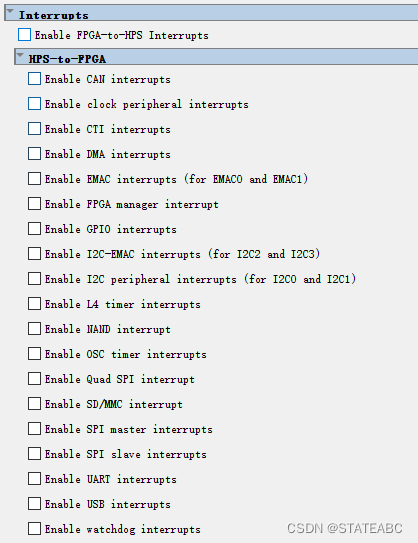

1.2.1.5 Interrupts

对不同中断使能,勾选Enable FPGA-to-HPS Interrupts则启用HPS中FPGA对MPU的中断信号,下方则是HPS中的每个外设提供给FPGA的中断信号

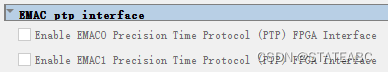

1.2.1.6 EMAC ptp interface

Enable EMAC Precision Time Protocol(PTP) FPGA Interface,启用EMACO精确时间协议 (PTP) FPGA接口,当EMAC通过Pinmux连接到HPS I/O时,可通过FPGA访问IEEE 1588精密时间协议(PTP)接口。当EMAC连接到FPGA时,PTP信号可用。

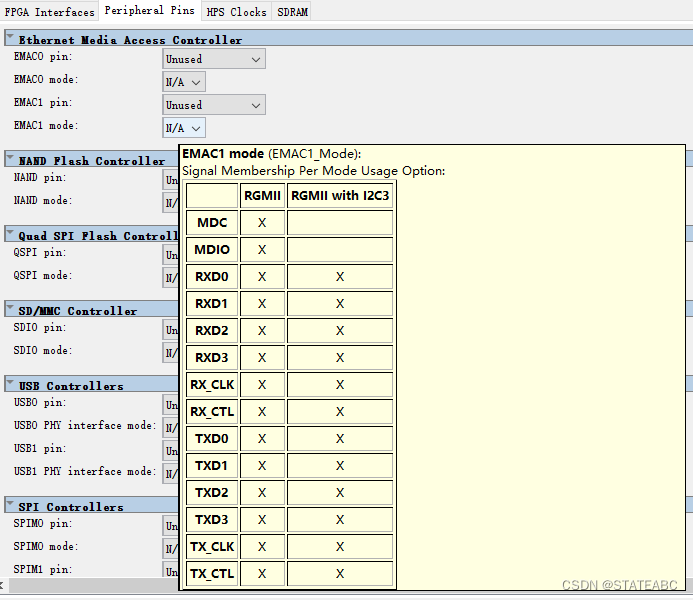

1.2.2 Peripheral Pin Multiplexing

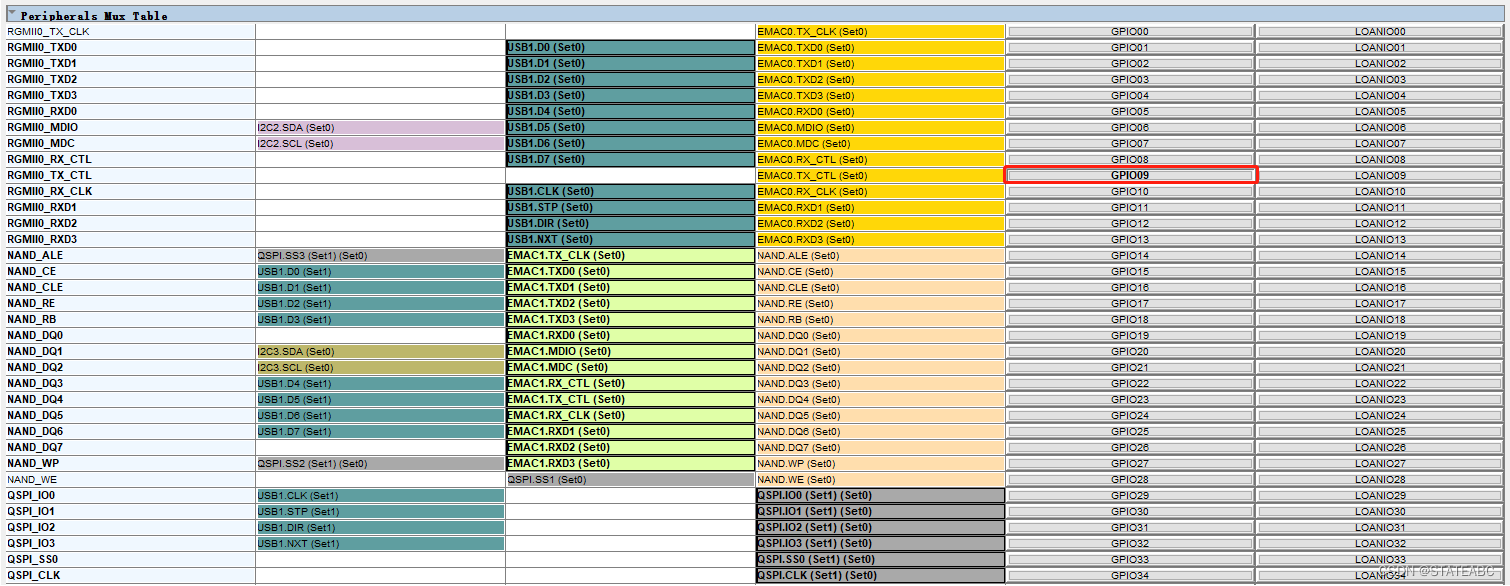

Peripheral Pin Multiplexing标签页包含了HPS所有可用外设的参数设置,通过选择HPS I/O设置可用启用对应的外设。当启用某个外设时,还需要设置其相应的工作模式。将鼠标放到相应的外设模式(mode)设置选项位置几秒时间,即可出现一个下拉列表,下拉列表给出了外设工作模式下的引脚定义。引脚复用设置应该与所用SOC FPGA开发板上的实际外设连接相匹配。

在最下方的Peripherals Mux Table中列出了HPS外设的引脚分配情况,包括没有分配给任何外设的引脚,可以将其作为普通目的I/O(GPIO)使用,点击相对应的后面的GPIO即可。

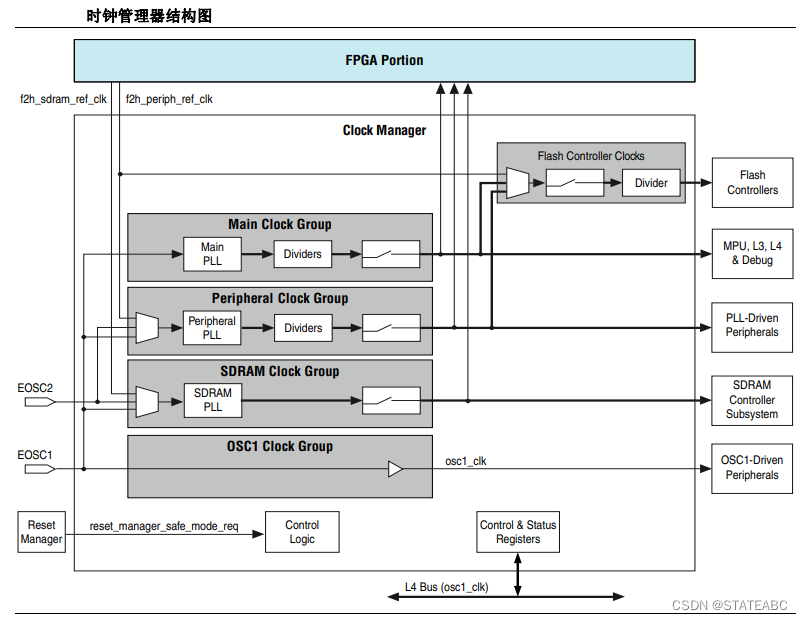

1.2.3 HPS Clocks

HPS Clocks包括Input Clocks和Output Clocks

注意:这里设置的时钟频率是指期望的最高频率,实际时钟频率可以通过MPU上的软件对寄存器的设置进行修改,这里设置的时钟频率将出现在Qsys产生的Synopsys设计约束文件(.sdc)中。

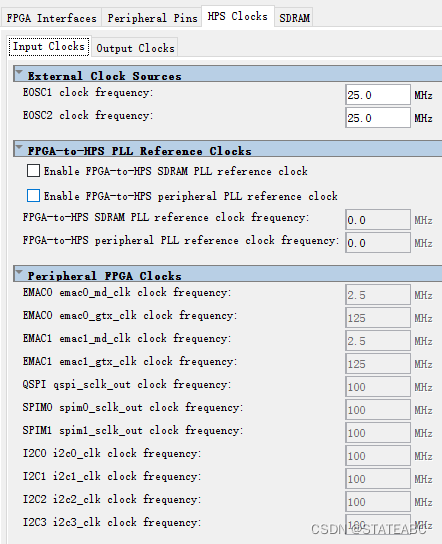

1.2.3.1 Input Clocks

External Clock Sources用于设置E0SC的时钟频率

FPGA-to-HPS PLL Reference Clocks用于启用HPS SDRAM PLL提供参考时钟的FPGA接口、启用HPS外设PLL提供参考时钟的FPGA接口

Peripheral FPGA Clocks用于设置HPS外设的时钟频率,但需要先设置HPS外设在FPGA可以(即相应外设的引脚复用选择FPGA)

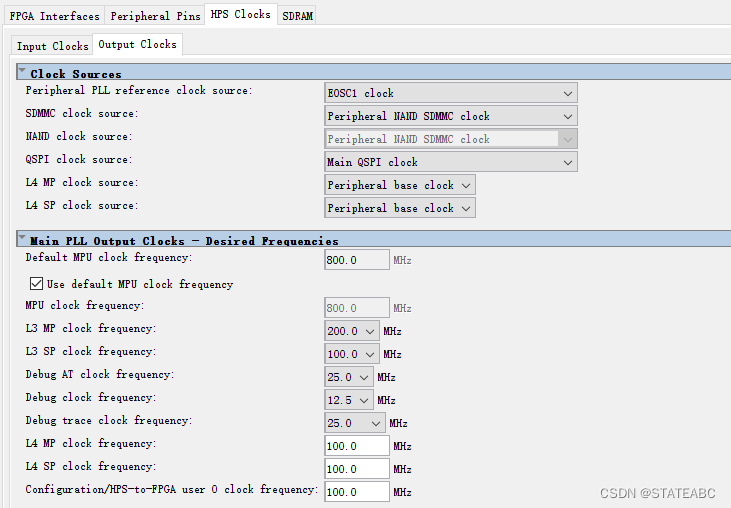

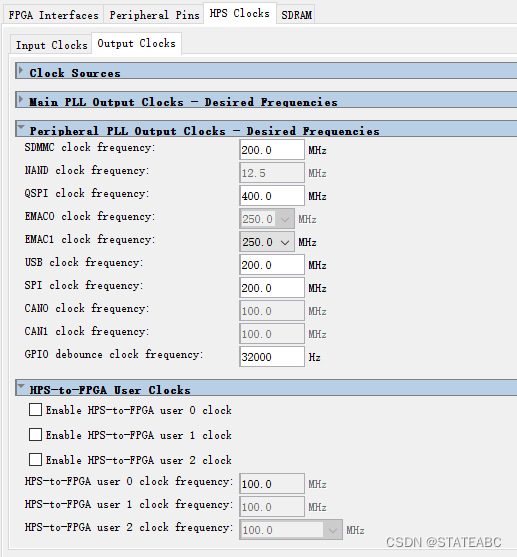

1.2.3.2 Output Clocks

Clock Sources设置时钟源

Main PLL Output Clocks - Desired Frequencies主锁相环输出时钟-所需频率

Peripheral PLL Output Clocks - Desired frequencies外围锁相环输出时钟-所需频率

HPS-to-FPGA User Clocks,用户时钟

| 参数名称 | 参数描述 |

| Enable HPS-to-FPGA user 0 clock | 启用HPS到FPGA的主PLL |

| Enable HPS-to-FPGA user 1 clock | 启用HPS到FPGA的外设PLL |

| Enable HPS-to-FPGA user 2 clock | 启用HPS到FPGA的SDRAM PLL |

1.2.4 SDRAM

HPS支持DDR2、DDR3、LPDDR2协议的存储器接口

1.2.4.1 PHY Settings

Memory clock frequency设置存储器芯片的时钟频率,依据DDR3芯片手册设置

Supply Voltage电源电压,依据DDR3芯片手册选择

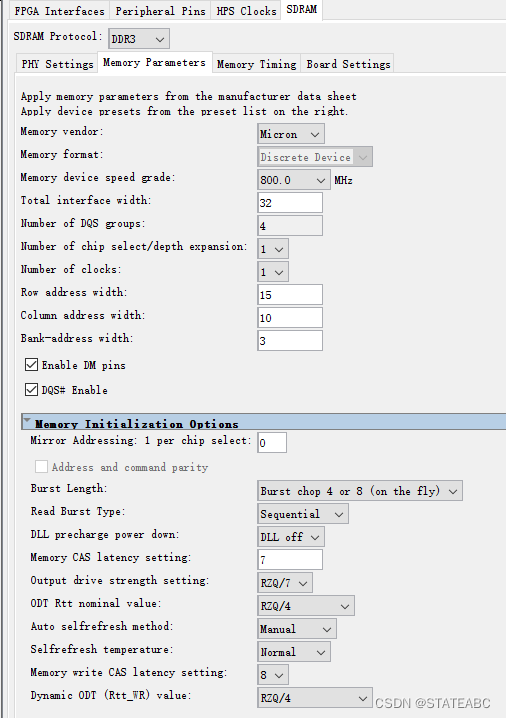

1.2.4.2 Memory Parameters

根据DDR3芯片手册中的参数设置Memory Parameters

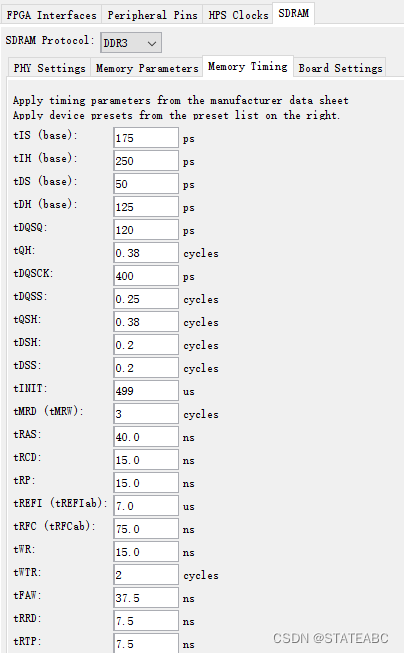

1.2.4.3 Memory Timing

根据DDR3芯片手册中的相关参数验证Memory Timing页面中的时序参数

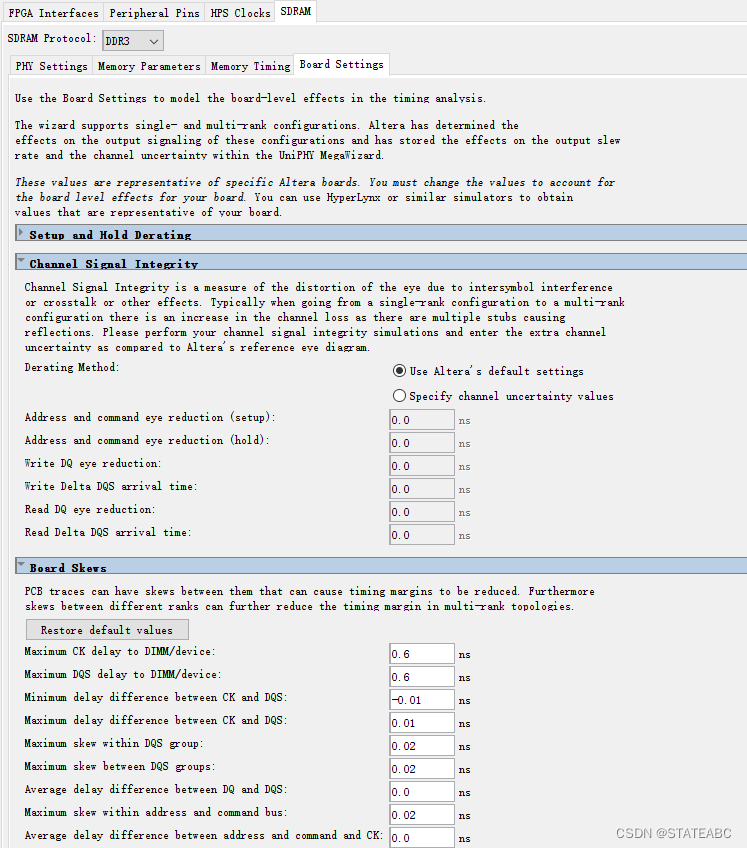

1.2.4.4 Board Settings

Setup and Hold Derating和Intersymbol Interference均可以选择Use Altera's default settings,也可以根据芯片手册中的相关参数进行设置

需要根据开发板参数设置Board Skews,SDRAM利用这些参数校准I/O延时以及FIFO设置来补偿板级、FPGA部分或存储器件的漂移时间

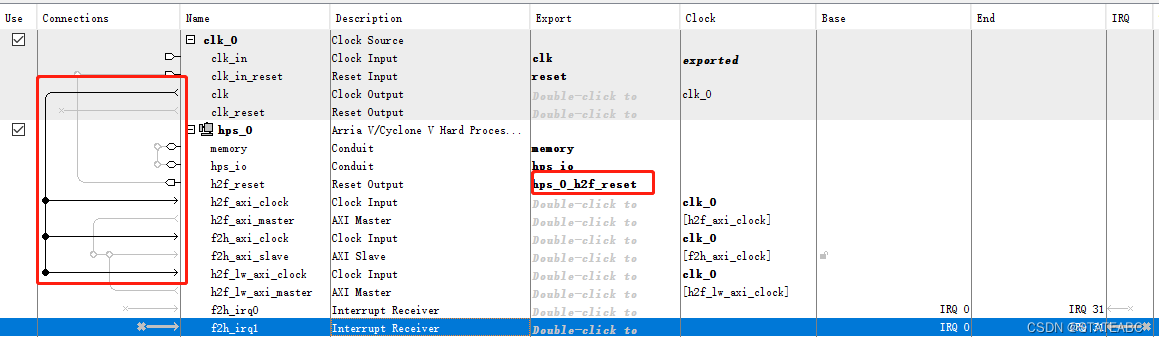

所有设置完成后点击右下角finish,将h2f_reset引出,将三个clock连接clk

1.3 添加其他组件

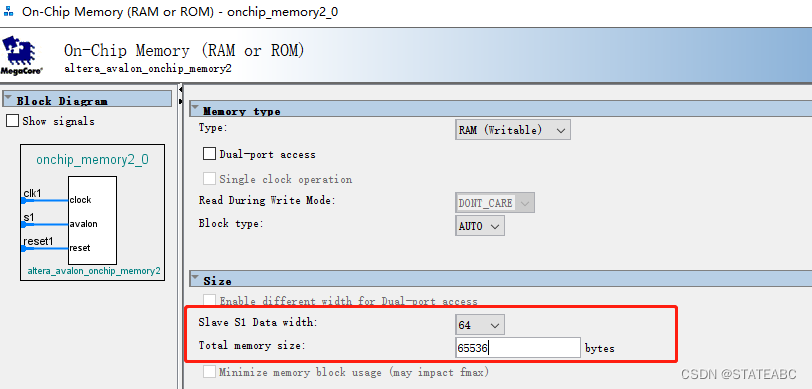

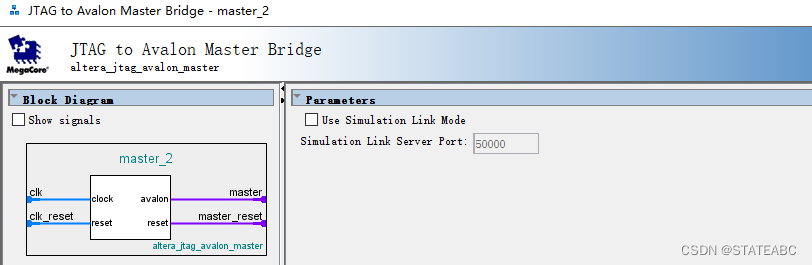

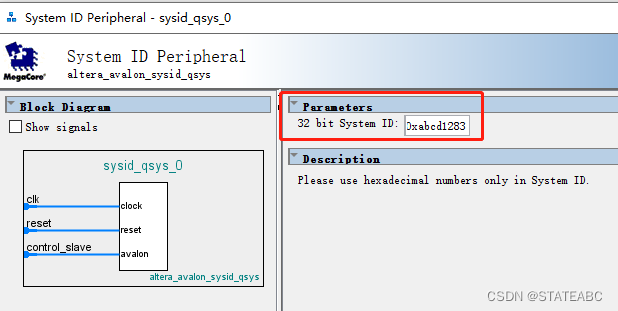

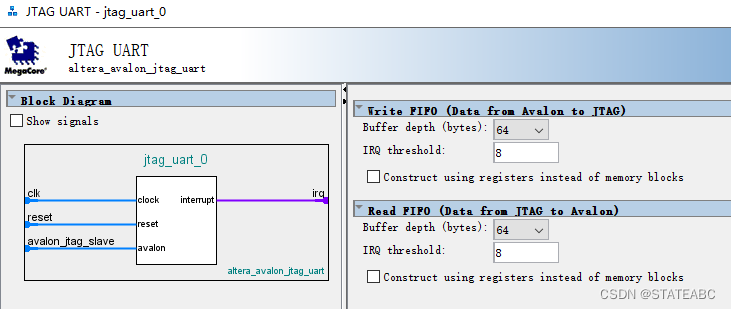

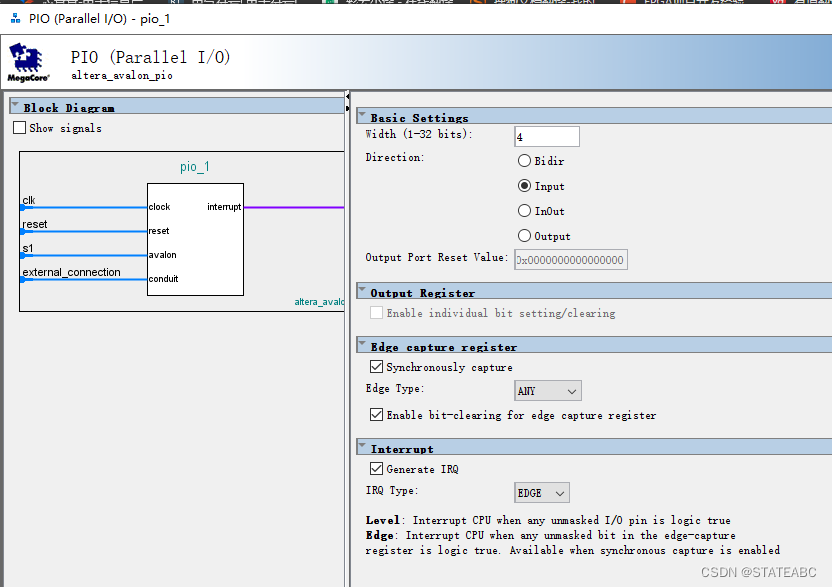

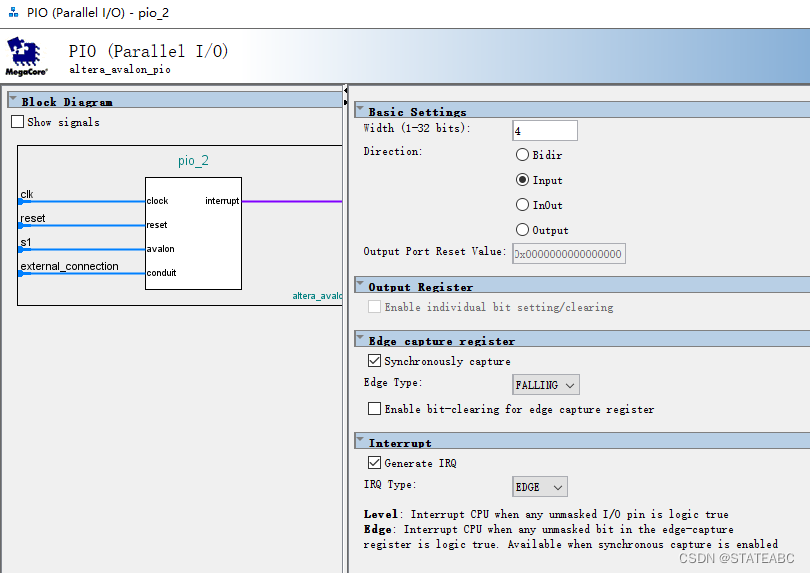

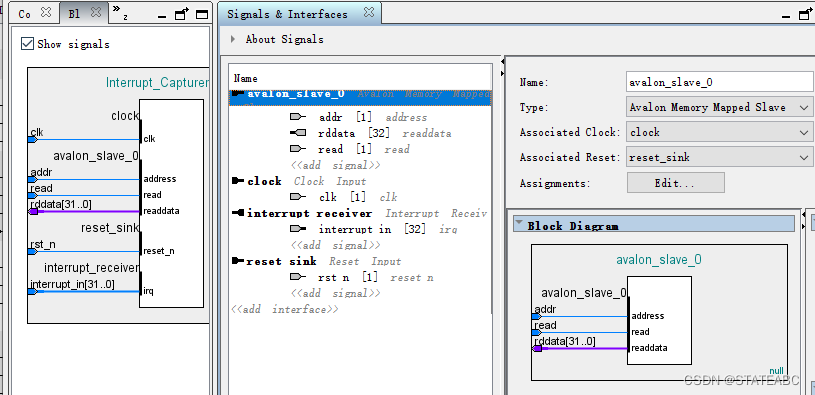

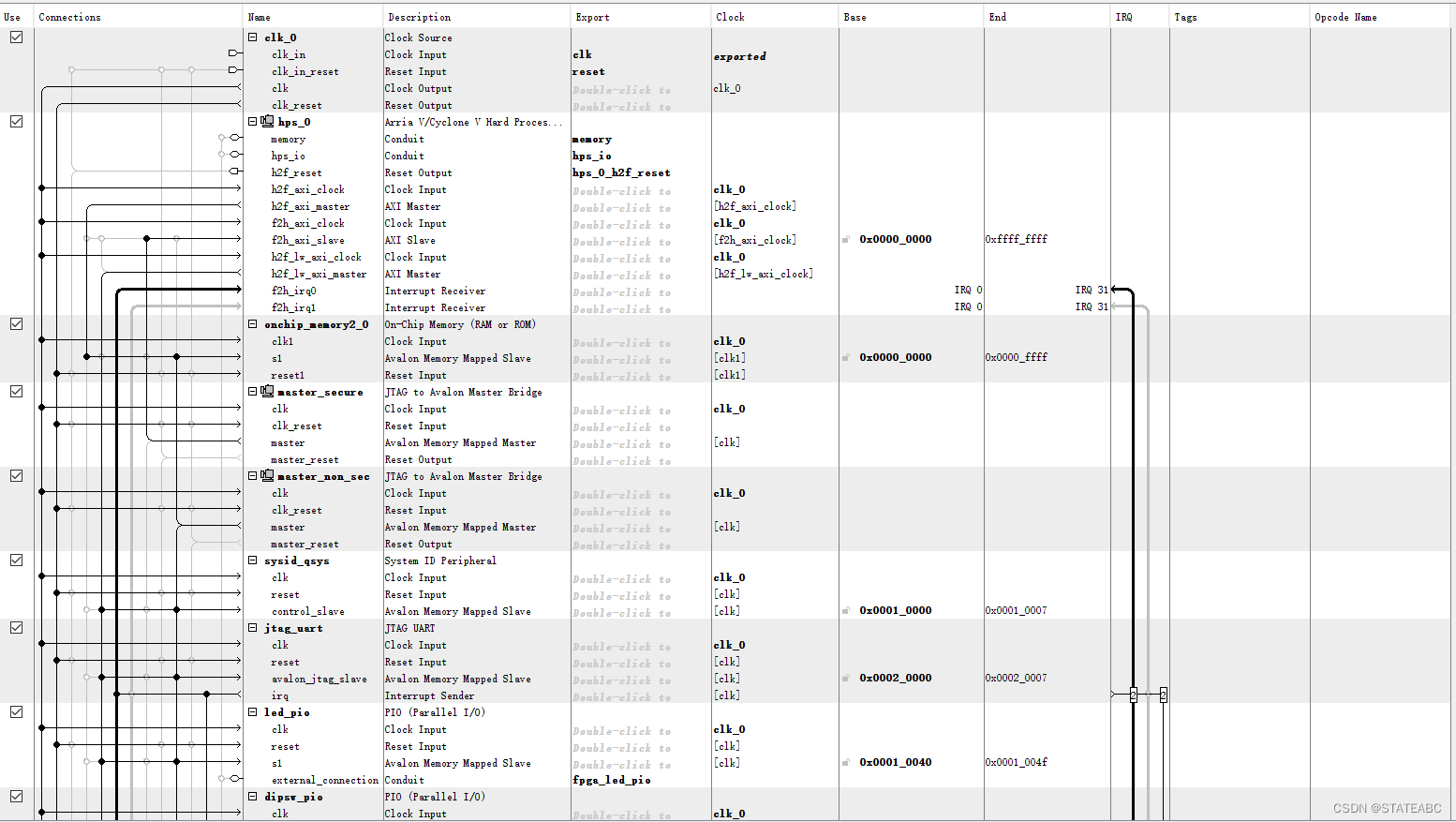

添加On-chip Memory、两个JTAG to Avalon Master Bridge、System ID Peripheral、JTAG UART、LED PIO、拨码开关PIO、按键PIO、自定义中断捕获模块

自定义中断捕获模块

module intr_capturer #(

parameter NUM_INTR = 32

// active high level interrupt is expected for the input of this capturer module

)(

input clk,

input rst_n,

input [NUM_INTR-1:0] interrupt_in,

//input [31:0] wrdata,

input addr,

input read,

output [31:0] rddata

);

reg [NUM_INTR-1:0] interrupt_reg;

reg [31:0] readdata_with_waitstate;

wire [31:0] act_readdata;

wire [31:0] readdata_lower_intr;

wire [31:0] readdata_higher_intr;

wire access_lower_32;

wire access_higher_32;

always @(posedge clk or negedge rst_n) begin

if (!rst_n) interrupt_reg <= 'b0;

else interrupt_reg <= interrupt_in;

end

generate

if (NUM_INTR>32) begin : two_intr_reg_needed

assign access_higher_32 = read & (addr == 1);

assign readdata_lower_intr = interrupt_reg[31:0] & {(32){access_lower_32}};

assign readdata_higher_intr = interrupt_reg[NUM_INTR-1:32] & {(NUM_INTR-32){access_higher_32}};

end

else begin : only_1_reg

assign readdata_lower_intr = interrupt_reg & {(NUM_INTR){access_lower_32}};

assign readdata_higher_intr = {32{1'b0}};

end

endgenerate

assign access_lower_32 = read & (addr == 0);

assign act_readdata = readdata_lower_intr | readdata_higher_intr;

assign rddata = readdata_with_waitstate;

always @(posedge clk or negedge rst_n) begin

if (!rst_n) readdata_with_waitstate <= 32'b0;

else readdata_with_waitstate <= act_readdata;

end

endmodule

1.4 产生Qsys系统

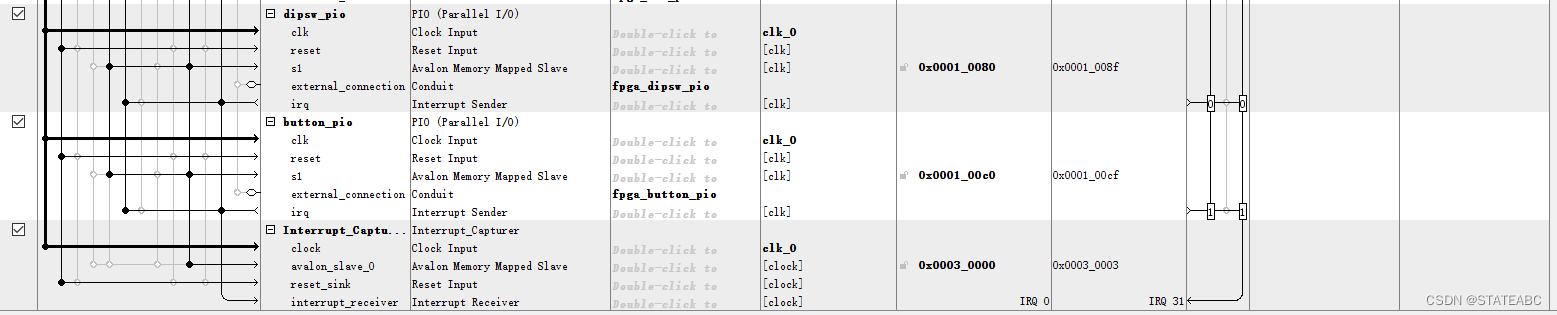

连线、设置中断、手动分配相应外设的基地址

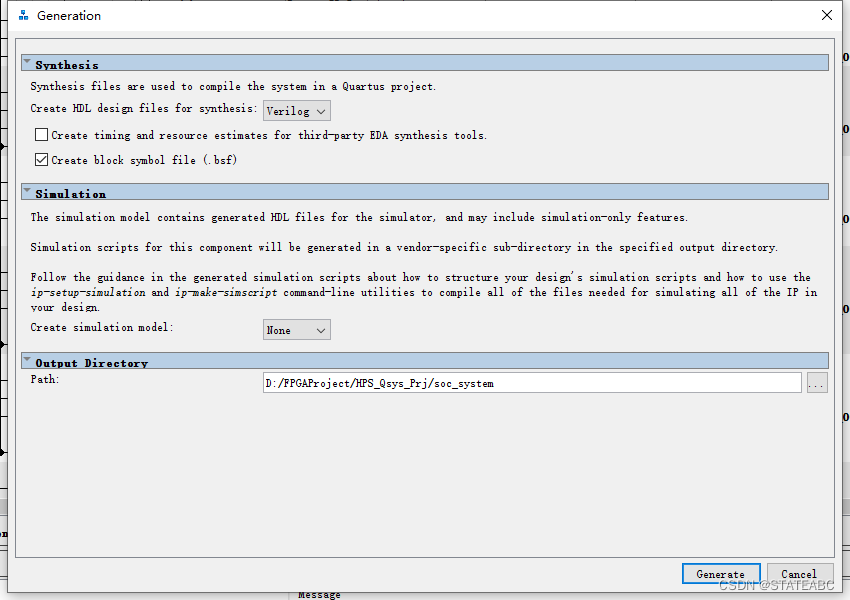

产生Qsys系统

Qsys将产生指定格式的硬件描述语言(HDL)文件用于Quartus工程编译,同时产生一组与硬件系统定义相关的文件,包括定义了选定的HPS外设默认引脚分配的Tcl(Tool Command Language)文件,定义了HPS与FPGA中多端口存储器控制器的Tcl文件,定义了系统所用IP和用于TimeQuest时序约束的QIP文件,可以在synthesis目录找到。

1.5 编译Quartus工程

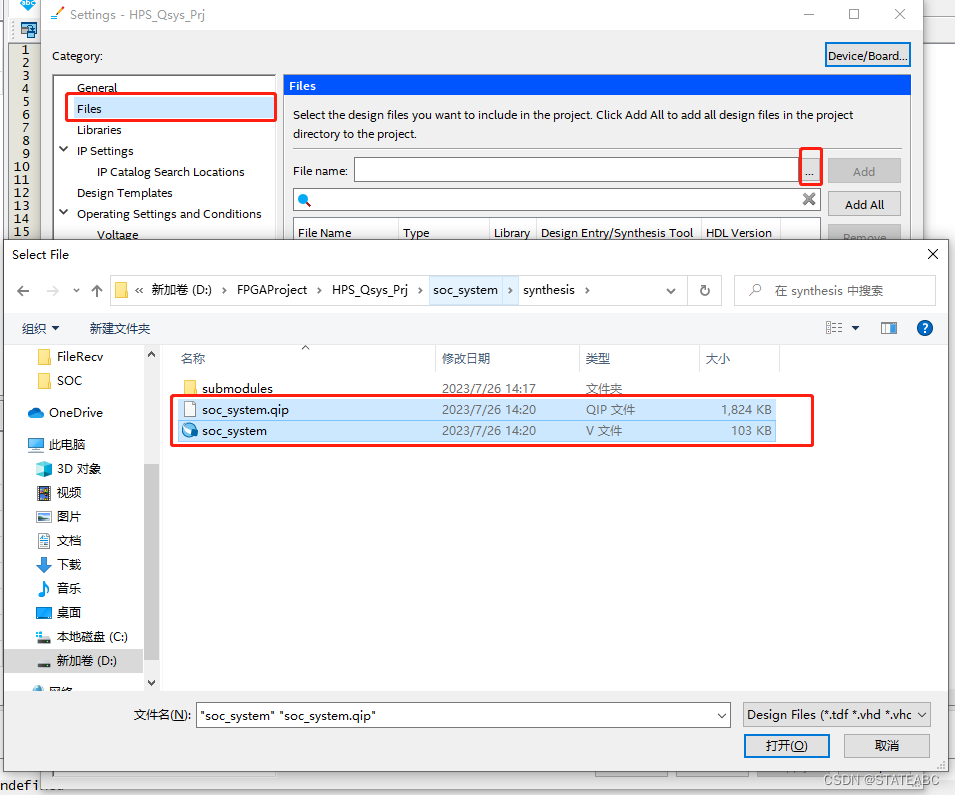

在Quartus的工程中添加soc_system.qip和soc_system.v文件

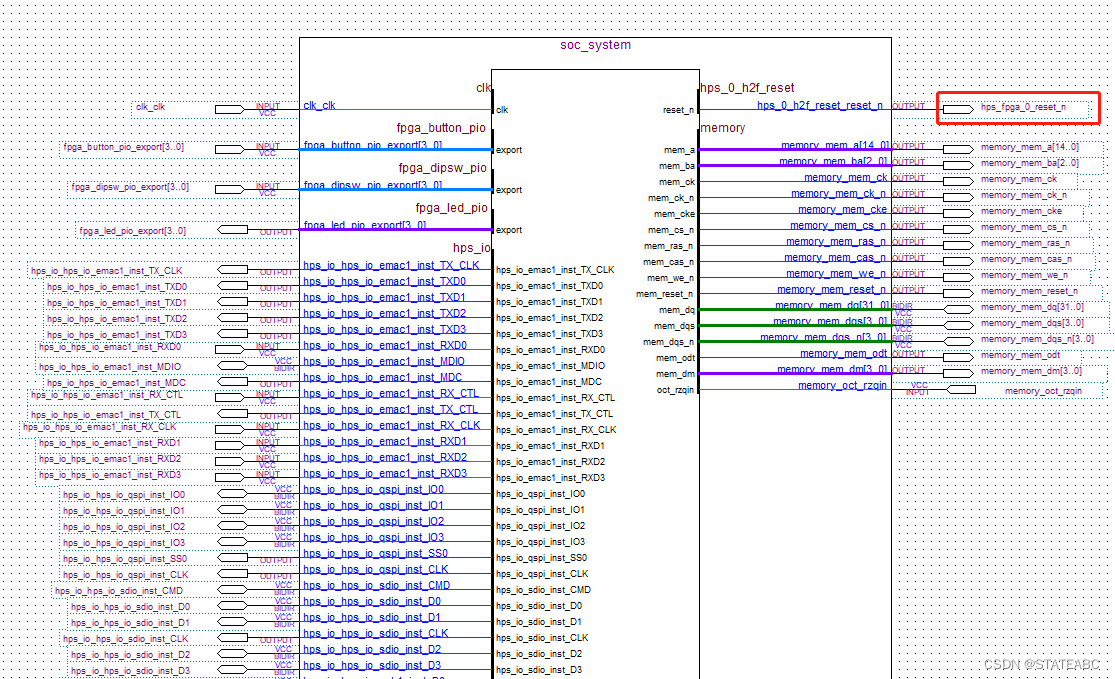

点击工具栏中的File->New->Block Diagram/Schematic File,新建一个原理图文件

再右键点击原理图空白处选择Insert->Symbol,将soc_system添加入原理图文件中,右键点击soc_system->Generate Pins for Symbol Ports,为元件添加输入/输出端口

将两处hps_0_h2f_reset的输出(命名为hps_fpga_reset_n)连接到系统的复位reset信号上,然后保存

添加顶层文件

module HPS_Qsys_prj(

///

HPS Interface

// input wire reset_reset_n, // reset.reset_n

// input wire clk_clk, // clk.clk

output wire [14:0] memory_mem_a, // memory.mem_a

output wire [2:0] memory_mem_ba, // .mem_ba

output wire memory_mem_ck, // .mem_ck

output wire memory_mem_ck_n, // .mem_ck_n

output wire memory_mem_cke, // .mem_cke

output wire memory_mem_cs_n, // .mem_cs_n

output wire memory_mem_ras_n, // .mem_ras_n

output wire memory_mem_cas_n, // .mem_cas_n

output wire memory_mem_we_n, // .mem_we_n

output wire memory_mem_reset_n, // .mem_reset_n

inout wire [31:0] memory_mem_dq, // .mem_dq

inout wire [3:0] memory_mem_dqs, // .mem_dqs

inout wire [3:0] memory_mem_dqs_n, // .mem_dqs_n

output wire memory_mem_odt, // .mem_odt

output wire [3:0] memory_mem_dm, // .mem_dm

input wire memory_oct_rzqin, // .oct_rzqin

output wire hps_0_hps_io_hps_io_emac1_inst_TX_CLK, // hps_0_hps_io.hps_io_emac1_inst_TX_CLK

output wire hps_0_hps_io_hps_io_emac1_inst_TXD0, // .hps_io_emac1_inst_TXD0

output wire hps_0_hps_io_hps_io_emac1_inst_TXD1, // .hps_io_emac1_inst_TXD1

output wire hps_0_hps_io_hps_io_emac1_inst_TXD2, // .hps_io_emac1_inst_TXD2

output wire hps_0_hps_io_hps_io_emac1_inst_TXD3, // .hps_io_emac1_inst_TXD3

input wire hps_0_hps_io_hps_io_emac1_inst_RXD0, // .hps_io_emac1_inst_RXD0

inout wire hps_0_hps_io_hps_io_emac1_inst_MDIO, // .hps_io_emac1_inst_MDIO

output wire hps_0_hps_io_hps_io_emac1_inst_MDC, // .hps_io_emac1_inst_MDC

input wire hps_0_hps_io_hps_io_emac1_inst_RX_CTL, // .hps_io_emac1_inst_RX_CTL

output wire hps_0_hps_io_hps_io_emac1_inst_TX_CTL, // .hps_io_emac1_inst_TX_CTL

input wire hps_0_hps_io_hps_io_emac1_inst_RX_CLK, // .hps_io_emac1_inst_RX_CLK

input wire hps_0_hps_io_hps_io_emac1_inst_RXD1, // .hps_io_emac1_inst_RXD1

input wire hps_0_hps_io_hps_io_emac1_inst_RXD2, // .hps_io_emac1_inst_RXD2

input wire hps_0_hps_io_hps_io_emac1_inst_RXD3, // .hps_io_emac1_inst_RXD3

inout wire hps_0_hps_io_hps_io_qspi_inst_IO0, // .hps_io_qspi_inst_IO0

inout wire hps_0_hps_io_hps_io_qspi_inst_IO1, // .hps_io_qspi_inst_IO1

inout wire hps_0_hps_io_hps_io_qspi_inst_IO2, // .hps_io_qspi_inst_IO2

inout wire hps_0_hps_io_hps_io_qspi_inst_IO3, // .hps_io_qspi_inst_IO3

output wire hps_0_hps_io_hps_io_qspi_inst_SS0, // .hps_io_qspi_inst_SS0

output wire hps_0_hps_io_hps_io_qspi_inst_CLK, // .hps_io_qspi_inst_CLK

inout wire hps_0_hps_io_hps_io_sdio_inst_CMD, // .hps_io_sdio_inst_CMD

inout wire hps_0_hps_io_hps_io_sdio_inst_D0, // .hps_io_sdio_inst_D0

inout wire hps_0_hps_io_hps_io_sdio_inst_D1, // .hps_io_sdio_inst_D1

output wire hps_0_hps_io_hps_io_sdio_inst_CLK, // .hps_io_sdio_inst_CLK

inout wire hps_0_hps_io_hps_io_sdio_inst_D2, // .hps_io_sdio_inst_D2

inout wire hps_0_hps_io_hps_io_sdio_inst_D3, // .hps_io_sdio_inst_D3

inout wire hps_0_hps_io_hps_io_usb1_inst_D0, // .hps_io_usb1_inst_D0

inout wire hps_0_hps_io_hps_io_usb1_inst_D1, // .hps_io_usb1_inst_D1

inout wire hps_0_hps_io_hps_io_usb1_inst_D2, // .hps_io_usb1_inst_D2

inout wire hps_0_hps_io_hps_io_usb1_inst_D3, // .hps_io_usb1_inst_D3

inout wire hps_0_hps_io_hps_io_usb1_inst_D4, // .hps_io_usb1_inst_D4

inout wire hps_0_hps_io_hps_io_usb1_inst_D5, // .hps_io_usb1_inst_D5

inout wire hps_0_hps_io_hps_io_usb1_inst_D6, // .hps_io_usb1_inst_D6

inout wire hps_0_hps_io_hps_io_usb1_inst_D7, // .hps_io_usb1_inst_D7

input wire hps_0_hps_io_hps_io_usb1_inst_CLK, // .hps_io_usb1_inst_CLK

output wire hps_0_hps_io_hps_io_usb1_inst_STP, // .hps_io_usb1_inst_STP

input wire hps_0_hps_io_hps_io_usb1_inst_DIR, // .hps_io_usb1_inst_DIR

input wire hps_0_hps_io_hps_io_usb1_inst_NXT, // .hps_io_usb1_inst_NXT

output wire hps_0_hps_io_hps_io_spim0_inst_CLK, // .hps_io_spim0_inst_CLK

output wire hps_0_hps_io_hps_io_spim0_inst_MOSI, // .hps_io_spim0_inst_MOSI

input wire hps_0_hps_io_hps_io_spim0_inst_MISO, // .hps_io_spim0_inst_MISO

output wire hps_0_hps_io_hps_io_spim0_inst_SS0, // .hps_io_spim0_inst_SS0

output wire hps_0_hps_io_hps_io_spim1_inst_CLK, // .hps_io_spim1_inst_CLK

output wire hps_0_hps_io_hps_io_spim1_inst_MOSI, // .hps_io_spim1_inst_MOSI

input wire hps_0_hps_io_hps_io_spim1_inst_MISO, // .hps_io_spim1_inst_MISO

output wire hps_0_hps_io_hps_io_spim1_inst_SS0, // .hps_io_spim1_inst_SS0

input wire hps_0_hps_io_hps_io_uart0_inst_RX, // .hps_io_uart0_inst_RX

output wire hps_0_hps_io_hps_io_uart0_inst_TX, // .hps_io_uart0_inst_TX

inout wire hps_0_hps_io_hps_io_i2c1_inst_SDA, // .hps_io_i2c1_inst_SDA

inout wire hps_0_hps_io_hps_io_i2c1_inst_SCL, // .hps_io_i2c1_inst_SCL

inout wire hps_0_hps_io_hps_io_gpio_inst_GPIO0, // .hps_io_gpio_inst_GPIO0

inout wire hps_0_hps_io_hps_io_gpio_inst_HLGPI1,

inout wire hps_0_hps_io_hps_io_gpio_inst_HLGPI2,

inout wire hps_0_hps_io_hps_io_gpio_inst_HLGPI3,

inout wire hps_0_hps_io_hps_io_gpio_inst_HLGPI4,

inout wire hps_0_hps_io_hps_io_gpio_inst_HLGPI5,

inout wire hps_0_hps_io_hps_io_gpio_inst_HLGPI6,

inout wire hps_0_hps_io_hps_io_gpio_inst_HLGPI7,

inout wire hps_0_hps_io_hps_io_gpio_inst_HLGPI8,

inout wire hps_0_hps_io_hps_io_gpio_inst_HLGPI9,

inout wire hps_0_hps_io_hps_io_gpio_inst_HLGPI10,

inout wire hps_0_hps_io_hps_io_gpio_inst_HLGPI11,

inout wire hps_0_hps_io_hps_io_gpio_inst_HLGPI12,

inout wire hps_0_hps_io_hps_io_gpio_inst_HLGPI13,

inout wire hps_0_hps_io_hps_io_gpio_inst_GPIO09, // .hps_io_gpio_inst_GPIO09

inout wire hps_0_hps_io_hps_io_gpio_inst_GPIO35, // .hps_io_gpio_inst_GPIO35

inout wire hps_0_hps_io_hps_io_gpio_inst_GPIO48, // .hps_io_gpio_inst_GPIO48

inout wire hps_0_hps_io_hps_io_gpio_inst_GPIO53, // .hps_io_gpio_inst_GPIO53

inout wire hps_0_hps_io_hps_io_gpio_inst_GPIO54, // .hps_io_gpio_inst_GPIO54

inout wire hps_0_hps_io_hps_io_gpio_inst_GPIO55, // .hps_io_gpio_inst_GPIO55

inout wire hps_0_hps_io_hps_io_gpio_inst_GPIO56, // .hps_io_gpio_inst_GPIO56

inout wire hps_0_hps_io_hps_io_gpio_inst_GPIO61, // .hps_io_gpio_inst_GPIO61

inout wire hps_0_hps_io_hps_io_gpio_inst_GPIO62, // .hps_io_gpio_inst_GPIO62

FPGA Interface

//FPGA-GPLL-CLK------------------------//X pins

input clk_100m_fpga, //2.5V //100 MHz (2nd copy to max)

input clk_50m_fpga, //2.5V //50MHz (2nd copy to max)

input clk_top1, //2.5V //156.25 MHz adjustable

input clk_bot1, //1.5V //100 MHz ajustable

input fpga_resetn, //2.5V //FPGA Reset Pushbutton

SiLabs Clock Generator I/F ///

output wire clk_i2c_sclk, // I2C Clock

inout wire clk_i2c_sdat, // I2C Data

`ifdef user_peripheral

//FPGA-User-IO-------------------------//14 pins //--------------------------

input [3:0] user_dipsw_fpga, //

output [3:0] user_led_fpga, //

input [3:0] user_pb_fpga, //

input wire irda_rxd, // IRDA Receive LED

output wire fan_ctrl // control for fan

`endif

`ifdef ddr3

//FPGA-DDR3-400Mx32--------------------//74 pins //--------------------------

output [14:0] ddr3_fpga_a, //SSTL15 //Address

output [2:0] ddr3_fpga_ba, //SSTL15 //Bank Address

output ddr3_fpga_casn, //SSTL15 //Column Address Strobe

output ddr3_fpga_cke, //SSTL15 //Clock Enable

output ddr3_fpga_clk_n, //SSTL15 //Diff Clock - Neg

output ddr3_fpga_clk_p, //SSTL15 //Diff Clock - Pos

output ddr3_fpga_csn, //SSTL15 //Chip Select

output [3:0] ddr3_fpga_dm, //SSTL15 //Data Write Mask

inout [31:0] ddr3_fpga_dq, //SSTL15 //Data Bus

inout [3:0] ddr3_fpga_dqs_n, //SSTL15 //Diff Data Strobe - Neg

inout [3:0] ddr3_fpga_dqs_p, //SSTL15 //Diff Data Strobe - Pos

output ddr3_fpga_odt, //SSTL15 //On-Die Termination Enable

output ddr3_fpga_rasn, //SSTL15 //Row Address Strobe

output ddr3_fpga_resetn, //SSTL15 //Reset

output ddr3_fpga_wen, //SSTL15 //Write Enable

input ddr3_fpga_rzq, //OCT_rzqin //On-die termination enable

// input oct_rdn, //SSTL15 //On-die termination enable

// input oct_rup, //SSTL15 //On-die termination enable

`endif

`ifdef temp_sense

Temp. Sensor I/F

// SPI interface //

output wire temp_cs_n, // Chip Select

output wire temp_sclk, // Slave Clock

output wire temp_mosi, // Data Out

input wire temp_miso, // Data In

`endif

`ifdef vga

VIDEO

output wire vga_clk, // Video Clock

output wire vga_hs, // Horizontal Synch

output wire vga_vs, // Vertical Synch

output wire [7:0] vga_r, // Red

output wire [7:0] vga_g, // Green

output wire [7:0] vga_b, // Blue

output wire vga_blank_n, // Composite Blank Control

output wire vga_sync_n, // Composite Synch Control

`endif

`ifdef audio

AUDIO

input wire aud_adcdat, // ADC Serial Data or I2C_SCLK

input wire aud_adclrck, // FDDR3e clock

input wire aud_bclk, // Bit Clock

output wire aud_dacdat, // DAC Serial Data

inout wire aud_daclrck, // FDDR3e Clock

output wire aud_i2c_sclk,

inout wire aud_i2c_sdat,

output wire aud_mute,

output wire aud_xck,

`endif

`ifdef hsma

//HSMC-Port-A----------------------------------------------------

// input [2:1] hsmc_clkin_n,

input [2:1] hsmc_clkin_p,

// output [2:1] hsmc_clkout_n,

output [2:1] hsmc_clkout_p,

input hsmc_clk_in0,

output hsmc_clk_out0,

inout [3:0] hsmc_d,

`ifdef HSMC_XCVR

// input [7:0] hsmc_gxb_rx_n,

input [7:0] hsmc_gxb_rx_p,

// output [7:0] hsmc_gxb_tx_n,

output [7:0] hsmc_gxb_tx_p,

// input hsmc_ref_clk_n,

input hsmc_ref_clk_p,

`endif

// input [16:0] hsmc_rx_n,

input [16:0] hsmc_rx_p,

output hsmc_scl,

inout hsmc_sda,

// output [16:0] hsmc_tx_n,

output [16:0] hsmc_tx_p

`endif

QSPI Flash I/F ///

inout wire [3:0] fpga_epqc_data, // Flash Data

output wire fpga_epqc_dclk, // Data Clock

output wire fpga_epqc_ncso // Chip Select

);

// internal wires and registers declaration

wire [3:0] fpga_led_internal;

wire hps_fpga_reset_n;

// connection of internal logics

// assign user_led_fpga = ~fpga_led_internal;

assign user_led_fpga = fpga_led_internal;

soc_system u0 (

.clk_clk (clk_bot1), // clk.clk

.fpga_button_pio_export (user_pb_fpga), // fpga_button_pio.export

.fpga_dipsw_pio_export (user_dipsw_fpga), // fpga_dipsw_pio.export

.fpga_led_pio_export (fpga_led_internal), // fpga_led_pio.export

.hps_0_h2f_reset_reset_n (hps_fpga_reset_n), // hps_0_h2f_reset.reset_n

.hps_io_hps_io_emac1_inst_TX_CLK (hps_0_hps_io_hps_io_emac1_inst_TX_CLK), // hps_io.hps_io_emac1_inst_TX_CLK

.hps_io_hps_io_emac1_inst_TXD0 (hps_0_hps_io_hps_io_emac1_inst_TXD0), // .hps_io_emac1_inst_TXD0

.hps_io_hps_io_emac1_inst_TXD1 (hps_0_hps_io_hps_io_emac1_inst_TXD1), // .hps_io_emac1_inst_TXD1

.hps_io_hps_io_emac1_inst_TXD2 (hps_0_hps_io_hps_io_emac1_inst_TXD2), // .hps_io_emac1_inst_TXD2

.hps_io_hps_io_emac1_inst_TXD3 (hps_0_hps_io_hps_io_emac1_inst_TXD3), // .hps_io_emac1_inst_TXD3

.hps_io_hps_io_emac1_inst_RXD0 (hps_0_hps_io_hps_io_emac1_inst_RXD0), // .hps_io_emac1_inst_RXD0

.hps_io_hps_io_emac1_inst_MDIO (hps_0_hps_io_hps_io_emac1_inst_MDIO), // .hps_io_emac1_inst_MDIO

.hps_io_hps_io_emac1_inst_MDC (hps_0_hps_io_hps_io_emac1_inst_MDC), // .hps_io_emac1_inst_MDC

.hps_io_hps_io_emac1_inst_RX_CTL (hps_0_hps_io_hps_io_emac1_inst_RX_CTL), // .hps_io_emac1_inst_RX_CTL

.hps_io_hps_io_emac1_inst_TX_CTL (hps_0_hps_io_hps_io_emac1_inst_TX_CTL), // .hps_io_emac1_inst_TX_CTL

.hps_io_hps_io_emac1_inst_RX_CLK (hps_0_hps_io_hps_io_emac1_inst_RX_CLK), // .hps_io_emac1_inst_RX_CLK

.hps_io_hps_io_emac1_inst_RXD1 (hps_0_hps_io_hps_io_emac1_inst_RXD1), // .hps_io_emac1_inst_RXD1

.hps_io_hps_io_emac1_inst_RXD2 (hps_0_hps_io_hps_io_emac1_inst_RXD2), // .hps_io_emac1_inst_RXD2

.hps_io_hps_io_emac1_inst_RXD3 (hps_0_hps_io_hps_io_emac1_inst_RXD3), // .hps_io_emac1_inst_RXD3

.hps_io_hps_io_qspi_inst_IO0 (hps_0_hps_io_hps_io_qspi_inst_IO0), // .hps_io_qspi_inst_IO0

.hps_io_hps_io_qspi_inst_IO1 (hps_0_hps_io_hps_io_qspi_inst_IO1), // .hps_io_qspi_inst_IO1

.hps_io_hps_io_qspi_inst_IO2 (hps_0_hps_io_hps_io_qspi_inst_IO2), // .hps_io_qspi_inst_IO2

.hps_io_hps_io_qspi_inst_IO3 (hps_0_hps_io_hps_io_qspi_inst_IO3), // .hps_io_qspi_inst_IO3

.hps_io_hps_io_qspi_inst_SS0 (hps_0_hps_io_hps_io_qspi_inst_SS0), // .hps_io_qspi_inst_SS0

.hps_io_hps_io_qspi_inst_CLK (hps_0_hps_io_hps_io_qspi_inst_CLK), // .hps_io_qspi_inst_CLK

.hps_io_hps_io_sdio_inst_CMD (hps_0_hps_io_hps_io_sdio_inst_CMD), // .hps_io_sdio_inst_CMD

.hps_io_hps_io_sdio_inst_D0 (hps_0_hps_io_hps_io_sdio_inst_D0), // .hps_io_sdio_inst_D0

.hps_io_hps_io_sdio_inst_D1 (hps_0_hps_io_hps_io_sdio_inst_D1), // .hps_io_sdio_inst_D1

.hps_io_hps_io_sdio_inst_CLK (hps_0_hps_io_hps_io_sdio_inst_CLK), // .hps_io_sdio_inst_CLK

.hps_io_hps_io_sdio_inst_D2 (hps_0_hps_io_hps_io_sdio_inst_D2), // .hps_io_sdio_inst_D2

.hps_io_hps_io_sdio_inst_D3 (hps_0_hps_io_hps_io_sdio_inst_D3), // .hps_io_sdio_inst_D3

.hps_io_hps_io_usb1_inst_D0 (hps_0_hps_io_hps_io_usb1_inst_D0), // .hps_io_usb1_inst_D0

.hps_io_hps_io_usb1_inst_D1 (hps_0_hps_io_hps_io_usb1_inst_D1), // .hps_io_usb1_inst_D1

.hps_io_hps_io_usb1_inst_D2 (hps_0_hps_io_hps_io_usb1_inst_D2), // .hps_io_usb1_inst_D2

.hps_io_hps_io_usb1_inst_D3 (hps_0_hps_io_hps_io_usb1_inst_D3), // .hps_io_usb1_inst_D3

.hps_io_hps_io_usb1_inst_D4 (hps_0_hps_io_hps_io_usb1_inst_D4), // .hps_io_usb1_inst_D4

.hps_io_hps_io_usb1_inst_D5 (hps_0_hps_io_hps_io_usb1_inst_D5), // .hps_io_usb1_inst_D5

.hps_io_hps_io_usb1_inst_D6 (hps_0_hps_io_hps_io_usb1_inst_D6), // .hps_io_usb1_inst_D6

.hps_io_hps_io_usb1_inst_D7 (hps_0_hps_io_hps_io_usb1_inst_D7), // .hps_io_usb1_inst_D7

.hps_io_hps_io_usb1_inst_STP (hps_0_hps_io_hps_io_usb1_inst_STP), // .hps_io_usb1_inst_STP

.hps_io_hps_io_usb1_inst_DIR (hps_0_hps_io_hps_io_usb1_inst_DIR), // .hps_io_usb1_inst_DIR

.hps_io_hps_io_usb1_inst_NXT (hps_0_hps_io_hps_io_usb1_inst_NXT), // .hps_io_usb1_inst_NXT

.hps_io_hps_io_spim0_inst_CLK (hps_0_hps_io_hps_io_spim0_inst_CLK), // .hps_io_spim0_inst_CLK

.hps_io_hps_io_spim0_inst_MOSI (hps_0_hps_io_hps_io_spim0_inst_MOSI), // .hps_io_spim0_inst_MOSI

.hps_io_hps_io_spim0_inst_MISO (hps_0_hps_io_hps_io_spim0_inst_MISO), // .hps_io_spim0_inst_MISO

.hps_io_hps_io_spim0_inst_SS0 (hps_0_hps_io_hps_io_spim0_inst_SS0), // .hps_io_spim0_inst_SS0

.hps_io_hps_io_spim1_inst_CLK (hps_0_hps_io_hps_io_spim1_inst_CLK), // .hps_io_spim1_inst_CLK

.hps_io_hps_io_spim1_inst_MOSI (hps_0_hps_io_hps_io_spim1_inst_MOSI), // .hps_io_spim1_inst_MOSI

.hps_io_hps_io_spim1_inst_MISO (hps_0_hps_io_hps_io_spim1_inst_MISO), // .hps_io_spim1_inst_MISO

.hps_io_hps_io_spim1_inst_SS0 (hps_0_hps_io_hps_io_spim1_inst_SS0), // .hps_io_spim1_inst_SS0

.hps_io_hps_io_uart0_inst_RX (hps_0_hps_io_hps_io_uart0_inst_RX), // .hps_io_uart0_inst_RX

.hps_io_hps_io_uart0_inst_TX (hps_0_hps_io_hps_io_uart0_inst_TX), // .hps_io_uart0_inst_TX

.hps_io_hps_io_i2c1_inst_SDA (hps_0_hps_io_hps_io_i2c1_inst_SDA), // .hps_io_i2c1_inst_SDA

.hps_io_hps_io_i2c1_inst_SCL (hps_0_hps_io_hps_io_i2c1_inst_SCL), // .hps_io_i2c1_inst_SCL

.hps_io_hps_io_gpio_inst_HLGPI0 (hps_0_hps_io_hps_io_gpio_inst_GPIO0), // .hps_io_gpio_inst_HLGPI0

.hps_io_hps_io_gpio_inst_HLGPI1 (hps_0_hps_io_hps_io_gpio_inst_HLGPI1), // .hps_io_gpio_inst_HLGPI1

.hps_io_hps_io_gpio_inst_HLGPI2 (hps_0_hps_io_hps_io_gpio_inst_HLGPI2), // .hps_io_gpio_inst_HLGPI2

.hps_io_hps_io_gpio_inst_HLGPI3 (hps_0_hps_io_hps_io_gpio_inst_HLGPI3), // .hps_io_gpio_inst_HLGPI3

.hps_io_hps_io_gpio_inst_HLGPI4 (hps_0_hps_io_hps_io_gpio_inst_HLGPI4), // .hps_io_gpio_inst_HLGPI4

.hps_io_hps_io_gpio_inst_HLGPI5 (hps_0_hps_io_hps_io_gpio_inst_HLGPI5), // .hps_io_gpio_inst_HLGPI5

.hps_io_hps_io_gpio_inst_HLGPI6 (hps_0_hps_io_hps_io_gpio_inst_HLGPI6), // .hps_io_gpio_inst_HLGPI6

.hps_io_hps_io_gpio_inst_HLGPI7 (hps_0_hps_io_hps_io_gpio_inst_HLGPI7), // .hps_io_gpio_inst_HLGPI7

.hps_io_hps_io_gpio_inst_HLGPI8 (hps_0_hps_io_hps_io_gpio_inst_HLGPI8), // .hps_io_gpio_inst_HLGPI8

.hps_io_hps_io_gpio_inst_HLGPI9 (hps_0_hps_io_hps_io_gpio_inst_HLGPI9), // .hps_io_gpio_inst_HLGPI9

.hps_io_hps_io_gpio_inst_HLGPI10 (hps_0_hps_io_hps_io_gpio_inst_HLGPI10), // .hps_io_gpio_inst_HLGPI10

.hps_io_hps_io_gpio_inst_HLGPI11 (hps_0_hps_io_hps_io_gpio_inst_HLGPI11), // .hps_io_gpio_inst_HLGPI11

.hps_io_hps_io_gpio_inst_HLGPI12 (hps_0_hps_io_hps_io_gpio_inst_HLGPI12), // .hps_io_gpio_inst_HLGPI12

.hps_io_hps_io_gpio_inst_HLGPI13 (hps_0_hps_io_hps_io_gpio_inst_HLGPI13), // .hps_io_gpio_inst_HLGPI13

.hps_io_hps_io_gpio_inst_GPIO09 (hps_0_hps_io_hps_io_gpio_inst_GPIO09), // .hps_io_gpio_inst_GPIO09

.memory_mem_a (memory_mem_a), // memory.mem_a

.memory_mem_ba (memory_mem_ba), // .mem_ba

.memory_mem_ck (memory_mem_ck), // .mem_ck

.memory_mem_ck_n (memory_mem_ck_n), // .mem_ck_n

.memory_mem_cke (memory_mem_cke), // .mem_cke

.memory_mem_cs_n (memory_mem_cs_n), // .mem_cs_n

.memory_mem_ras_n (memory_mem_ras_n), // .mem_ras_n

.memory_mem_cas_n (memory_mem_cas_n), // .mem_cas_n

.memory_mem_we_n (memory_mem_we_n), // .mem_we_n

.memory_mem_reset_n (memory_mem_reset_n), // .mem_reset_n

.memory_mem_dq (memory_mem_dq), // .mem_dq

.memory_mem_dqs (memory_mem_dqs), // .mem_dqs

.memory_mem_dqs_n (memory_mem_dqs_n), // .mem_dqs_n

.memory_mem_odt (memory_mem_odt), // .mem_odt

.memory_mem_dm (memory_mem_dm), // .mem_dm

.memory_oct_rzqin (memory_oct_rzqin), // .oct_rzqin

.reset_reset_n (hps_fpga_reset_n) // reset.reset_n

);

endmodule

对工程文件进行分析综合

由于系统中的HPS是在Qsys集成工具中例化得到,因此除了所使用的外部存储器引脚以外,其他的专用引脚不需要再Quartus中进行分配,而是在HSP例化过程中由Qsys自动完成HPS的引脚分配,并把相关信息保存在XML格式的文件中提供给软件开发工具使用。但是HPS的外部存储器引脚需要在Quartus中进行引脚分配,该引脚分配信息同样保存在Tcl脚本文件中,只需要执行该脚本文件即可。

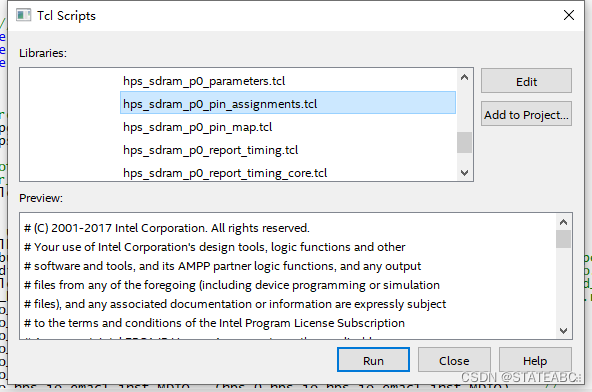

Tool->Tcl Scripts->hps_sdram_p0_pin_assignments.tcl->run

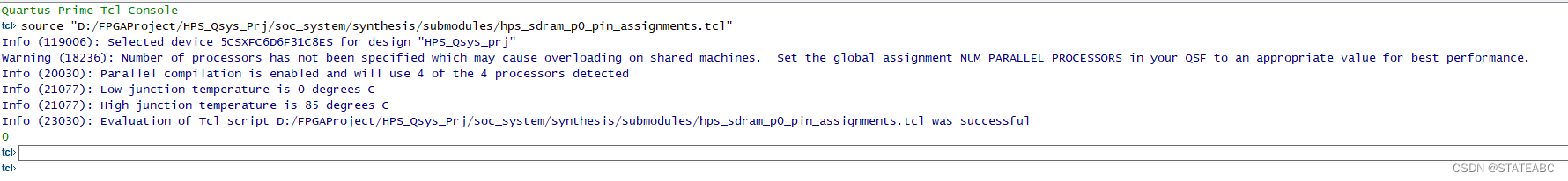

执行完后可以在Tcl Console总查看执行结果

最后进行外设引脚分配、工程编译产生.sof文件、下载到FPGA开发板上,整个硬件平台建立完毕

1.6 硬件系统外设的输入/输出测试

系统控制台(Syetem Console)是一种硬件调试工具,通过Tcl脚本命令可以对Qsys中定制的FPGA部分的外设进行测试。在Syetem Console中通过执行Tcl命令可以读取输入PIO寄存器的状态,也可以向输出PIO寄存器写入需要输出的结果

1.7 相关代码

基于Qsys的HPS模型设计资源-CSDN文库

参考文献:

基于FPGA的嵌入式系统设计—Altera Soc FPGA

Cyclone V SoC FPGA和 Arria V SoC FPGA设计指南概述 (intel.cn)

Cyclone V SoC GSRD | Documentation | RocketBoards.org

![[JavaScript游戏开发] 绘制冰宫宝藏地图、人物鼠标点击移动、障碍检测](https://img-blog.csdnimg.cn/f6af768ffacd4764b475e8140d6bb74b.png)