RISCV -3 RV32I/RV64I基本整型指令集

- 1 RV32I Base Integer Instruction Set

- 1.1 Programmers’ Model for Base Integer ISA

- 1.2 Base Instruction Formats

- 1.3 Immediate Encoding Variants

- 1.4 Integer Computational Instructions

- 1.4.1 Integer Register-Immediate Instructions

- 1.4.2 Integer Register-Register Operations

- 1.4.3 NOP Instruction

- 1.5 Control Transfer Instructions

- 1.5.1 Unconditional Jumps

- 1.5.2 Conditional Branches

- 1.6 Load and Store Instructions

- 1.7 Memory Ordering Instructions

- 1.8 Environment Call and Breakpoints

- 1.9 HINT Instructions

- 2 RV64I Base Integer Instruction Set

- 2.1 Register State

- 2.2 Integer Computational Instructions

- 2.2.1 Integer Register-Immediate Instructions

- 2.2.2 Integer Register-Register Operations

- 2.3 Load and Store Instructions

- 2.4 HINT Instructions

- 参考文档

RISCV - 1 RV32/64G指令集清单

RISCV - 2 “Zicsr“, CSR Instructions

1 RV32I Base Integer Instruction Set

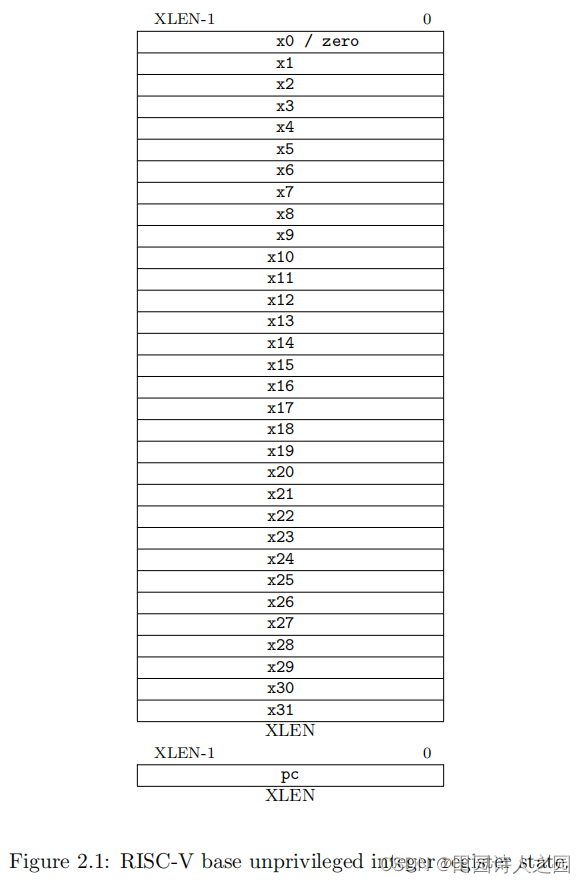

1.1 Programmers’ Model for Base Integer ISA

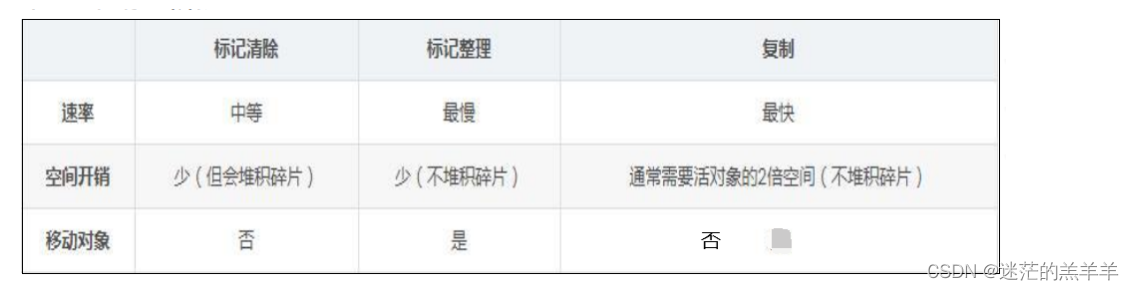

Figure 2.1 shows the unprivileged state for the base integer ISA. For RV32I, the 32 x registers are each 32 bits wide, i.e., XLEN=32. Register x0 is hardwired with all bits equal to 0. General purpose registers x1–x31 hold values that various instructions interpret as a collection of Boolean values, or as two’s complement signed binary integers or unsigned binary integers.

图 2.1 显示了基本整数 ISA 的非特权状态。对于 RV32I,32 个 x 寄存器每个都是 32 位宽,即 XLEN=32。通用寄存器 x1-x31 保存的值被各种指令解释为布尔值集合、有符号二进制整数或无符号二进制整数。

There is one additional unprivileged register: the program counter pc holds the address of the current instruction.

还有一个非特权寄存器:程序计数器 pc,用于保存当前指令的地址。

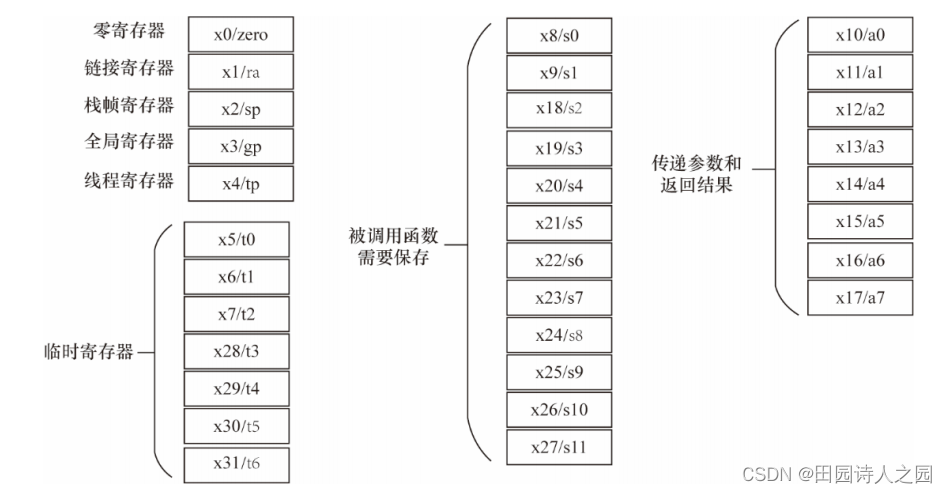

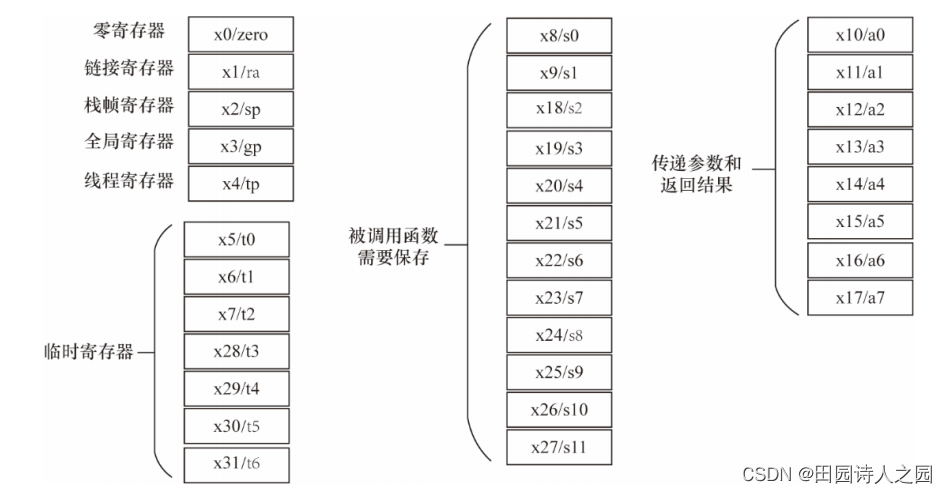

RC32I的寄存器功能分类:

There is no dedicated stack pointer or subroutine return address link register in the Base Integer ISA; the instruction encoding allows any x register to be used for these purposes. However, the standard software calling convention uses register x1 to hold the return address for a call, with register x5 available as an alternate link register. The standard calling convention uses register x2 as the stack pointer.

在基本整数 ISA 中,没有专用的堆栈指针或子程序返回地址链接寄存器;指令编码允许将任何 x 寄存器用于这些目的。不过,标准软件调用习惯使用寄存器 x1 保存调用的返回地址,寄存器 x5 可作为备用链接寄存器。标准调用习惯使用寄存器 x2 作为堆栈指针。

Hardware might choose to accelerate function calls and returns that use x1 or x5.

硬件可能会加速函数调用和返回选择使用 x1 或 x5 。

The optional compressed 16-bit instruction format is designed around the assumption that x1 is the return address register and x2 is the stack pointer. Software using other conventions will operate correctly but may have greater code size.

可选的压缩 16 位指令格式是根据 x1 是返回地址寄存器、x2 是堆栈指针的假设设计的。使用其他约定的软件也能正常运行,但代码量可能较大。

1.2 Base Instruction Formats

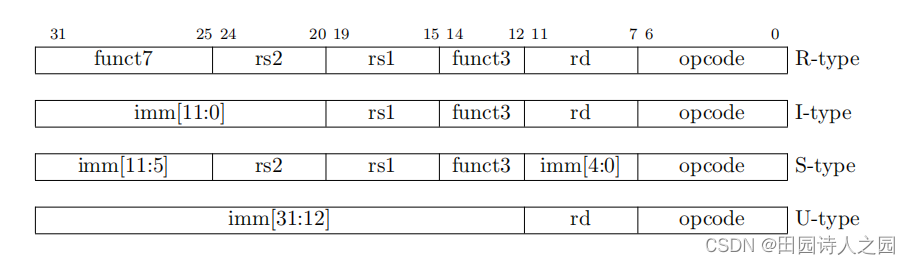

In the base RV32I ISA, there are four core instruction formats (R/I/S/U), as shown in Figure 2.2. All are a fixed 32 bits in length and must be aligned on a four-byte boundary in memory. An instruction-address-misaligned exception is generated on a taken branch or unconditional jump if the target address is not four-byte aligned. This exception is reported on the branch or jump instruction, not on the target instruction. No instruction-address-misaligned exception is generated for a conditional branch that is not taken.

在基本 RV32I ISA 中,有四种核心指令格式(R/I/S/U),如图 2.2 所示。所有指令的长度都是固定的 32 位,并且必须在内存的四字节边界上对齐。如果目标地址未按四字节对齐,则在执行分支或无条件跳转时会产生指令地址不对齐异常。报告异常的是分支或跳转指令,而不是目标指令。未执行的有条件分支不会产生指令地址对齐异常。

Figure 2.2: RISC-V base instruction formats. Each immediate subfield is labeled with the bit position (imm[x ]) in the immediate value being produced, rather than the bit position within the instruction’s immediate field as is usually done.

图 2.2: RISC-V 基本指令格式。每个立即数子字段都标有正在产生的立即数的位位置(imm[x ]),而不是通常指令立即字段中的位位置。

1.3 Immediate Encoding Variants

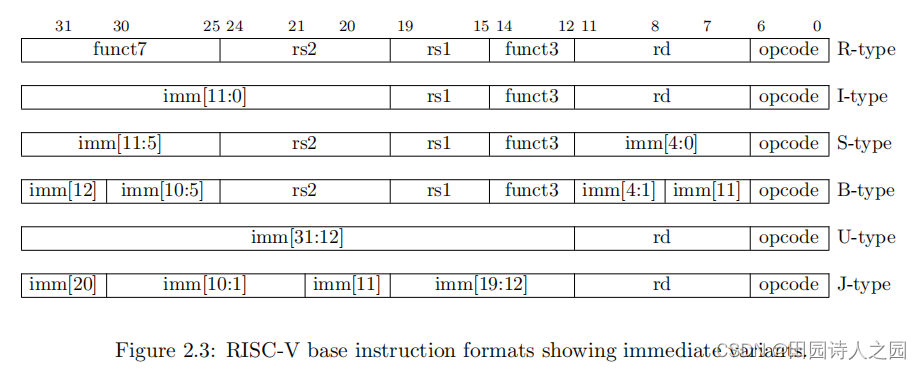

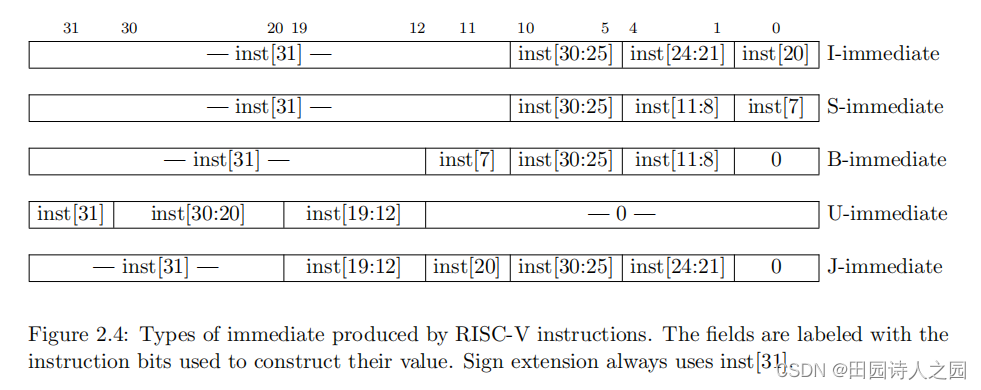

There are a further two variants of the instruction formats (B/J) based on the handling of immediates, as shown in Figure 2.3.

如图 2.3 所示,指令格式 (B/J) 还有两种基于立即数处理的变体。

Figure 2.4 shows the immediates produced by each of the base instruction formats, and is labeled to show which instruction bit (inst[y ]) produces each bit of the immediate value.

图 2.4 显示了每种基本指令格式产生的立即值,并标注了产生立即数每一位的指令位(inst[y ])。

1.4 Integer Computational Instructions

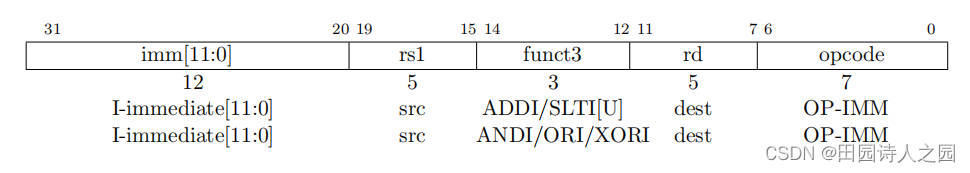

Most integer computational instructions operate on XLEN bits of values held in the integer register file. Integer computational instructions are either encoded as register-immediate operations using the I-type format or as register-register operations using the R-type format. The destination is register rd for both register-immediate and register-register instructions. No integer computational instructions cause arithmetic exceptions.

大多数整数计算指令对整数寄存器文件中的 XLEN 位值进行操作。整数运算指令要么使用 I 型格式编码为寄存器-立即数操作,要么使用 R 型格式编码为寄存器-寄存器操作。无论是立即数-寄存器指令还是寄存器-寄存器指令,其目标寄存器都是寄存器 rd。整数运算指令不会导致算术异常。

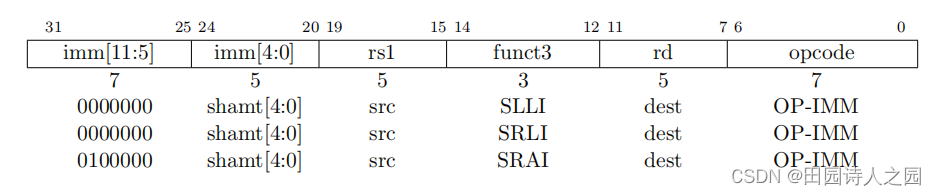

1.4.1 Integer Register-Immediate Instructions

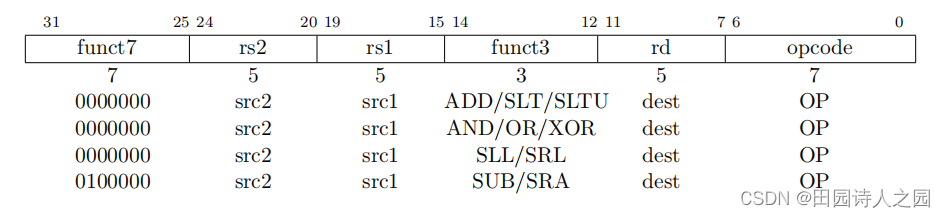

1.4.2 Integer Register-Register Operations

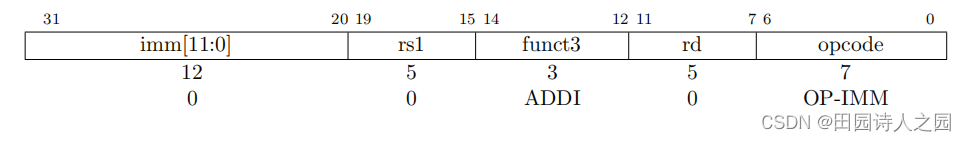

1.4.3 NOP Instruction

The NOP instruction does not change any architecturally visible state, except for advancing the pc and incrementing any applicable performance counters. NOP is encoded as ADDI x0, x0, 0.

除了推进 pc 和递增任何适用的性能计数器外,NOP 指令不会改变任何架构上可见的状态。NOP 编码为 ADDI x0, x0, 0。

1.5 Control Transfer Instructions

RV32I provides two types of control transfer instructions: unconditional jumps and conditional branches. Control transfer instructions in RV32I do not have architecturally visible delay slots.

RV32I 提供两种控制转移指令:无条件跳转和有条件分支。RV32I 中的控制转移指令没有架构上可见的延迟槽。

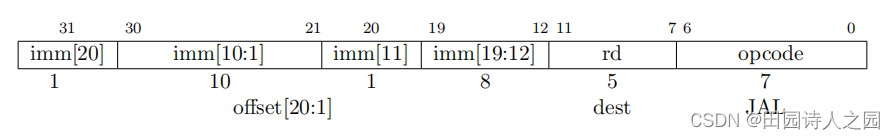

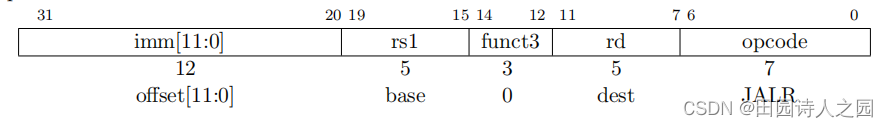

1.5.1 Unconditional Jumps

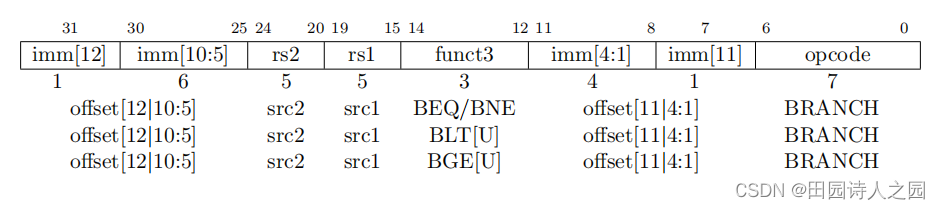

1.5.2 Conditional Branches

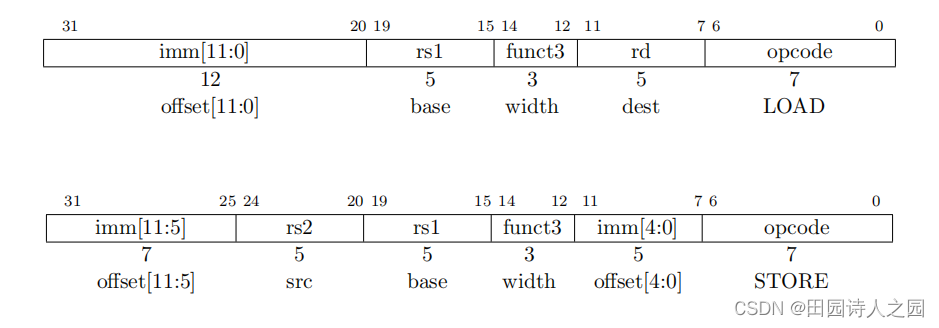

1.6 Load and Store Instructions

RV32I is a load-store architecture, where only load and store instructions access memory and arithmetic instructions only operate on CPU registers. RV32I provides a 32-bit address space that is byte-addressed. The EEI will define what portions of the address space are legal to access with which instructions (e.g., some addresses might be read only, or support word access only). Loads with a destination of x0 must still raise any exceptions and cause any other side effects even though the load value is discarded.

RV32I 是一种加载-存储架构,只有加载和存储指令才能访问内存,算术指令只能在 CPU 寄存器上运行。RV32I 提供字节寻址的 32 位地址空间。EEI 将定义地址空间的哪些部分可以用哪些指令合法访问(例如,某些地址可能只允许读取,或只支持字访问)。目标地址为 x0 的加载,即使加载值被丢弃,仍必须引发任何异常并导致任何其他副作用。

The EEI will define whether the memory system is little-endian or big-endian. In RISC-V, endianness is byte-address invariant.

EEI 将定义内存系统是小端(little-endian)还是大端(big-endian)。在 RISC-V 中,字节地址不变。

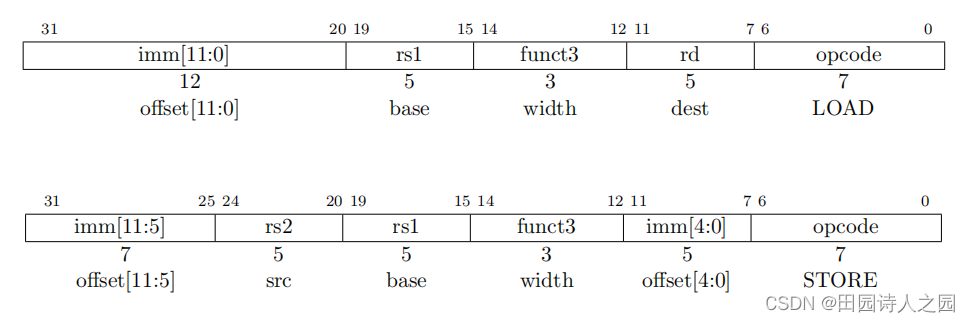

Load and store instructions transfer a value between the registers and memory. Loads are encoded in the I-type format and stores are S-type. The effective address is obtained by adding register rs1 to the sign-extended 12-bit offset. Loads copy a value from memory to register rd. Stores copy the value in register rs2 to memory.

加载和存储指令在寄存器和内存之间传输数值。加载采用 I 型编码格式,存储采用 S 型编码格式。有效地址由寄存器 rs1 加上符号扩展后的 12 位偏移获得。加载将内存中的值复制到寄存器 rd 中。存储时将寄存器 rs2 中的值复制到内存中。

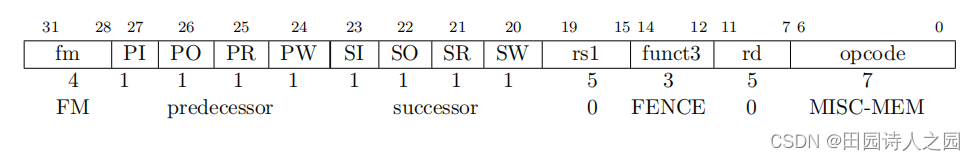

1.7 Memory Ordering Instructions

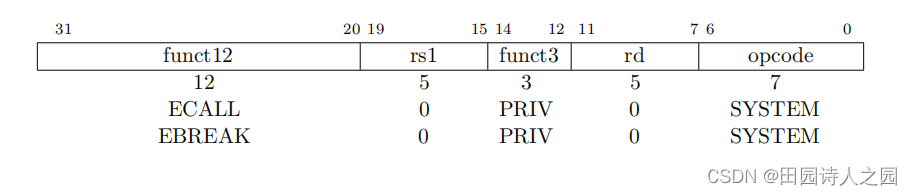

1.8 Environment Call and Breakpoints

These two instructions cause a precise requested trap to the supporting execution environment.

这两条指令会向支持执行环境发出一个精确请求陷阱。

The ECALL instruction is used to make a service request to the execution environment. The EEI will define how parameters for the service request are passed, but usually these will be in defined locations in the integer register file.

ECALL 指令用于向执行环境发出服务请求。EEI 将定义如何传递服务请求的参数,但通常这些参数将放在整数寄存器文件中定义的位置。

The EBREAK instruction is used to return control to a debugging environment.

EBREAK 指令用于将控制返回调试环境。

ECALL and EBREAK were previously named SCALL and SBREAK. The instructions have the same functionality and encoding, but were renamed to reflect that they can be used more generally than to call a supervisor-level operating system or debugger.

ECALL 和 EBREAK 以前的名称是 SCALL 和 SBREAK。这两条指令具有相同的功能和编码,但重新命名是为了反映它们的用途比调用监督级操作系统或调试器更广泛。

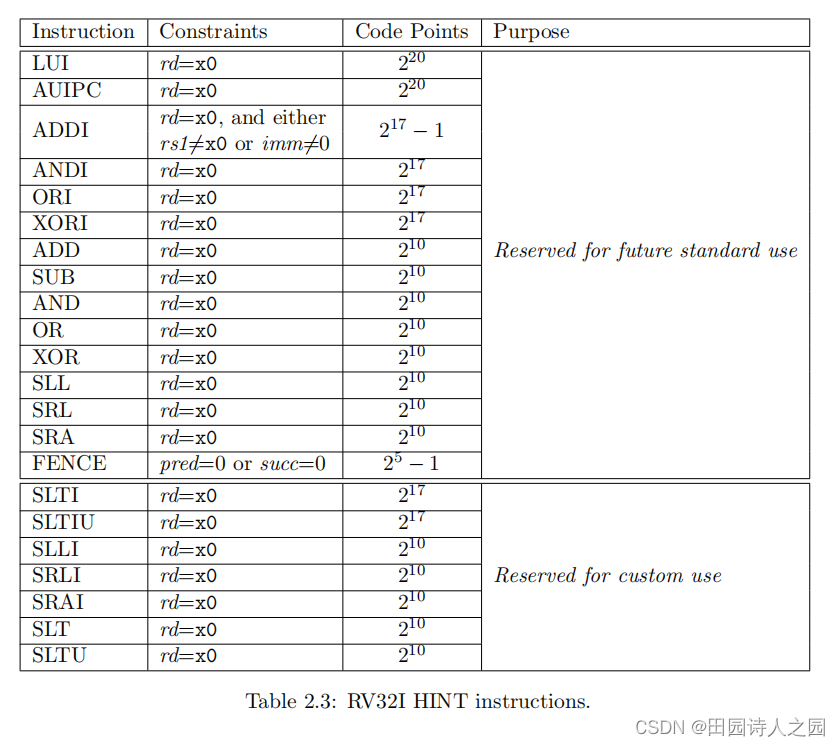

1.9 HINT Instructions

RV32I reserves a large encoding space for HINT instructions, which are usually used to communicate performance hints to the microarchitecture. HINTs are encoded as integer computational instructions with rd=x0. Hence, like the NOP instruction, HINTs do not change any architecturally visible state, except for advancing the pc and any applicable performance counters. Implementations are always allowed to ignore the encoded hints.

RV32I 为 HINT 指令保留了较大的编码空间,通常用于向微体系结构传达性能提示。HINT 被编码为 rd=x0 的整数计算指令。因此,与 NOP 指令一样,除了推进 pc 和任何适用的性能计数器外,HINT 不会改变任何架构上可见的状态。在任何情况下,都允许执行程序忽略已编码的提示。

Table 2.3 lists all RV32I HINT code points. 91% of the HINT space is reserved for standard HINTs, but none are presently defined. The remainder of the HINT space is reserved for custom HINTs: no standard HINTs will ever be defined in this subspace.

表 2.3 列出了所有 RV32I HINT 代码点。91% 的 HINT 空间是为标准 HINT 保留的,但目前尚未定义任何标准 HINT。HINT 空间的其余部分保留给自定义 HINT:该子空间将不会定义任何标准 HINT。

2 RV64I Base Integer Instruction Set

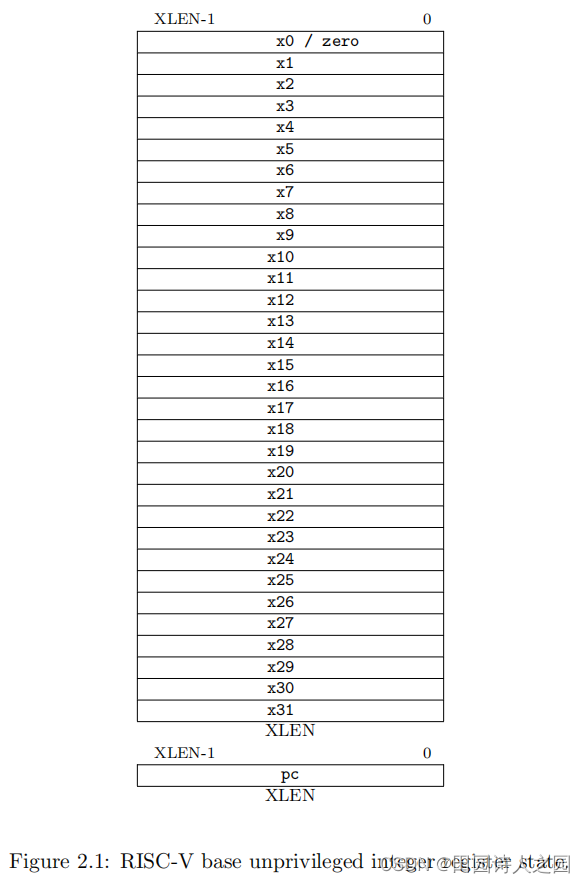

2.1 Register State

RV64I widens the integer registers and supported user address space to 64 bits (XLEN=64).

RV64I 将整数寄存器和支持的用户地址空间扩展到 64 位(XLEN=64)。

RV64I寄存器功能分类:

2.2 Integer Computational Instructions

Most integer computational instructions operate on XLEN-bit values. Additional instruction variants are provided to manipulate 32-bit values in RV64I, indicated by a ‘W’ suffix to the opcode.

大多数整数计算指令都在 XLEN 位数值上运行。在 RV64I 中,还提供了其他指令变体来操作 32 位数值,操作码后缀为 “W”。

These “*W” instructions ignore the upper 32 bits of their inputs and always produce 32-bit signed values, i.e. bits XLEN-1 through 31 are equal.

这些 "*W "指令忽略其输入的高 32 位,始终产生 32 位有符号数值,即 XLEN-1 至 31 位相等。

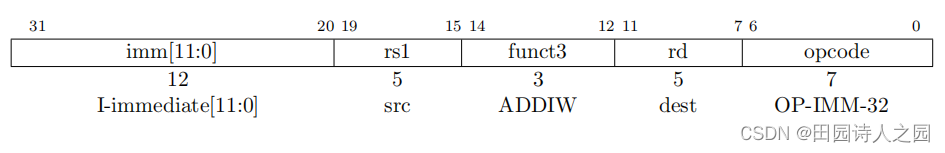

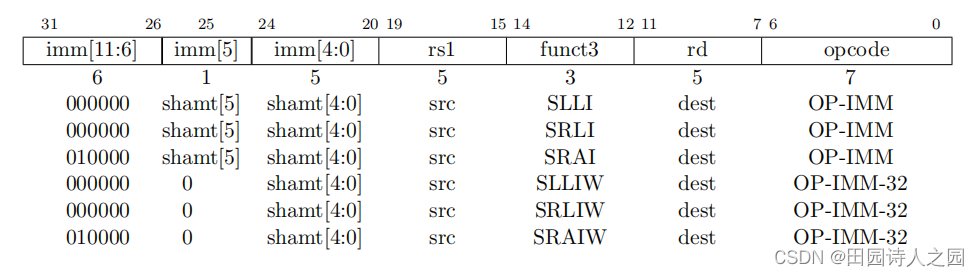

2.2.1 Integer Register-Immediate Instructions

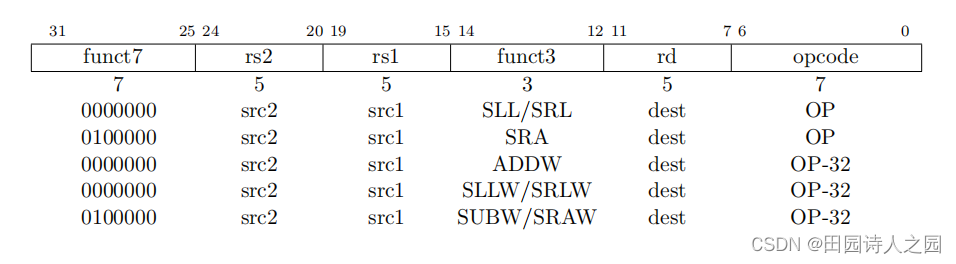

2.2.2 Integer Register-Register Operations

2.3 Load and Store Instructions

RV64I extends the address space to 64 bits. The execution environment will define what portions of the address space are legal to access.

RV64I 将地址空间扩展到 64 位。执行环境将确定地址空间的哪些部分可以合法访问。

The LD instruction loads a 64-bit value from memory into register rd for RV64I.

LD 指令将内存中的 64 位值加载到 RV64I 的寄存器 rd 中。

The LW instruction loads a 32-bit value from memory and sign-extends this to 64 bits before storing it in register rd for RV64I. The LWU instruction, on the other hand, zero-extends the 32-bit value from memory for RV64I. LH and LHU are defined analogously for 16-bit values, as are LB and LBU for 8-bit values. The SD, SW, SH, and SB instructions store 64-bit, 32-bit, 16-bit, and 8-bit values from the low bits of register rs2 to memory respectively.

LW 指令从内存中加载一个 32 位值,并将其符号扩展到 64 位,然后将其存储到 RV64I 的寄存器 rd 中。而 LWU 指令则是将内存中的 32 位值零扩展到 RV64I。对于 16 位数值,LH 和 LHU 的定义类似;对于 8 位数值,LB 和 LBU 的定义类似。SD、SW、SH 和 SB 指令分别将寄存器 rs2 低位的 64 位、32 位、16 位和 8 位数值存储到内存中。

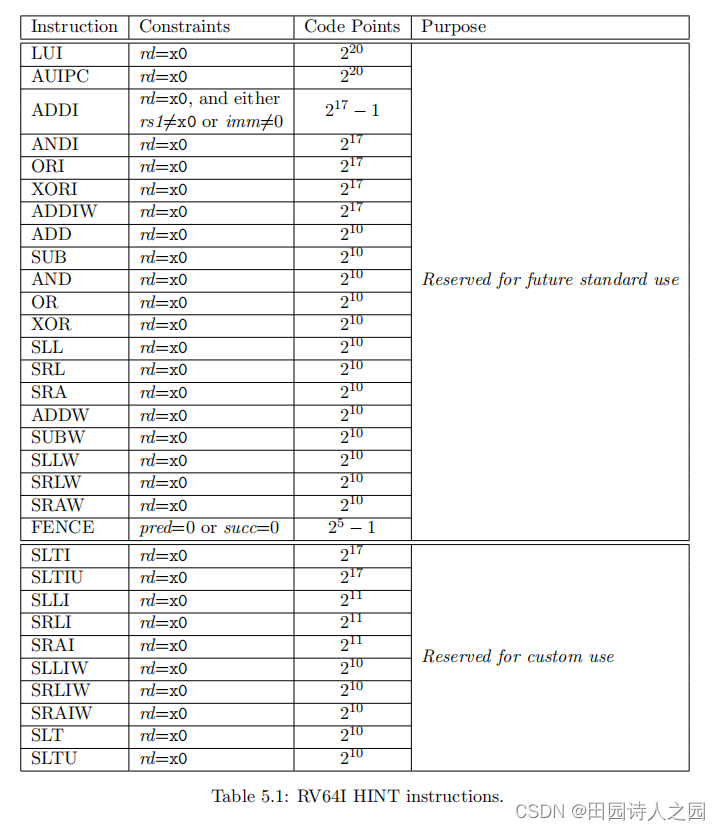

2.4 HINT Instructions

All instructions that are microarchitectural HINTs in RV32I (see Section 2.9) are also HINTs in RV64I. The additional computational instructions in RV64I expand both the standard and custom HINT encoding spaces.

所有在 RV32I 中属于微架构 HINT 的指令(参见第 2.9 节)在 RV64I 中也属于 HINT。RV64I 中的附加计算指令扩展了标准和自定义 HINT 编码空间。

Table 5.1 lists all RV64I HINT code points. 91% of the HINT space is reserved for standard HINTs, but none are presently defined. The remainder of the HINT space is reserved for custom HINTs: no standard HINTs will ever be defined in this subspace.

表 5.1 列出了所有 RV64I HINT 代码点。91% 的 HINT 空间是为标准 HINT 保留的,但目前尚未定义任何标准 HINT。其余的 HINT 空间是为自定义 HINT 保留的:该子空间将不会定义任何标准 HINT。

参考文档

《The RISC-V Instruction Set Manual Volume I: Unprivileged ISA》