文章目录

- 时钟

- 主时钟图

- 时钟树

- 系统时钟

时钟

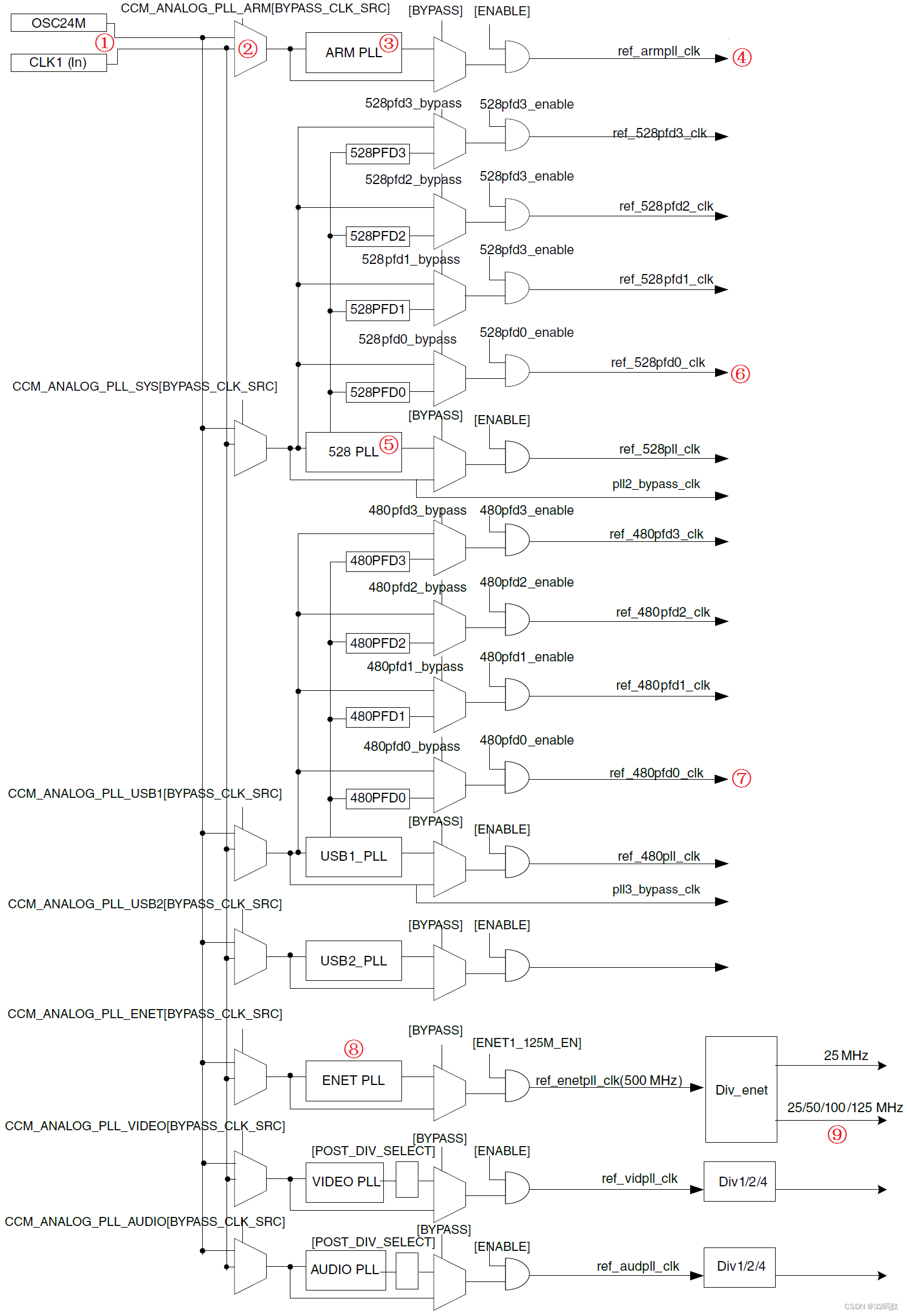

- 主时钟图表明了各个 PLL 时钟(总共 7 个 PLL)的由来和通路;

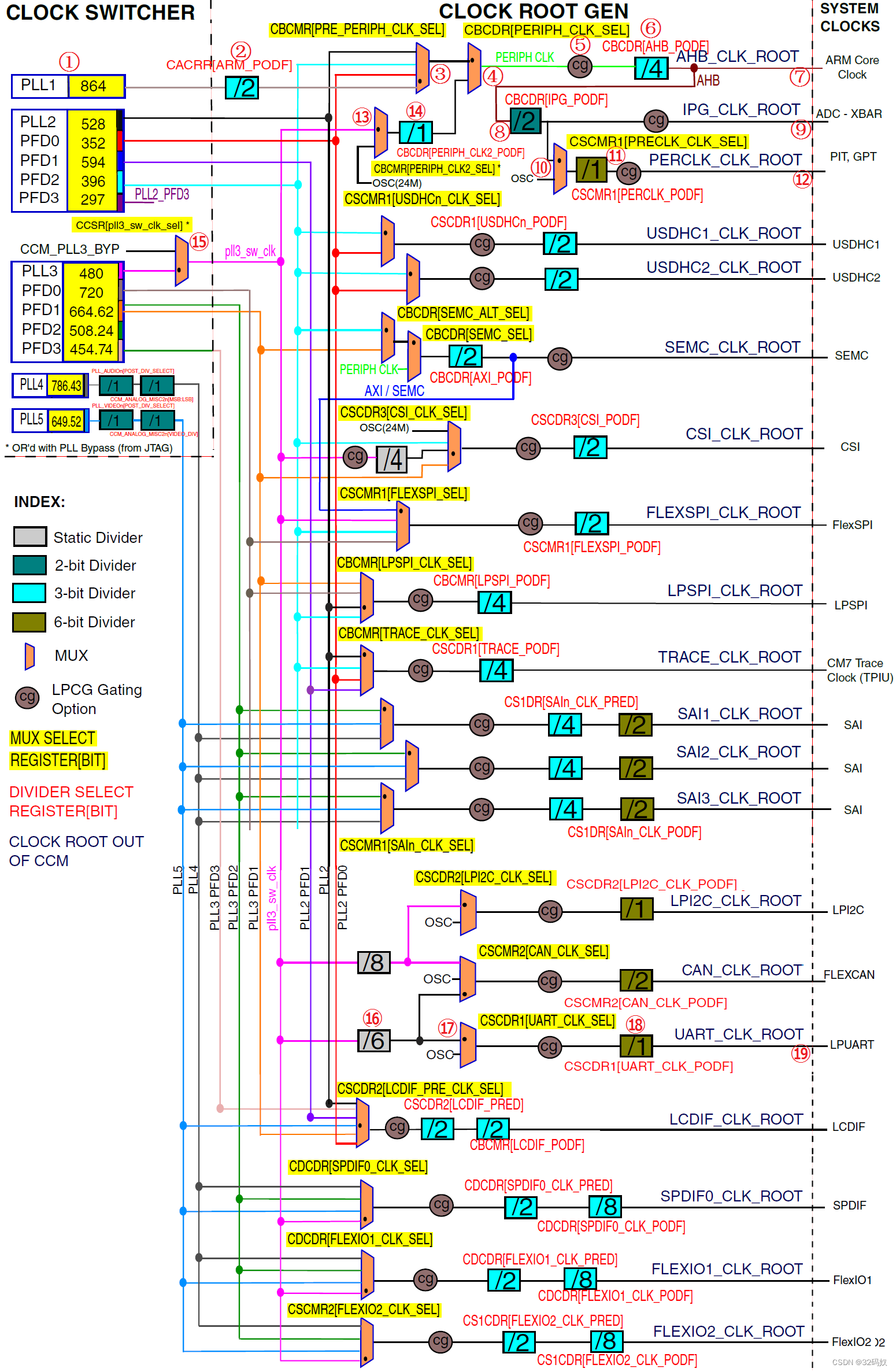

- 时钟树图,则表明了 RT1052 内部各个根时钟(CLK ROOT)的由来和通路。

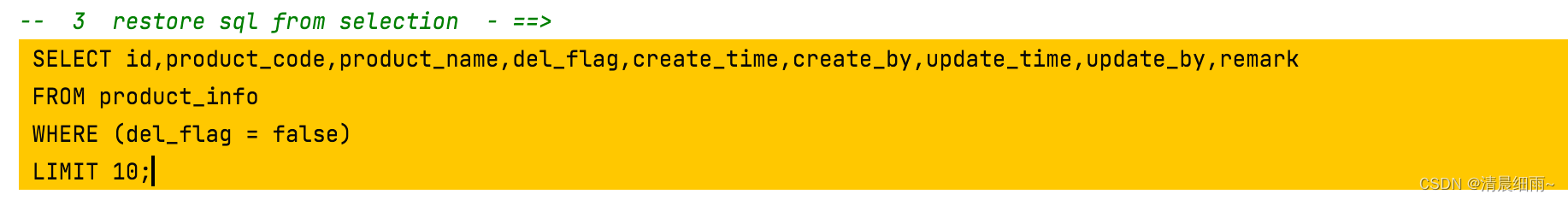

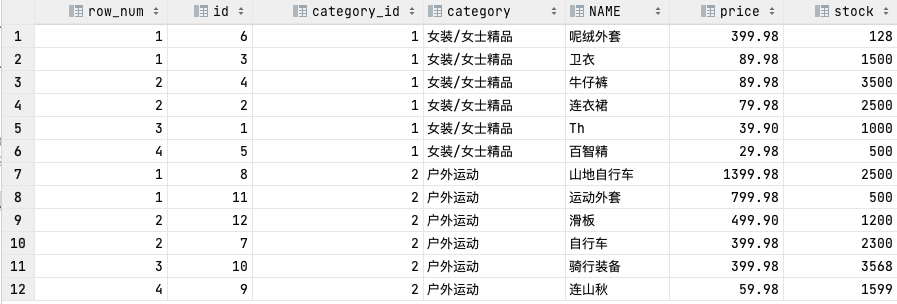

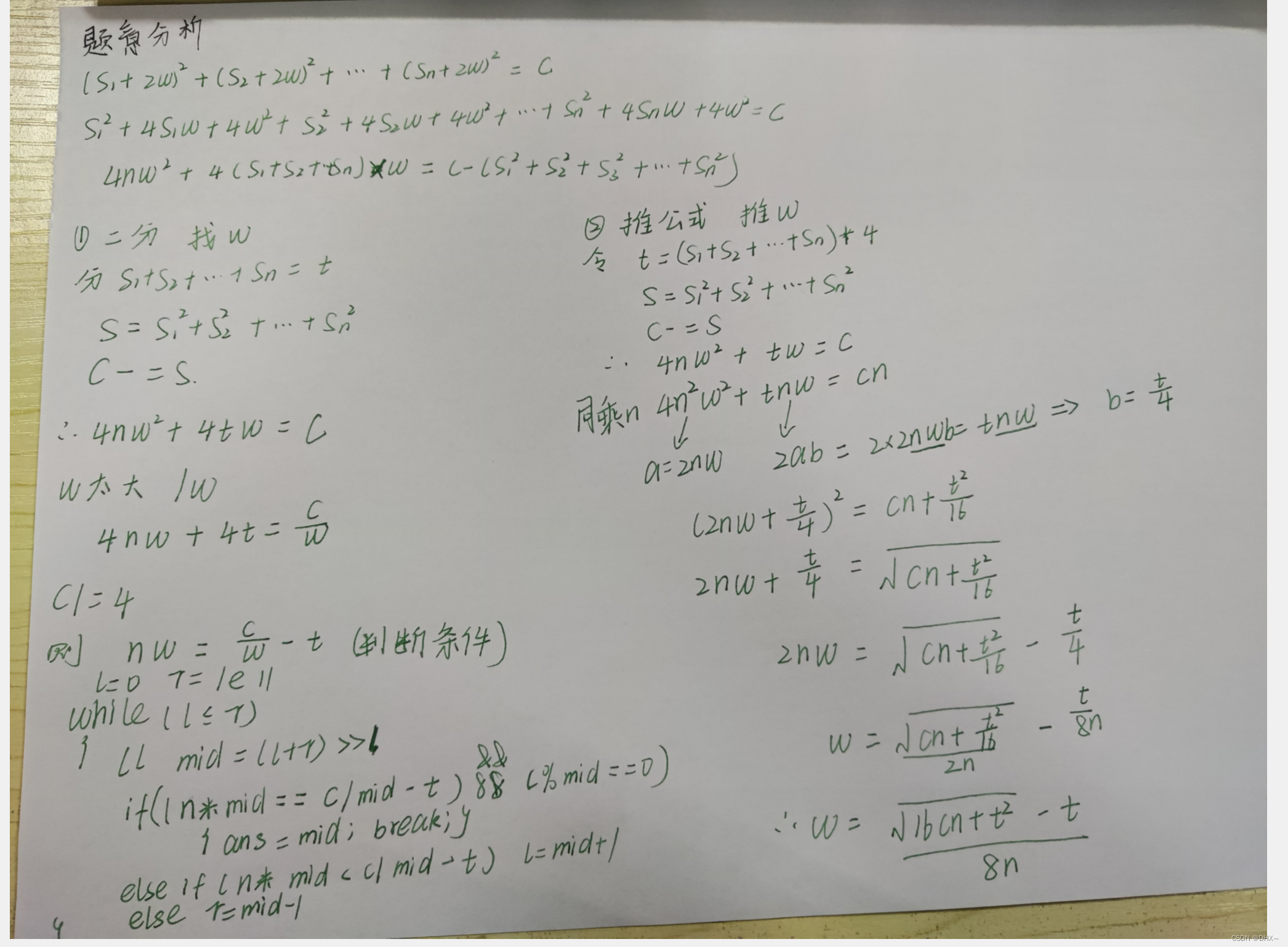

主时钟图

图中总共有7个PLL,分别是:ARM PLL(PLL1)、528 PLL(PLL2)、USB1 PLL(PLL3)、AUDIO PLL(PLL4)、VIDEO PLL(PLL5)、ENET PLL

图中总共有7个PLL,分别是:ARM PLL(PLL1)、528 PLL(PLL2)、USB1 PLL(PLL3)、AUDIO PLL(PLL4)、VIDEO PLL(PLL5)、ENET PLL

(PLL6)和 USB2 PLL(PLL7)。

- 其中 PLL2 和 PLL3,每个 PLL 可以有 5 路输出(1PLL+4PFD,PFD:Phase Fractional Dividers,即相位分数分频器,我们可以理解为将 PLL 输出再乘以一个分数(分数可以大于 1,也可以小于 1),然后再做为输出)。

时钟树

系统时钟

SysTick 是一个 24 位的倒计数定时器,当计到 0 时,将从RELOAD 寄存器中自动重装载定时初值。只要不把它在 SysTick 控制及状态寄存器中的使能位清除,就永不停息。

- 利用 RT1052 的内部 SysTick 可实现延时,既不占用中断,也不占用系统定时器。

- 注意:我们设置 SysTck 的时钟源为内核时钟,其频率为系统主频(一般为:600Mhz)。