(CPU外部的)总线

用于连接computer3大模块(M+C/GPU+IO)

CPU内部的片内总线判优由时序逻辑实现

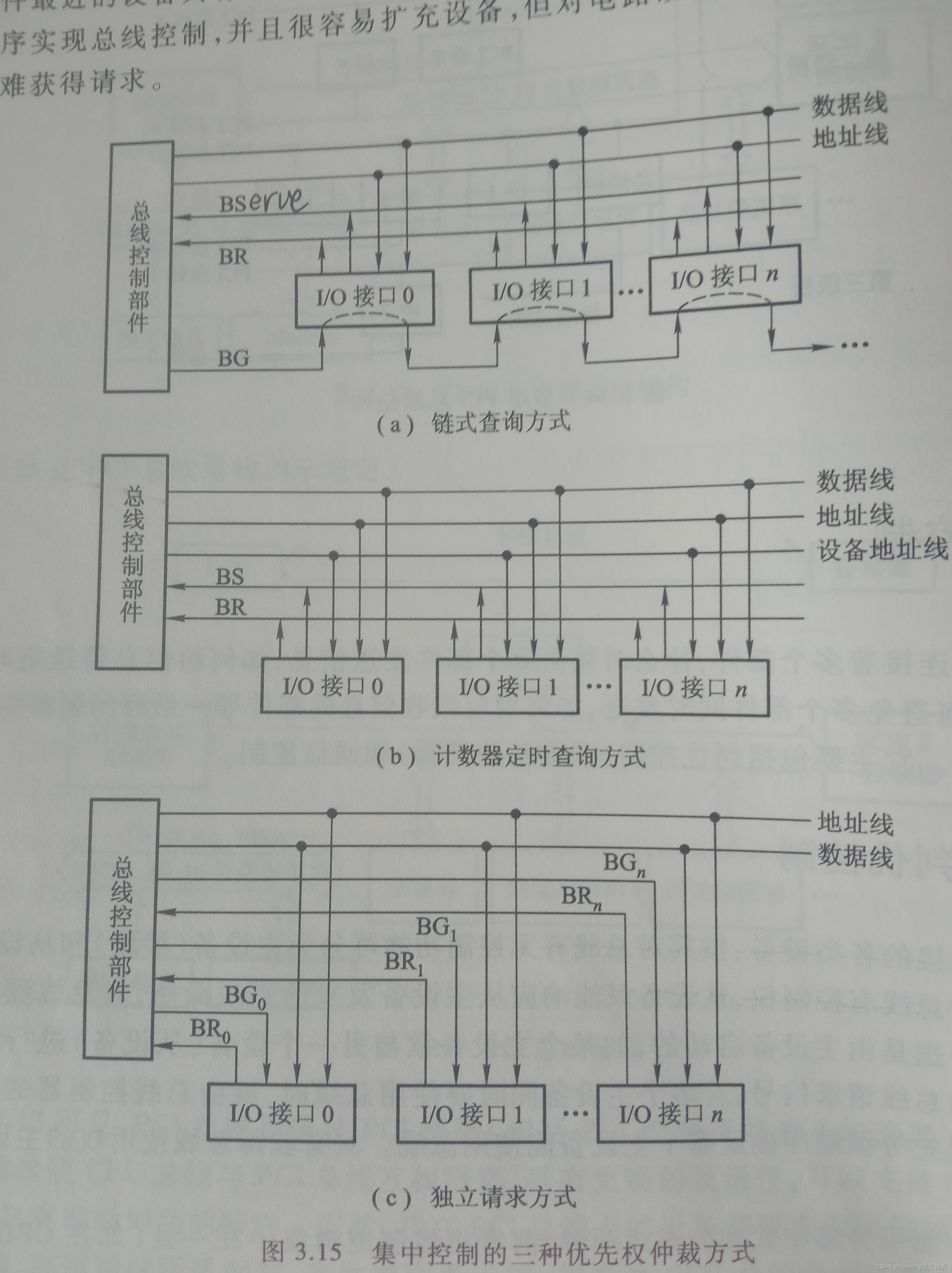

composition& priority-judging

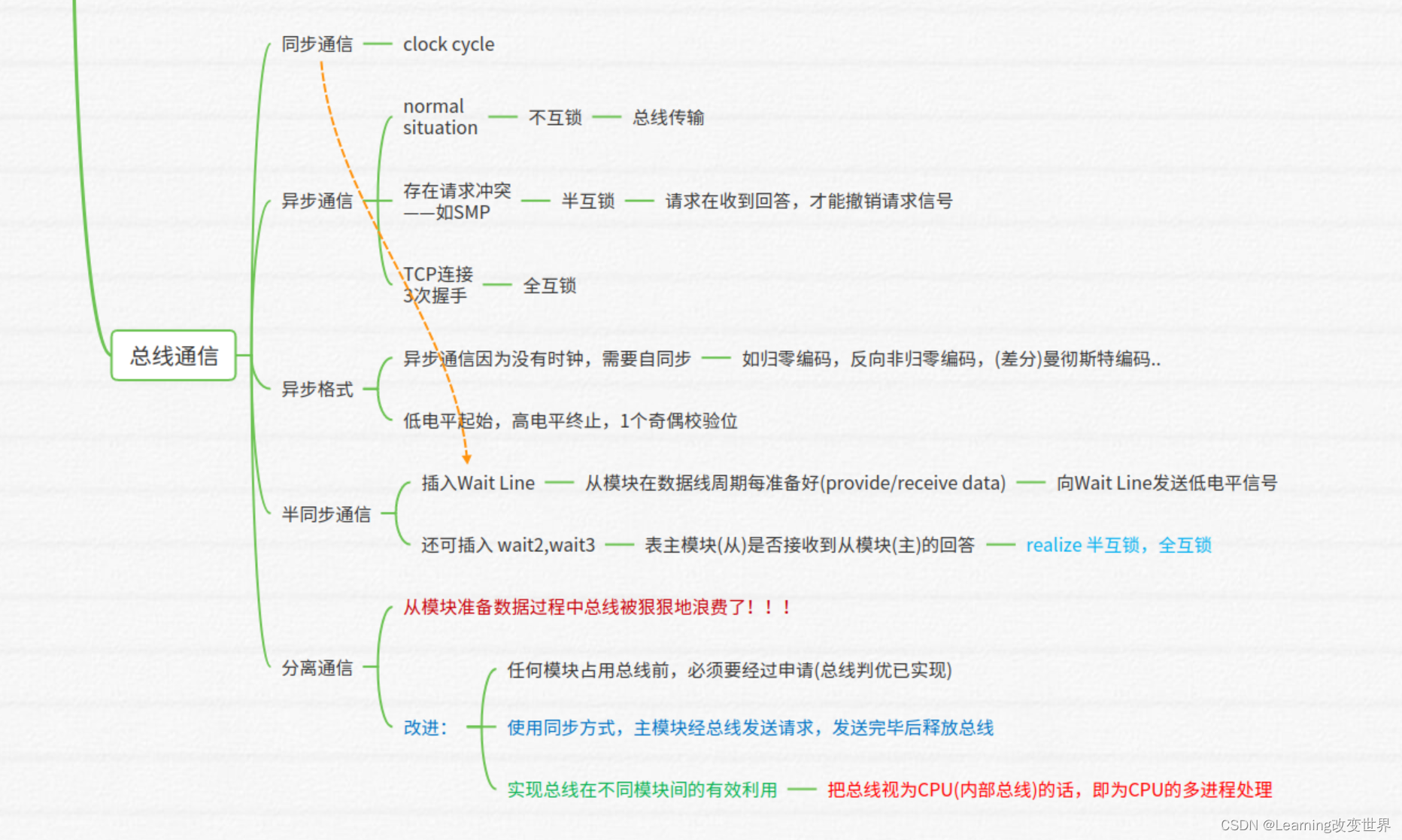

通信方式

- CPU内部的片内总线用于取指、译码、执行、中断的数据通信;

IO

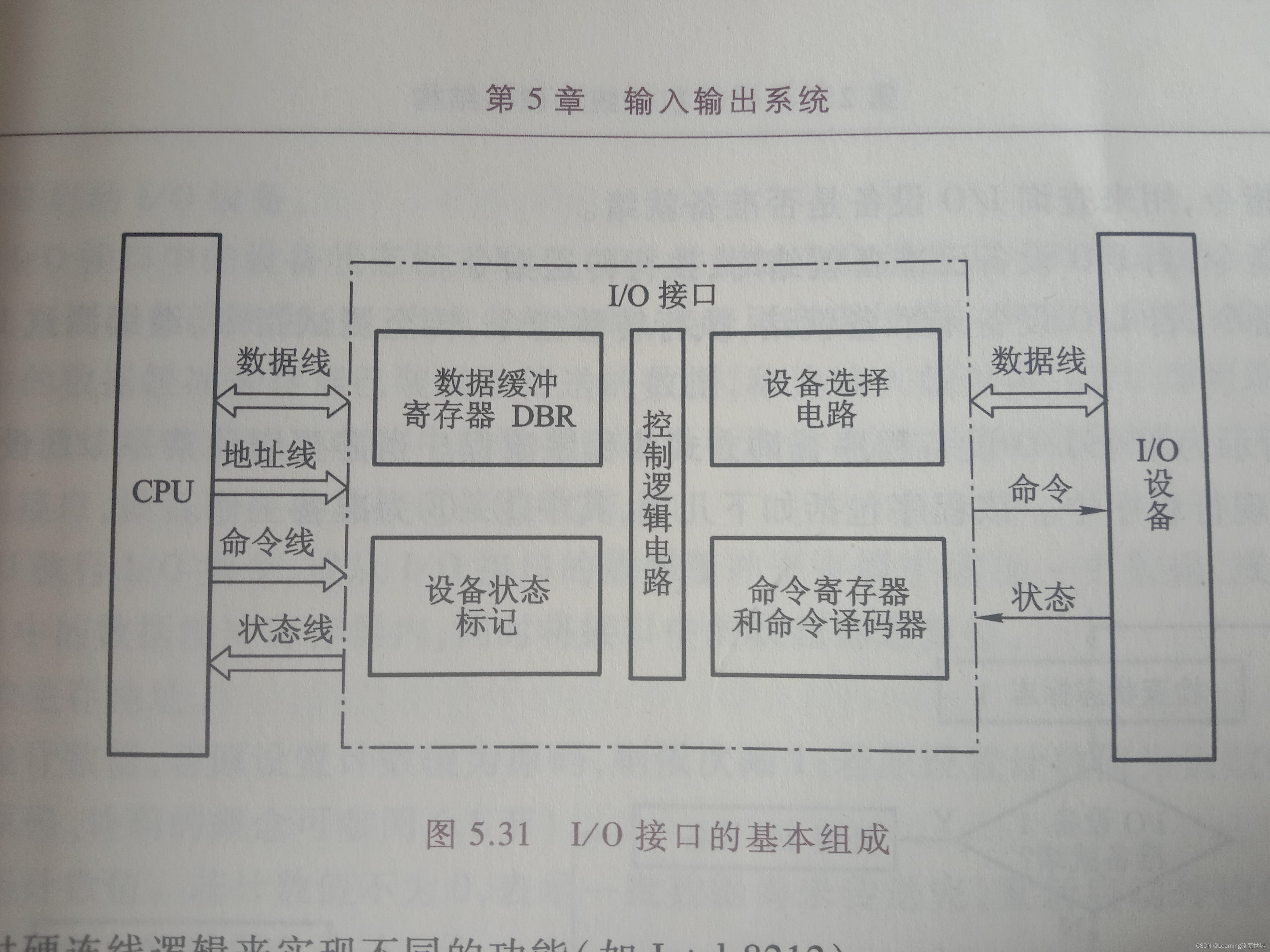

- 总线分为控制线、数据线和地址线,对IO设备的控制也是如此,

- 只是不同的IO数据传输速率差别较大,通过IO接口转接,

- 此外,CPU准备好了,IO未必准备好,控制线由此分为命令线和状态线,

在程序中断方式、程序查询中,制定(设备)地址线后,CPU发送信号到命令线,IO准备好后通过状态线响应,之后方可从数据线读取; - 若干个端口(存放数据、地址、控制信息的寄存器)+控制逻辑=接口;

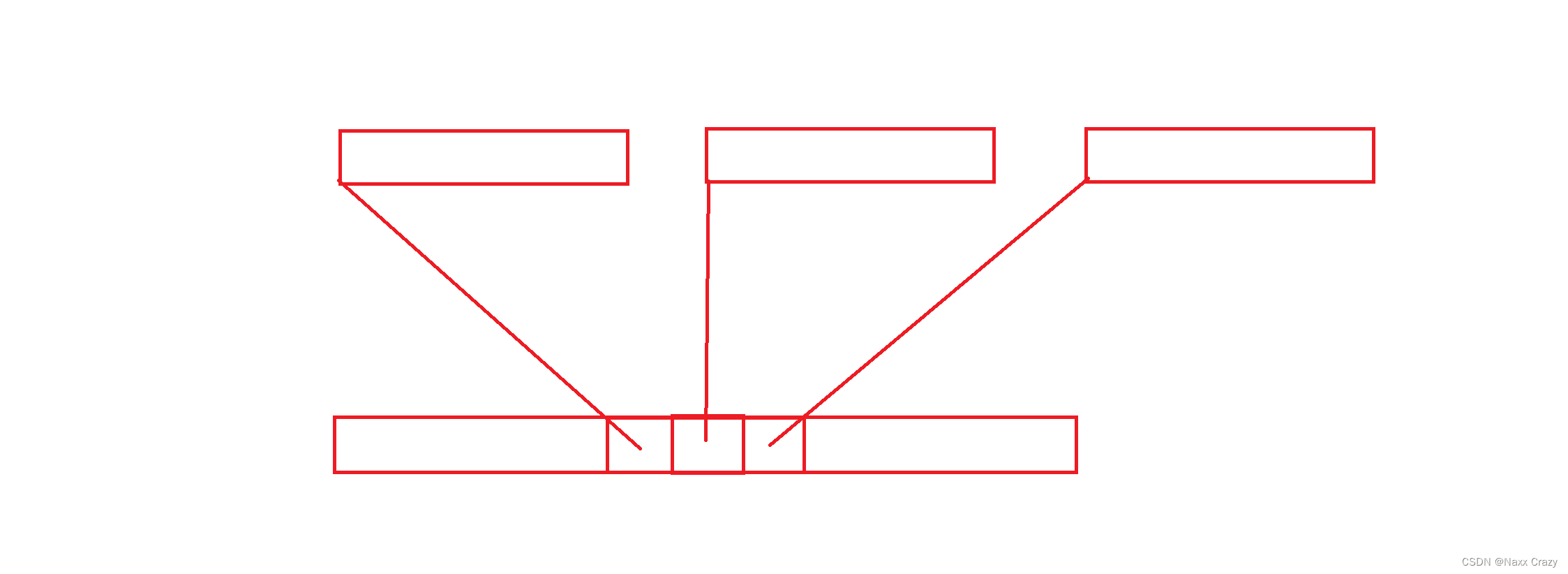

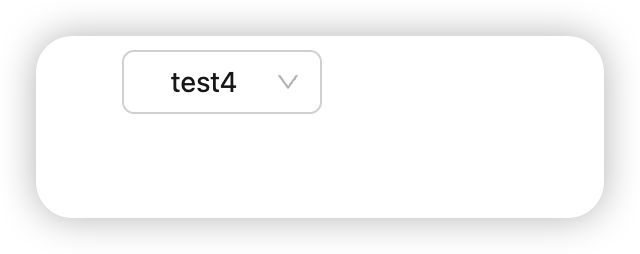

IO设备的工作原理,IO接口的构成

IO接口的工作流程

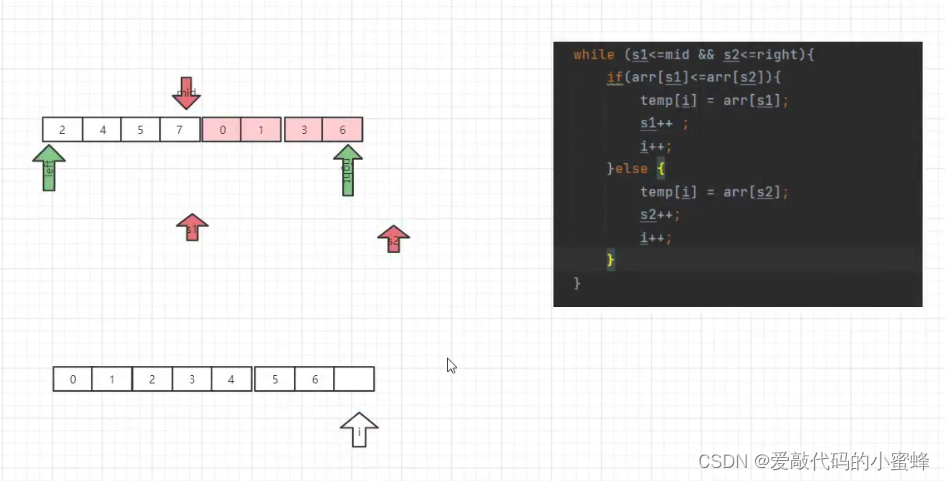

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-ZEC8nCZS-1689816967399)(./assets/IMG_20230720_093221.jpg)]](https://img-blog.csdnimg.cn/ab12452776aa4bc19b06bb125040a9e5.png)

从IO读入

- CPU由地址线确定要读入的地址,通过控制线发送读信号,

- IO控制逻辑发送控制信号到IO,状态控制寄存器标记为 待写入/读IO

- 外设准备好后,通过状态线发送准备状态到IO控制逻辑,寄存器=D=1,B=0,ID=0,CD=0

- IO控件接受IO发送的数据,并存储到数据缓冲寄存器,寄存器=D=1,B=0,ID=1,CD=0

- 将状态/控制寄存器标记为 已写入IO,CPU未读取/读IO,状态线通知CPU可以读取,

- CPU发送读信号,然后从缓冲区读取,之后状态/控制寄存器 标记为 已读取/读IO为,寄存器=D=1,B=0,ID=1,CD=1

- 状态/控制寄存器——标记外设状态,控制IO的读写等操作

写入IO

-

CPU由地址线确定要写入的地址,控制线发送写信号,状态/控制寄存器标为 未写入/写IO

-

IO设备通过外设控制逻辑向设备发送写信号,

-

IO数据缓冲寄存器接受CPU的写入数据,状态/控制寄存器标为 已写入控件,IO未读取/写IO

-

IO准备好通过状态线通知IO控件,IO控件通过控制逻辑发送写信号

-

然后将数据缓冲寄存器的数据输出到外设,状态/控制寄存器标为 已读取/写IO

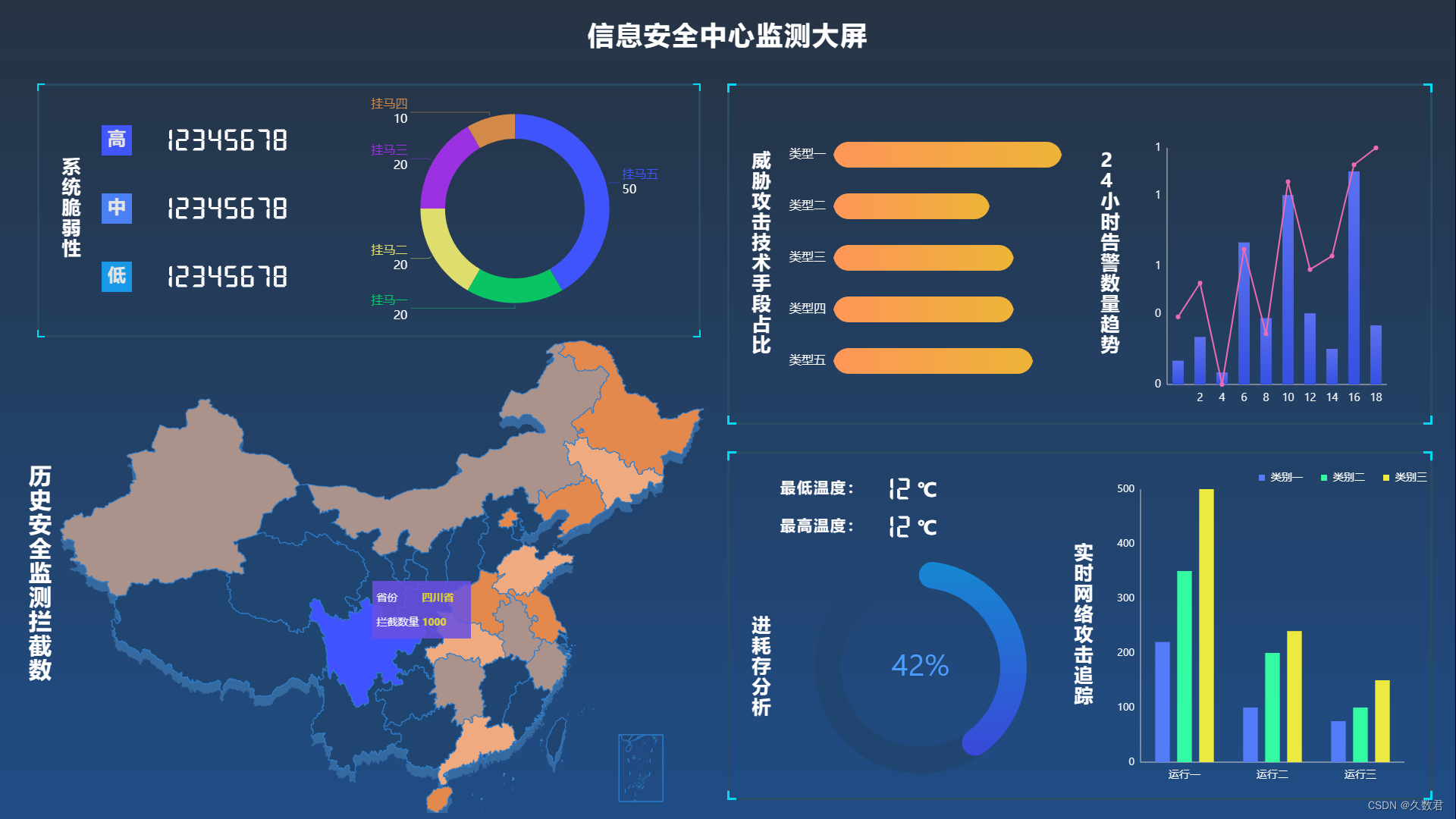

IO与CPU、主存的交互方式

- 这3种IO与系统的交互

并没有优劣之分,只是使用的场景不同 - 程序中断可以取代程序查询吗?——需要编写响应的中断程序,可以将CPU从查询的等待中解放出来;

- 程序查询用于CPU与IO交换数据,程序中断用于CPU与IO交换数据等中断服务处理

- DMA用于主存与IO交换数据,程序中断需要中断请求、判优、响应、服务、返回,耗时

- DMA控制逻辑相当于1个小CPU,负责IO与MM的传输控制