1、关于库的定义

PADS中的元件库分为四个文件 :*.ld9 *.ln9 *.pd9 *.pt9 即CAE、 LINES、PCB DECAL、PART TYPE。只有这四个文件都存在才是一个完整的库,才可以加载。

我们设计的电路所用到的元件必须在PADS logic和PADS layout中都存在,其中包括了元件、逻辑封装(CAE)、PCB封装,下面就来讲这三者的区别。

PCB封装和CAE(逻辑封装)是一个具体封装,不具有电气特性,它是元件类型的一个组成部分,是元件类型在设计中的一个实体表现,它指明的是所属元件的类型。

a.PCB封装实际上是零件在PCB板上的脚印图,并且每一个封装名都是唯一的

b.CAE封装是零件在原理图上的电子符号,并且每一个封装名都是唯一的

注意:PCB封装只能在PADS的封装编辑中建立,CAE封装只能在PADS logic中建立。

c.元件类型在库管理系统中,用元件图标来表现,他不是唯一的,是类的概念。在PADS系统中,同一元件有多种封装的情况,因此使用类来管理这种情况。一个元件类型就是一个类,在PADS中一个元件类型最多包含4种不同的CAE封装和16种不同的PCB封装,这些封装中存在优先级。当我们在库文件中添加元件的时候,我们在对话框中输入的查找条件不是CAE封装名,也不是PCB封装名,而是元件封装的元件封装名。

另外还需要了解门封装的概念。元件是一个包含常规设置、pcb封装、门、管脚信息、属性的大类,而门封装中可以添加4个CAE封装,一个元件也可以有多个门封装(比如多引脚的MCU、FPGA)。编辑CAE封装的时候,需要选择编辑哪个门,哪个CAE封装。尤其需要注意阻容等通用CAE封装的编辑,因为阻容都是多个元件使用同一个CAE封装,而一旦修改了该CAE封装,所有使用这个CAE封装的元件都会被改动。

最后说一些建封装时的小技巧,修改好一个封装后,保存的时候选择另存为,而不是保存(因为之前刚开始使用pads建封装的时候,会复制一个封装,然后在该封装上面修改,而点击保存的话会使这两个封装一起被修改,所以同事传授经验说选择另存为不会发生这种情况)另外pcb封装在另存为的时候会跳出一个“是否希望创建新的元件类型”的对话框,这个时候需要选择“否”,选择“是”的话会在元件封装库中新建一个和pcb封装同名的封装。

2、库的检查

元件的检查:

a、logic图形有无错误,和数据手册是否对应。

b、检查元器件信息

常规--确保逻辑系列与当前元件一致,比如电容是C、电感是L,这个会影响后续原理图中的元 器件位号的前缀。

PCB封装--确保PCB封装是正确的。

门--确保CAE封装是正确的,需要注意多个元件使用一个门的情况,此时不要随便修改该封装。

管脚--需要注意有方向的元器件,比如二极管,CAE的±极性是否和PCB decal的±极性一致,不一致的话可以在这边直接修改。

属性--按照自己公司要求添加相应信息

PCB Decal的检查:

a、检查焊盘

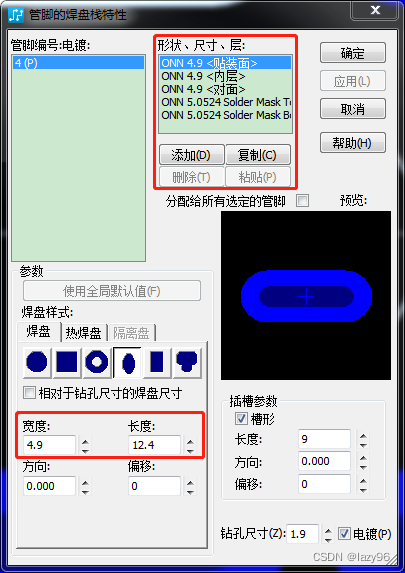

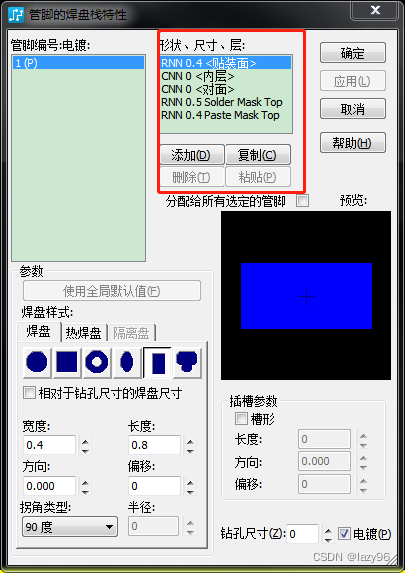

插件焊盘中需要添加的层,除了贴装面、内层、对面之外,还需要添加solder mask的top和bot层,需要注意每一层的焊盘信息都需要修改。

使用椭圆形焊盘时,需要注意长度数值必须要比宽度数值大,否则会报错。假如管脚方向与实际封装方向不符,可以在方向处输入旋转角度修改方向。

表贴焊盘需要贴装面、solder mask top以及paste mask top

b、检查丝印

设计外框丝印时需要画在silkscreen和assembly层,设计的时候2D线可以使用路径,而不是多边形或者矩形。因为在后续设计PCB拖动元件的时候,2D线的外框可以显示,但是矩形的外框会消失,只有焊盘。这样会导致布局的时候元器件位置不好把握,会过近。

检查一脚引脚的丝印。

c、检查波峰焊圈

放在layer15,波峰焊圈比焊盘再多2mm。贴片元器件不可靠近波峰焊圈。

检查元器件最小摆放位置边框

放在layer14,接插件的框比外框多3mm,IC的框比两边引脚多1mm。这个框是指,两个元器件之间相距3mm,而不是在布局的时候两个元器件需要贴框放置(即元器件间距6mm)。

3、pcb设计时的一些技巧

a、关于原理图与pcb的链接

在原理图界面,选择pads layout的图标![]() ,假如只打开一个pcb和一个原理图,就会自动连接,不需要重新选择文档。

,假如只打开一个pcb和一个原理图,就会自动连接,不需要重新选择文档。

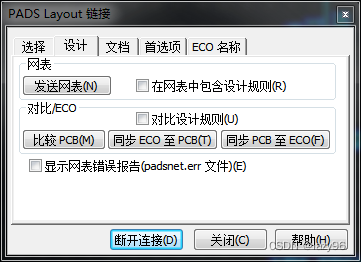

原理图更新后,选择同步ECO至PCB,后续会跳出检查报告,假如有问题需要跟硬件工程师及时沟通。

这个状态下就是已链接的状态,在pcb点击元器件,原理图中会跳转,反之亦然。

另外在pcb中元器件模块化布局的时候,需要按原理图现先元器件分开,而选中logic中的元器件之后,需要在pcb界面点击shift(不点击shift,移动的是logic中的器件)然后ctrl+e移动。

b、网络相关设置

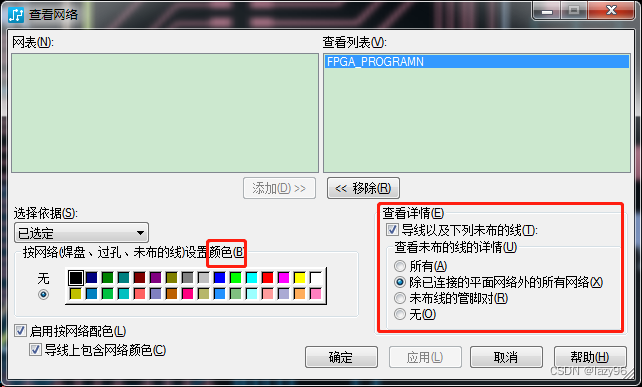

右键选择网络--选中想要选择的网络--右键查看网络 可以设置网络颜色和飞线

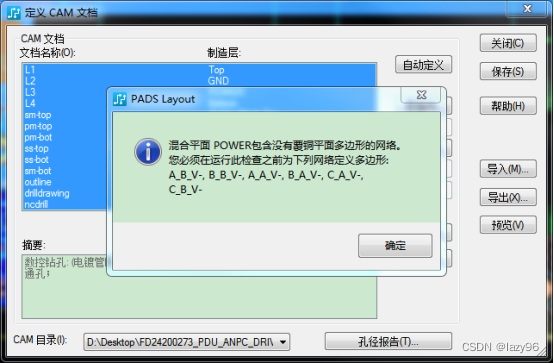

c、导出gerber的时候出现报错--混合平面包含没有敷铜平面多边形的网络

出现这个问题是因为power层走线了,将power层设置为无平面就不会报错。

d、DRC检查

DRC的时候需要打开所有层,并且全局显示。这样出来的报错才是准确的。不然只打开一层或者局部显示,报错只会给出当前显示界面的错误,会有遗漏。

e、铺铜

如果同一网络连接不上焊盘,可以看看焊盘有无设置为热焊盘。

修改默认的铜皮和间距规则之后,假如铺铜没有改变,可以看样一下类和网络中是否也有规则。