众所周知,以太网已经深入我们的生活无处不在,企业、校园、大数据中心和家庭等都离不开网络,否则我们的生活将受到严重的影响。

以太网的接口速率也是迅速发展:10M、100M、GE、10GE、40GE、100GE,到目前逐步成熟的2.5GE、5GE、25GE、50GE甚至400GE,基本是每10年速率10倍增长的发展趋势。

很多数据中心和运营商也已准备将其网络从100GE扩展到400GE,以支持第五代无线技术(5G)、人工智能(AI)、虚拟现实(VR)、物联网(IoT)、自动驾驶汽车等新兴技术所需的带宽和响应时间。

然而任何新型网络接口速率、网络设备的研发至形成最终产品及网络新技术从研究到落地,每个阶段都离不开测试验证,而且已经给测试带来了极大的挑战。同时,高性能的稳定的高速率网络测试仪的发展,却有点跟不上网络设备的研发需求。

所以高速率、稳定的网络测试仪的发展刻不容缓,尤其是掌握核心技术的国产化网络测试仪产品。

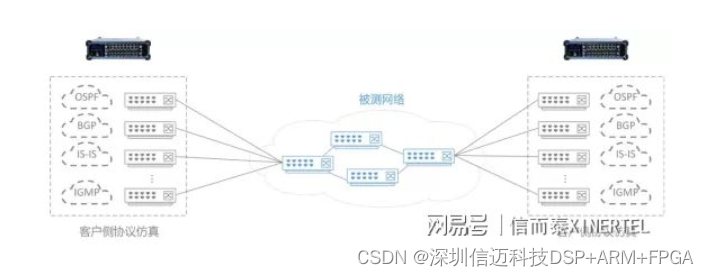

国内电信运营商进行的大规模的数据中心交换机或是核心路由器的测试场景对测试仪提出了极高的要求。

- · 稳定性

- 具备长时间稳定打流、统计及协议仿真的能力,如7x24小时长时间稳定运行;

- · 可重复性

- 同样的物理环境及网络条件,多次测试结果必须一致;

- · 准确性

- 测试结果必须能准确的反映被测设备或系统的真实指标情况,如吞吐量指标、时延和抖动的精确性、流量调度的精确性、流量统计的精确性;

- · 高性能

- 支持所有包长(如64-16000字节或IMIX混合包长)线速发流及统计的能力、超高的路由交换协议仿真能力(如多session数的BGP/OSPF/ISIS/PPPOE/IPOE/EVPN等);多端口(如上百个以上的100GE/10GE)多业务(如IPV4/IPV6/MPLS/Multicast)流量场景仿真能力;

- · 标准性

- 具备符合国际测试标准RFC-2544,RFC-2889、RFC3511、RFC3918等;

- · 丰富的接口类型

- 支持1GE/2.5GE/5GE/10GE/

- 25GE/40GE/50GE/100GE/400GE等多种接口类型,支持多机框级联搭建大规模的测试场景。

而目前市面上存在的网络测试仪主要有两种架构。

基于x86+DPDK+网卡的测试仪

X86的编程相对容易,调试手段更加丰富,成本有一定的优势,在要求不高的功能性测试方面,是一个不错的选择。

基于FPGA+x86混合的测试仪

FPGA+x86这样的软硬集合的测试系统,则适用于高性能、全覆盖、测试场景规模大、测试业务复杂的测试场景。

FPGA+x86的混合架构,一方面利用了FPGA越来越强大的数据硬件层面的并行性,另一方面也结合了CPU在控制层面的处理灵活性,同时由于FPGA和CPU本质上都是可编程的系统,根据业务处理的需要,可以在FPGA硬件和CPU软件之间灵活地移动业务划分边界,实现整个业务流程的全面优化。

我们按照前面所说的电信运营商的复杂测试场景要求,对两种架构的测试仪进行一个全面的对比分析如下:

64-16000字节包长的线速发流及统计能力

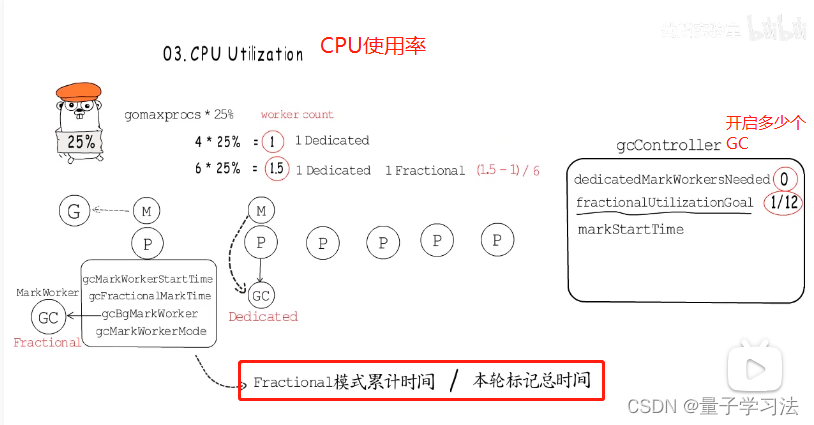

x86+DPDK+网卡:以图示的100G网络为例,在64字节包长的情况下,大概每秒会收发150M个数据包,以目前的CPU的计算和存储存取能力是无法处理的,而基于FPGA架构的测试仪没有此限制。根据DPDK官网公开发布的最新数据(2019·10·9)【数据来源:DPDK官网 www·dpdk·org】,采用图1的系统配置,可以明显看出在64,128,256等小字节情况下无法做到100G线速收发包;

FPGA+x86:所有字节可以做到线速发包与统计。

图1. X86+DPDK测试系统配置

所能达到的小字节包长线速性能如下图所示(下图 - X86系统的各包长测试性能)。

时延和抖动的精确性

时延测试的精度在网络测试中是非常重要的指标。

x86+DPDK+网卡:X86系统是面向通用计算的系统,它本身的基准时钟精度就不高,同时OS的调度误差至少在us量级;如果x86系统的NIC不支持在物理层插入时间戳的话,需要由软件系统来处理网络时延,这将带来进一步的误差;所以通常网络测试需要的精确至10ns量级的时延难以在面向计算的通用x86平台上实现;

FPGA+x86:在FPGA平台上,通过0.1~0.001PPM精度的晶振,产生高达400M的时钟,可以将时延的精度控制在2.5ns数量级别。

存储系统灵活性

x86+DPDK+网卡:x86系统面向通用计算,目前主流的内存系统是DDR4内存,带宽大但是访问延迟也大,根据读写访问模式的不同,可能会带有延迟抖动;

FPGA+x86:FPGA的内存,可以根据需要组合片上RAM(可以实现cache功能)+DDR+QDR+RLDRAM等各种内存技术,优化带宽需求型和延迟访问需求型。

协议加速的能力

x86+DPDK+网卡:无额外资源来实现TCP offloading等协议加速功能;

FPGA+x86:FPGA是硬件的可编程系统,可以根据硬件资源的多少,以及业务处理的需要,在协议处理方面和x86系统灵活地划分接口界限,实现TCP offloading等协议加速功能,把协议处理中的计算密集型的无状态任务在硬件层面并行化,可以大大增强整个系统的处理能力。

2-3层流量调度的精确性

x86+DPDK+网卡:x86系统在高速端口上无法实现小字节包长线速发流,更谈不上精准的流量调度了;

FPGA+x86:面对测试业务流量越来越复杂和规模越来越大的交换机、路由器,FPGA系统架构下支持产生成千上万条流(比如高端测试仪中典型的64K条流),并且可以对每条流之间的带宽比例、发送调度模式做到精确控制,甚至精确到小数点后面5位。

统计的实时性能和准确性

x86+DPDK+网卡:CPU的测试功能软件实现本质上是一个串行的指令集合,随着多核的超线程等新技术的实现,在指令级别可以实现部分的并行,但是对于一些统计数据,比如实时的每秒收发帧数等,至少是由两个参数来定义的(一定的时间间隔delta和该间隔内的收发包数),若是这两个参数的读取是在一个CPU内核上实现的,则指令的串行特性必然带来很大的误差;若是这两个参数的读取是在两个内核上实现的,则目前的CPU技术难以实现内核之间ns级别的同步,同样带来统计值的不精确;

FPGA+x86:FPGA内部,通过硬件编程技术,可以很轻松地实现统计值快照功能,严格保证上述两个参数的读取是精确对应的。

系统可扩展性

x86+DPDK+网卡:对于大规模的被测系统,无论是x86的软件实现还是FPGA+X86这样的混合系统,单机都无法完成测试任务,系统级联并且在10ns级别实现同步是必然的选项。x86系统面向通用计算,可以通过运行NTP的协议可以实现多机同步,但是NTP的同步精度无法达到时延测试业务的要求;

FPGA+x86:在FPGA+x86的混合系统中,通过FPGA可以实现本地线缆级联/GPS/1588v2等高精度同步技术,保证时间测试精度。

另外,在FPGA+x86混合系统的实现中,2-3层的流量处理在FPGA内实现,不需要经过CPU的协议栈或者上层应用,CPU只需实现轻量级的配置下发、界面呈现等运算,避免了CPU在线速收发流处理方面的天然缺陷;在X86一侧,也可以灵活部署DPDK技术,由X86系统实现经过加速后的纯协议处理部分,将FPGA和x86的优势组合起来,实现高效的业务处理。

显而易见,采用FPGA+x86混合系统是构建高性能网络测试仪的最佳选择。

- 近年来,国外以太网测试技术发展迅速,新产品层出不穷,高速率高性能测试软硬件平台凭借多年的技术积累,美国的Spirent、keysight两家公司在以太网测试领域长期占据全球主导地位,在本行业内走在世界前列。

- 国内对以太网测试技术的研究始于21世纪初,经过十几年的努力,相关测试产品的自主设计开发能力也取得了长足进步。

网络测试仪采用的是机箱式结构+可插拔板卡的形式,硬件总体方案采用分布式计算架构,在逻辑上分为数据平面和管理平面,在物理单元上将测试模块和主控模块独立设计,使用FPGA+x86混合系统的架构来实现高性能网络测试仪的目标。

![C国演义 [第十二章]](https://img-blog.csdnimg.cn/ef799b9f95114cb197c9eb1e1143b2e6.png)