PCI

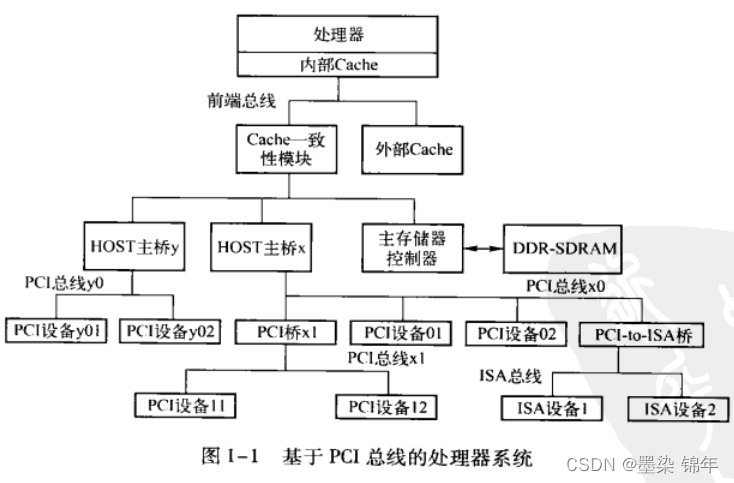

PCI总桥由HOST主桥和PCI桥推出,HOST主桥与主存储器控制器在同一级总线上,因此PCI设备可以方便地通过HOST主桥访问主存储器,即进行DMA操作。

PCI设备的DMA操作需要与处理器系统的Cache进行一致性操作,当PCI设备通过HOST主桥访问主存储器时,Cache一致性模块将进行地址监听,并根据监听的结果改变Cache的状态。因此,设计HOST主桥时需要重点考虑Cache一致性操作。

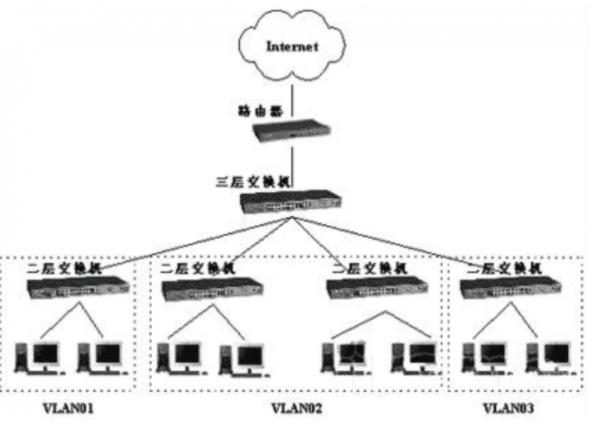

每一个HOST主桥都管理了一棵PCI总线树,在同一棵PCI总线树上的所有PCI设备属于同一个PCI总线域。

PCI总线规定在同一时刻内,在一棵PCI总线树上有且只有一个HOST处理器。

PCI总线树的实际管理者是HOST主桥,而不是HOST处理器。

每一个PCI主设备都具有独立的总线仲裁信号,并与PCI总线仲裁器一一相连。而总线仲裁器需要保证在通过一个时间段内,只有一个PCI设备可以使用当前总线。

PCI桥跨接在两个PCI总线之间,其中距离HOST主桥较近的PCI总线被称为该桥片的上有总线,距离较远的PCI总线被称为该桥片的下游总线。

PCI 中断

处理器的速度跟外围硬件设备的速度往往不在一个数量级上,让硬件在需要的时候再向内核发出信号(变内核主动为硬件主动)。这就是中断机制。

中断随时可以产生。因此,内核随时可能因为新到来的中断而被打断。

同步中断:是当指令执行时由 CPU 控制单元产生,之所以称为同步,是因为只有在一条指令执行完毕后 CPU 才会发出中断,而不是发生在代码指令执行期间,比如系统调用。

异步中断:是指由其他硬件设备依照 CPU 时钟信号随机产生,即意味着中断能够在指令之间发生,例如键盘中断。

handle_irq:上层的通用中断处理函数指针,如果未设置则默认为__do_IRQ()。通常针对电平触发或者边沿触发有不同的处理函数。每个中断线可分别设置;

Delay传送方式处理Non-Posted总线事务

![[Java]重写equals为什么要重写hashcode???配合HashMap源码一起理解](https://img-blog.csdnimg.cn/42c749145e29456a8bdca0a824cb01ea.png)