标题:A Low-Loss Diode Integrated SiC Trench MOSFET for Improving Switching Performance

阅读日期:2023.7.17

研究了什么

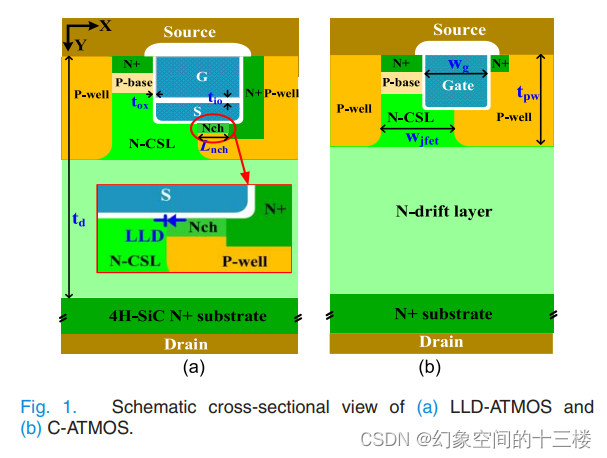

该研究提出并通过数值模拟对一种集成低损耗二极管(LLD-ATMOS)的硅碳化物(SiC)非对称沟槽MOSFET进行了研究,以减小开关损耗并消除体二极管的双极性退化。虚拟栅极下方的N沟槽区提供了从N漂移层到N+源区输送电子的低势垒通路,从而将正向导通电压降从10A的pn体二极管的3.5V降低到10A的LLD-ATMOS的1.9V。此外,LLD的反向恢复电荷(QRR)和LLD-ATMOS的栅-漏电容(Cgd)分别比传统的非对称沟槽MOSFET(C-ATMOS)低76%和95%。因此,LLD-ATMOS的关断和开启损耗分别降低了49%和58%。计算得到的LLD-ATMOS的高频优化指标(HF-FOM = RON,sp × Cgd)显著降低到C-ATMOS的1/14。此外,还开发了LLD的导带能量分析模型。改进的性能表明,LLD-ATMOS是电力电子系统中具有竞争力的选项。

文章创新点

虚设栅极下方的N沟道区域提供了一个低势垒路径,将电子从N漂移层传输到N+源极区域。多晶硅栅极分为两部分。顶部的是真栅极,而底部的是源极连接的伪栅极。应用电流扩展层(CSL)来减少JFET效应。

文章的研究方法

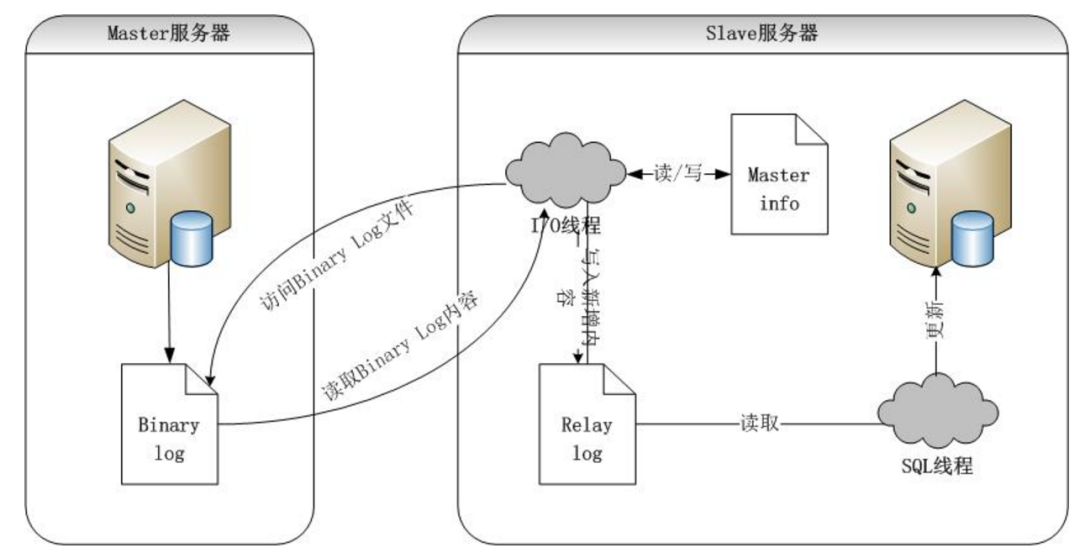

对比分析LLD-ATMOS和C-ATMOS的正向和第三象限传导特性图。仿真分析LLD-ATMOS和C-ATMOS在15和−5V的栅极-源极电压(VGS)下的正向和第三象限电感性能。

仿真分析LLD-ATMOS和C-ATMOS中二极管的反向恢复特性,并给出了双脉冲测试电路。

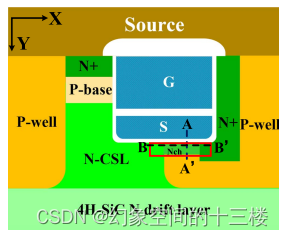

给出了NCSL、Nch和N+区域之间的三维导带能量分布.

沿A–A’切割线的导带能量分布,沿着B–B’切割线的导带能量分布。

不同VSD值下沿B–B’切割线的导带能量分布.

VGS=−5V时LLD-ATMOS的势垒与tnch和Nnch的关系。

LLD-ATMOS和C-ATMOS的器件电容。

LLD-ATMOS和C-ATMOS的栅极电荷特性。

LLD-ATMOS和C-ATMOS的开关特性。(a)关闭过程和(b)打开过程。

LLD-ATMOS和C-ATMOS的阻断特性。

LLD-ATMOS和C-ATMOS的空穴密度分布。

tnch和Nnch对LLD-ATMOS击穿电压的影响。

tox对LLD势垒高度的影响。

Lnch对LLD-ATMOS的势垒高度和击穿电压的影响,以及不同Lnch值的LLD沿B–B’切割线的导带能量分布。

(a)C-ATMOS和(b)LLD-ATMOS在不同VGS值下的第三象限特性。

LLD-ATMOS的简要制造工艺流程。(a) N-CSL和P阱的外延生长和N+源注入。(b) 沟槽蚀刻。(c) Nch区域注入。(d) P-base和N+源极区注入。(e) 多晶硅沉积和蚀刻形成虚设栅极。(f) 隔离氧化物沉积和蚀刻。(g) 栅极氧化。(h) 多晶硅蚀刻。(i) 金属化。

文章得出的结论

提出了一种新型的嵌入LLD的SiC不对称沟槽MOSFET,并用Sentaurus TCAD进行了仿真。还使用导带能量分析模型来理解LLD的操作机制。仿真结果表明,LLD比pn体二极管具有更低的VON和更好的反向恢复性能。因此,消除了双极性退化,并且导通损耗从C-ATMOS的5.5mJ/cm2降低到LLD-ATMOS的2.3mJ/cm2。同时,在保持其他性能几乎不变的情况下,LLD-ATMOS显著提高了HF-FOM(RON,sp×CGD和RON,sp×Qgd)。上述优点使得所提出的LLD-ATMOS能够成为电力电子应用的有力竞争对手。

![[QT编程系列-21]:基本框架 - QT常见数据结构:QString、QList、QVector、QMap、QHash、QSet、QPair详解](https://img-blog.csdnimg.cn/7b9dd2406f8541d1b97fa89e68f1d143.png)