Verdi平台包括最先进的结构可视化和分析工具,其中,nTrace用于源代码,nWave用于波形,nSchema用于原理图/逻辑图,nState用于有限状态机(FSM)。本节将对nState的使用进行介绍。

为了简单起见,我们以一个序列检测器为例,介绍nState的使用过程。

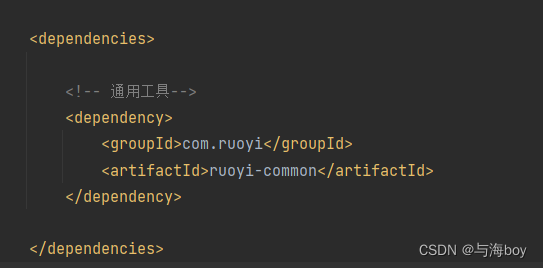

设计代码:

module top(

input logic clk,

input logic rst,

input logic bit_in,

output logic detect

);

//detect seq:1101

parameter S0=0;

parameter S1=1;

parameter S11=2;

parameter S110=3;

parameter S1101=4;

//

logic [2:0] cs;

logic [2:0] ns;

//

always@(posedge clk,posedge rst)

if(rst)

cs<=S0;

else

cs<=ns;

//

always@(*)

case(cs)

S0:ns=(bit_in)?S1:S0;

S1:ns=(bit_in)?S11:S0;

S11:ns=(bit_in)?S11:S110;

S110:ns=(bit_in)?S1101:S0;

S1101:ns=(bit_in)?S11:S0;

default:ns=S0;

endcase

//

always@(posedge clk,posedge rst)

if(rst)

detect<=0;

else if(cs==S110&&bit_in==1)

detect<=1;

else

detect<=0;

endmodule

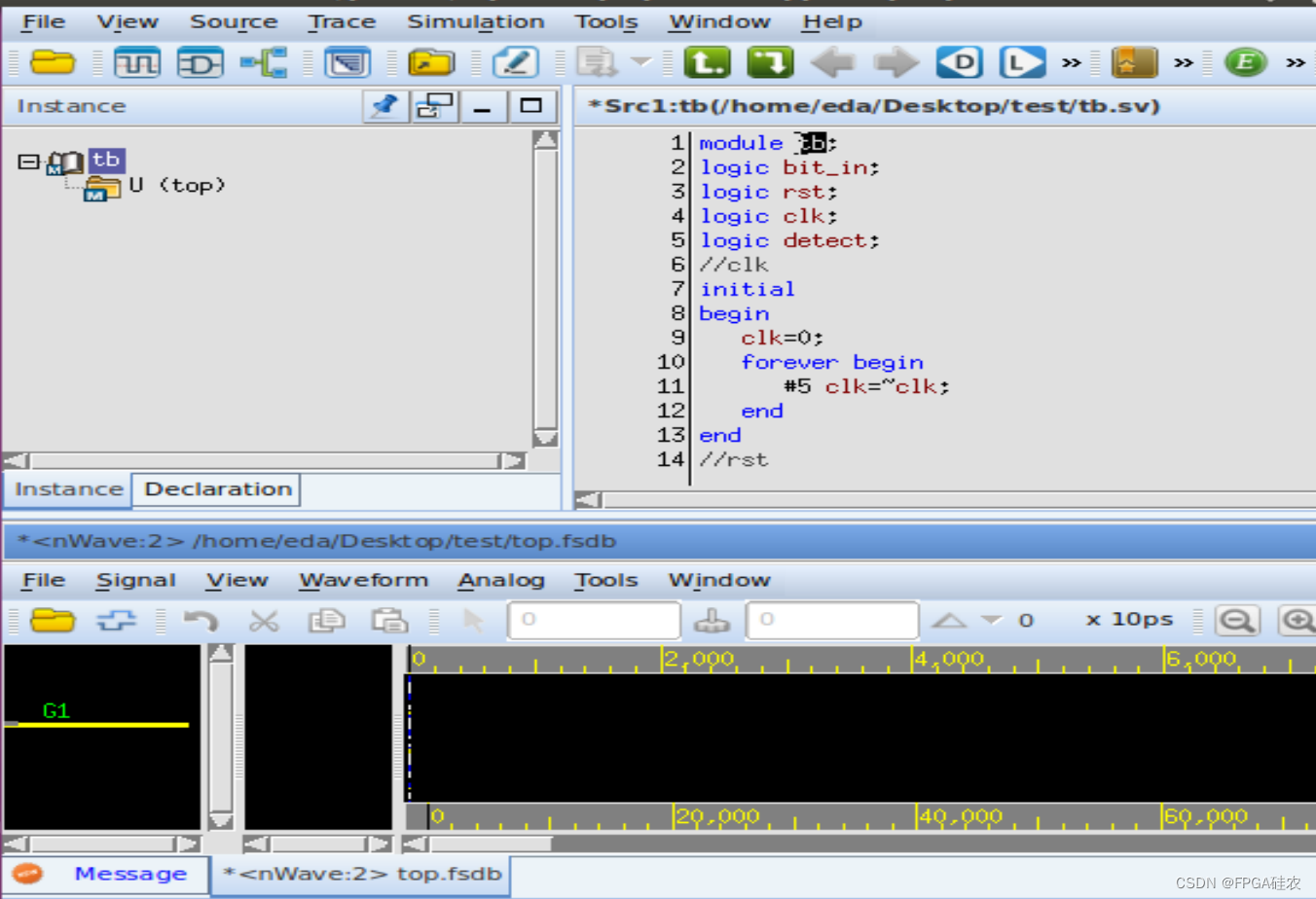

测试平台(未对正确性作验证):

module tb;

logic bit_in;

logic rst;

logic clk;

logic detect;

//clk

initial

begin

clk=0;

forever begin

#5 clk=~clk;

end

end

//rst

initial

begin

rst=1;

#100

rst=0;

end

//

always@(posedge clk,posedge rst)

if(rst)

bit_in<=0;

else

bit_in<={$random%2};

//

initial

begin

#1000

$finish;

end

//

initial begin

$fsdbDumpfile("./top.fsdb");

$fsdbDumpvars(0);

end

//inst

top U(.*);

endmodule

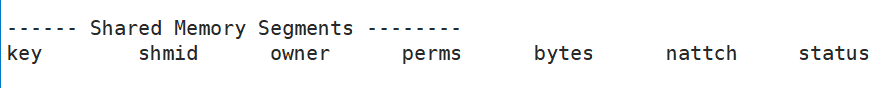

makefile脚本:

all: listfile com sim verdi clean

listfile:

find -name "*.sv" > filelist.f

com:

vcs -full64 -cpp g++-4.8 -cc gcc-4.8 -LDFLAGS -Wl,--no-as-needed -sverilog -debug_access -timescale=1ns/10ps \

-f filelist.f -l com.log -kdb -lca

sim:

./simv -l sim.log

verdi:

verdi -sv -f filelist.f -ssf *.fsdb -nologo &

clean:

rm -rf csrc *.log *.key *simv* *.vpd *DVE*

rm -rf verdiLog *.fsdb *.bak *.conf *.rc *.f

依次输入make listfile, make com, make sim, 然后输入make verdi。(或者直接输入make listfile ; make com ; make sim ; make verdi)得到:

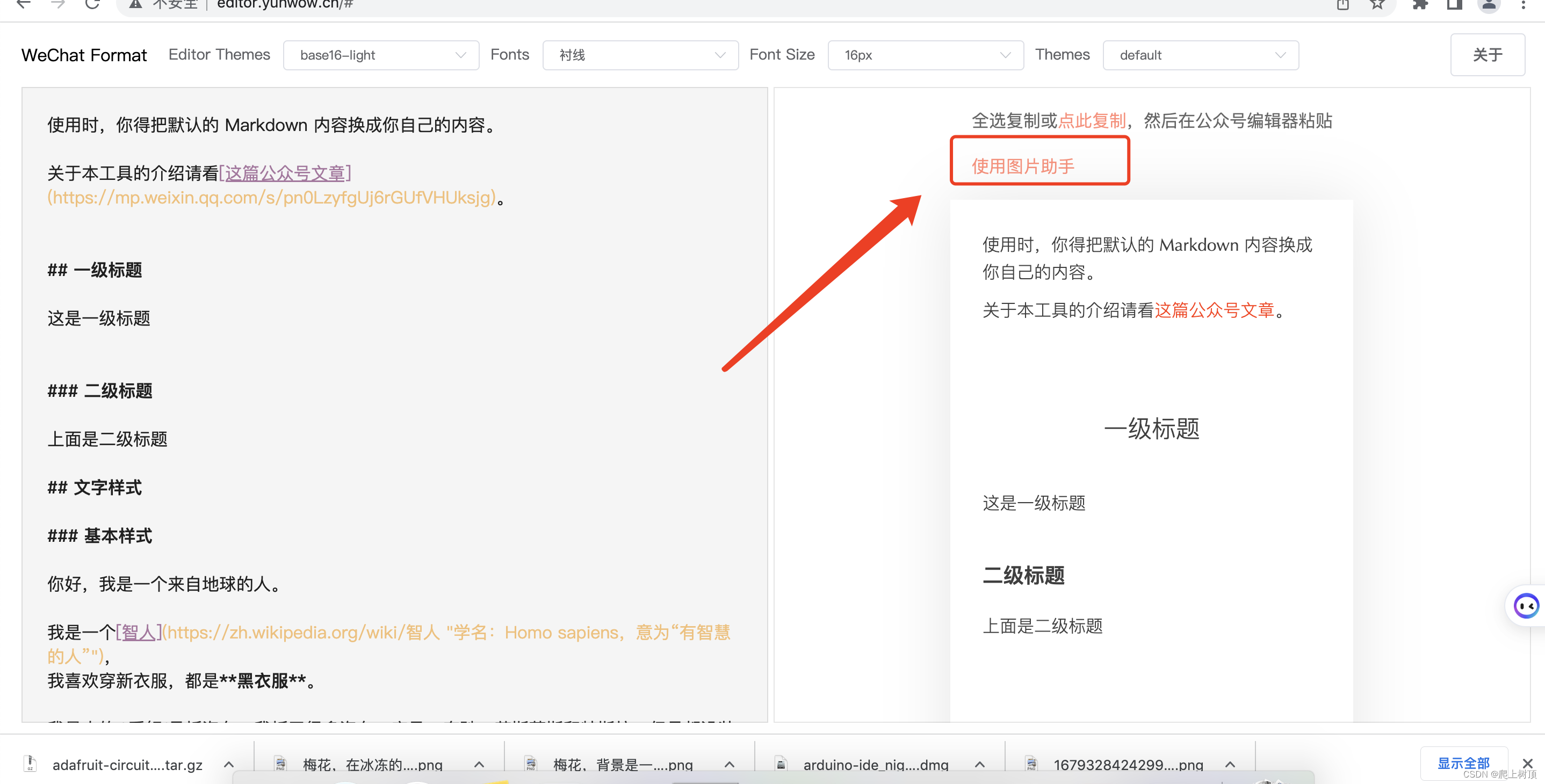

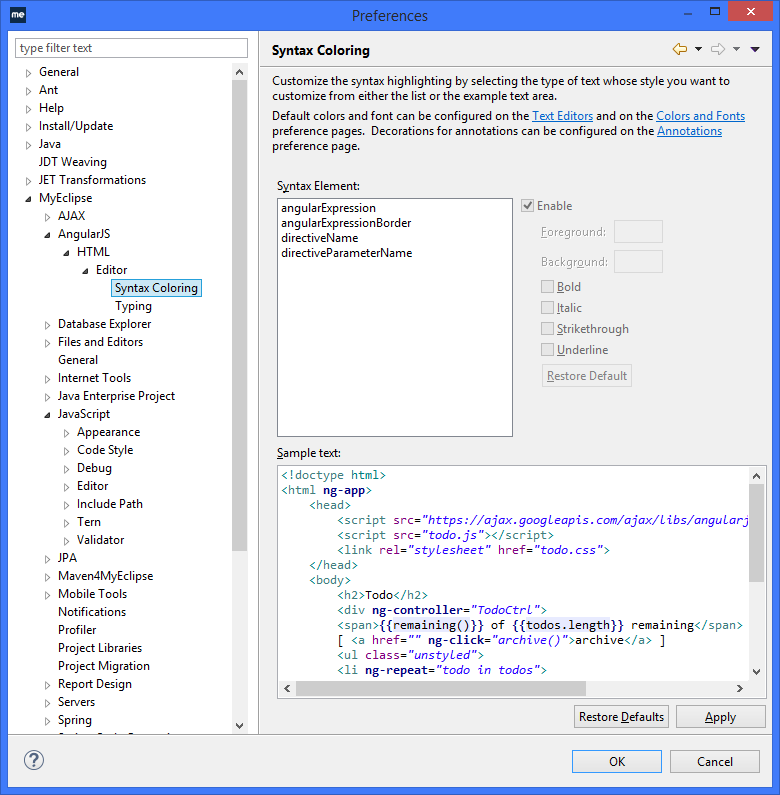

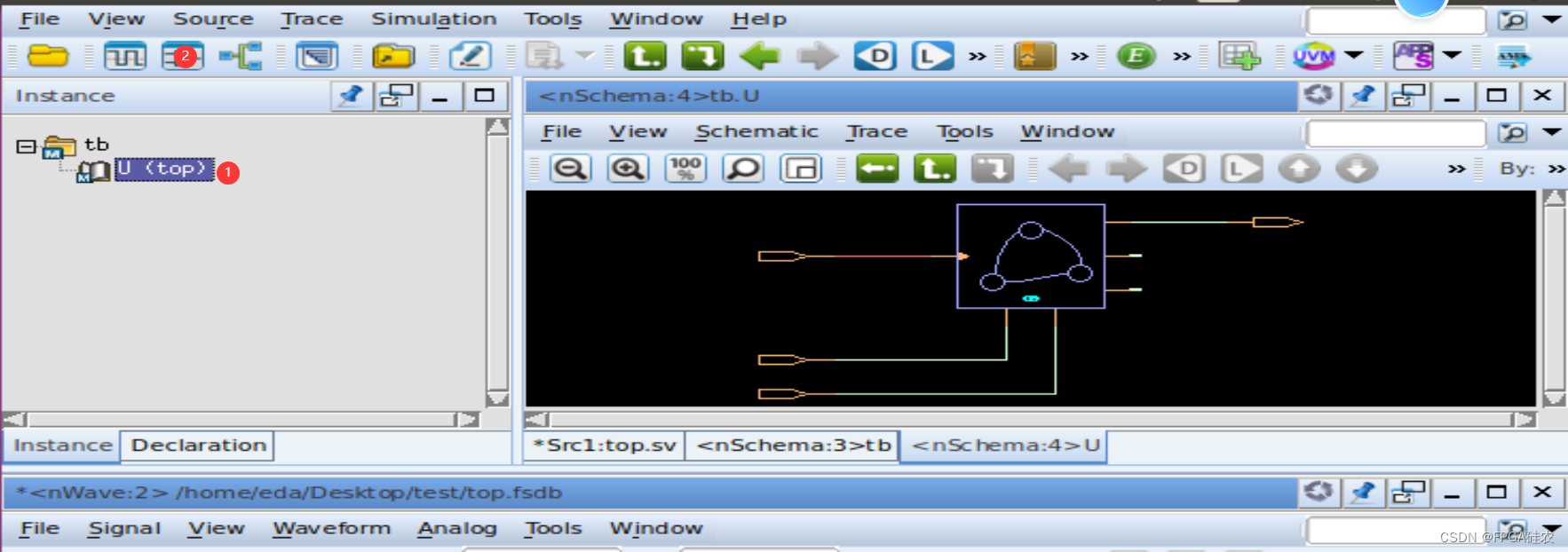

选中U(top),即1,然后点击2,得到:

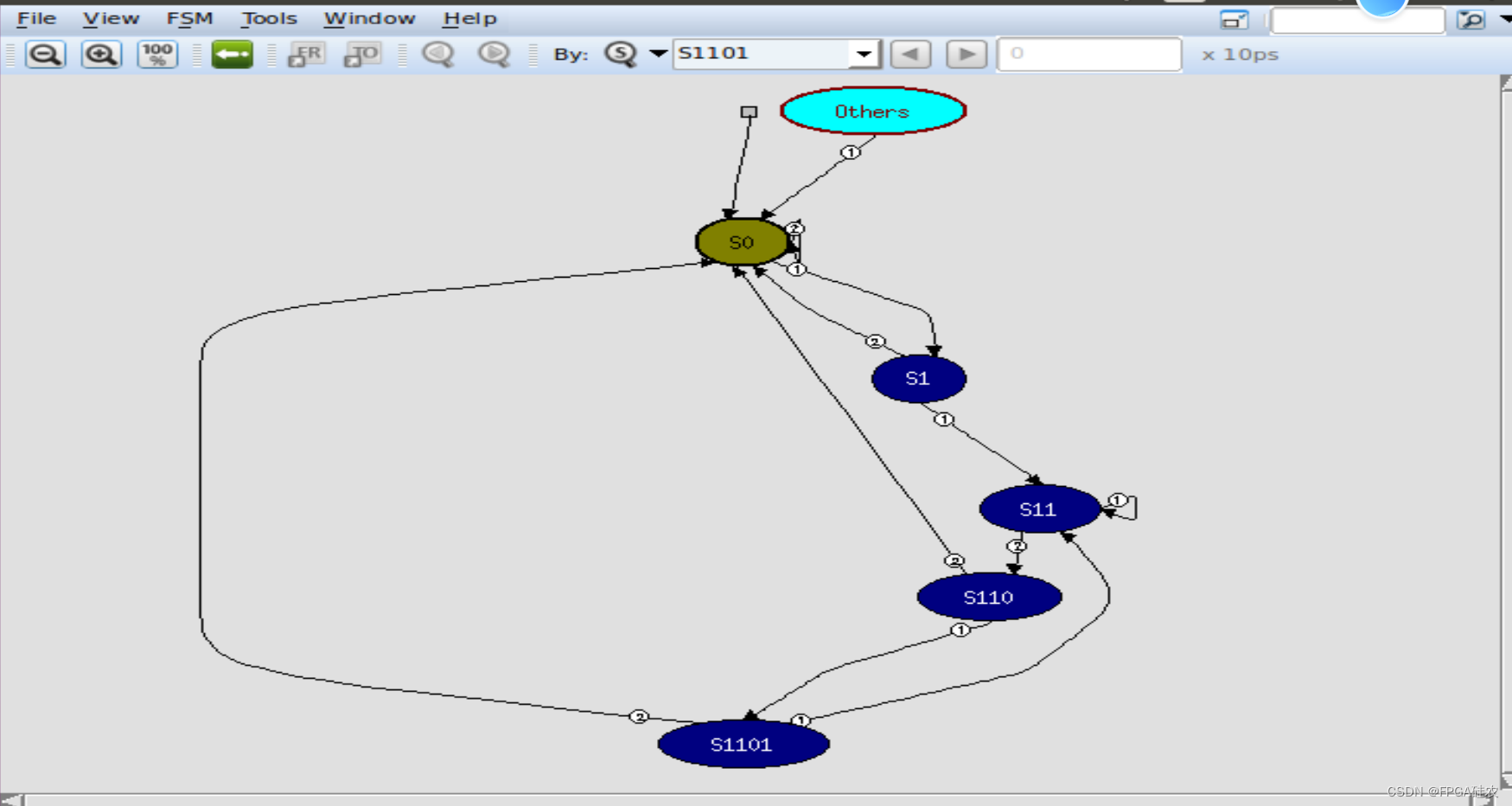

双击nSchema方框中的状态机,得到

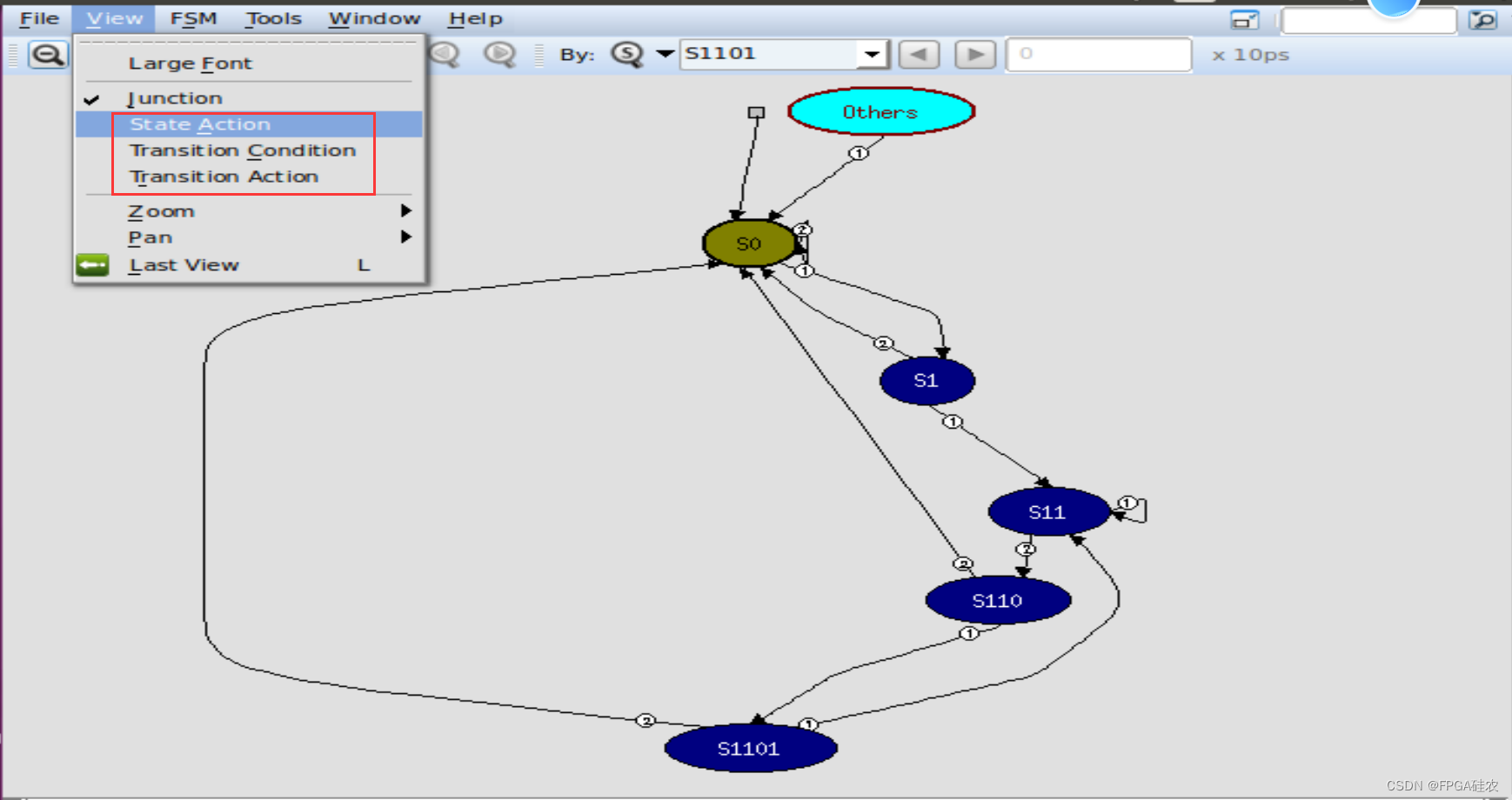

点击View,勾选下图所示的三项:

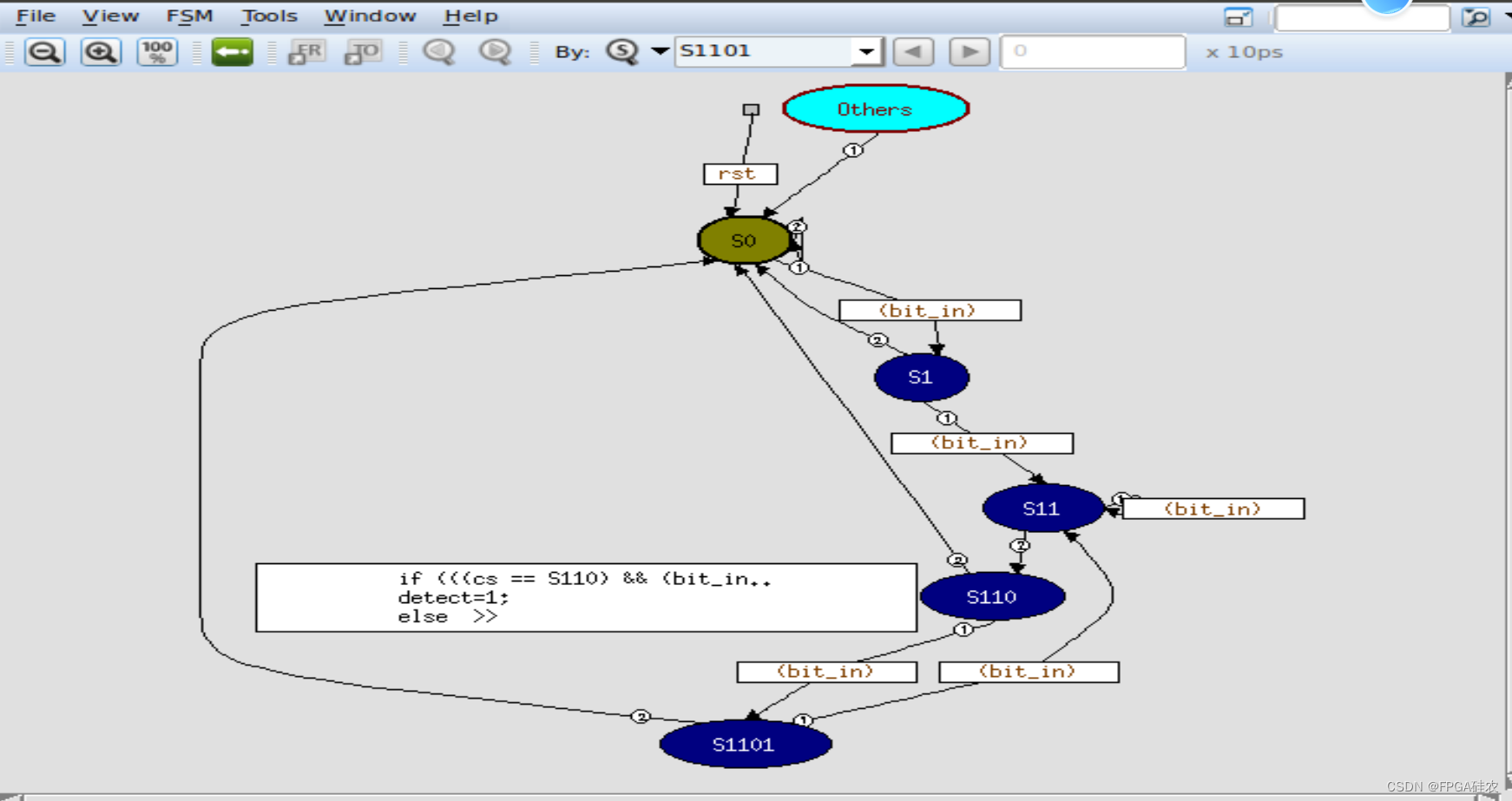

此时,会显示所勾选的三项的相关信息,如下图所示。

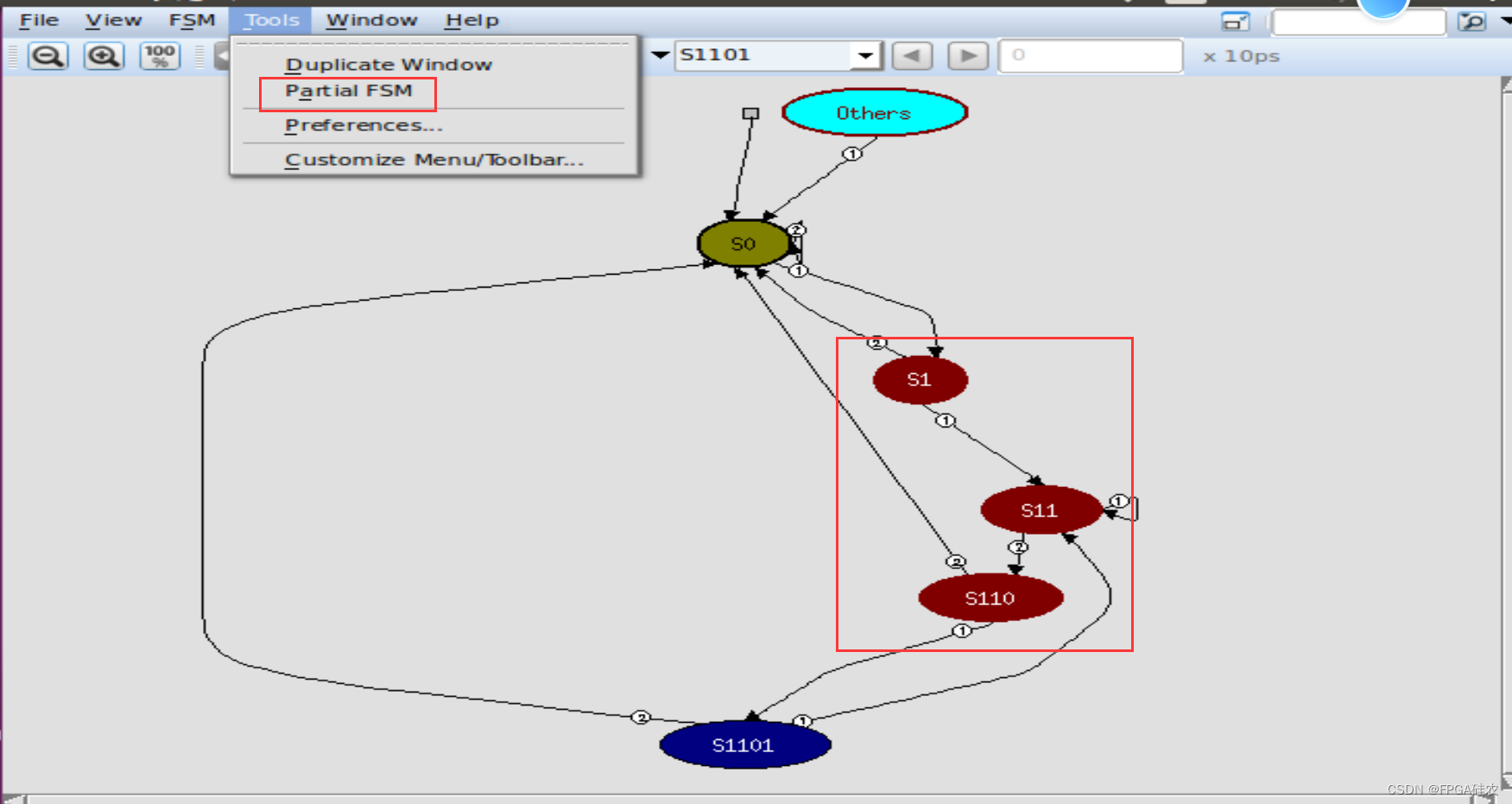

按住shift,选中S1, S11和S110三个状态,然后点击Tools–>Partial FSM。

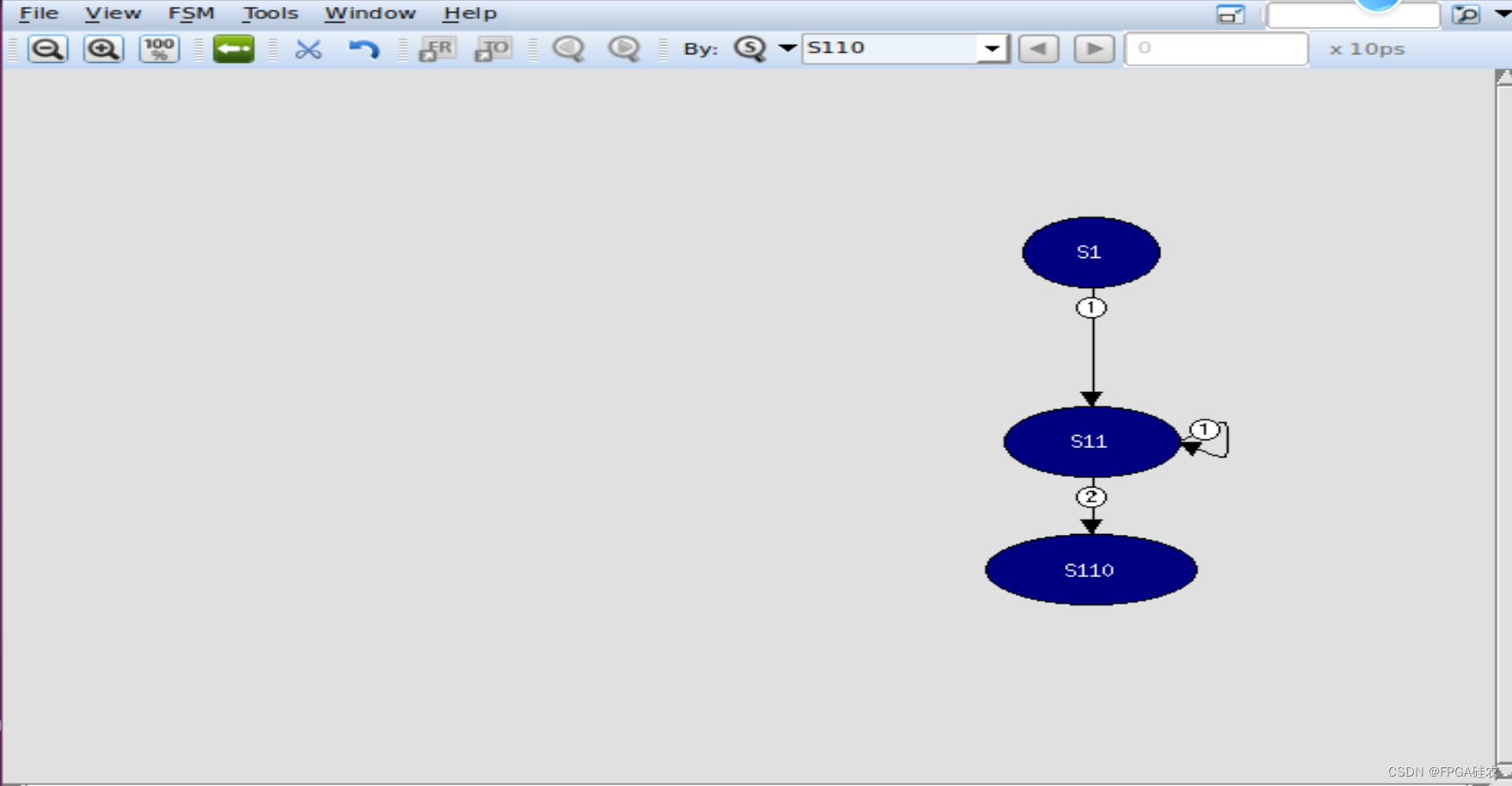

可以得到由这三个状态所组成的部分状态机:

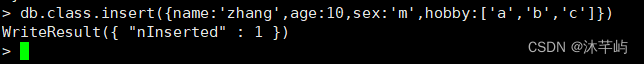

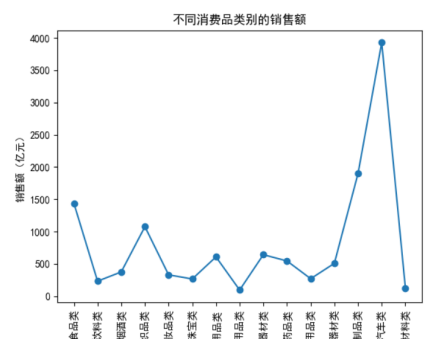

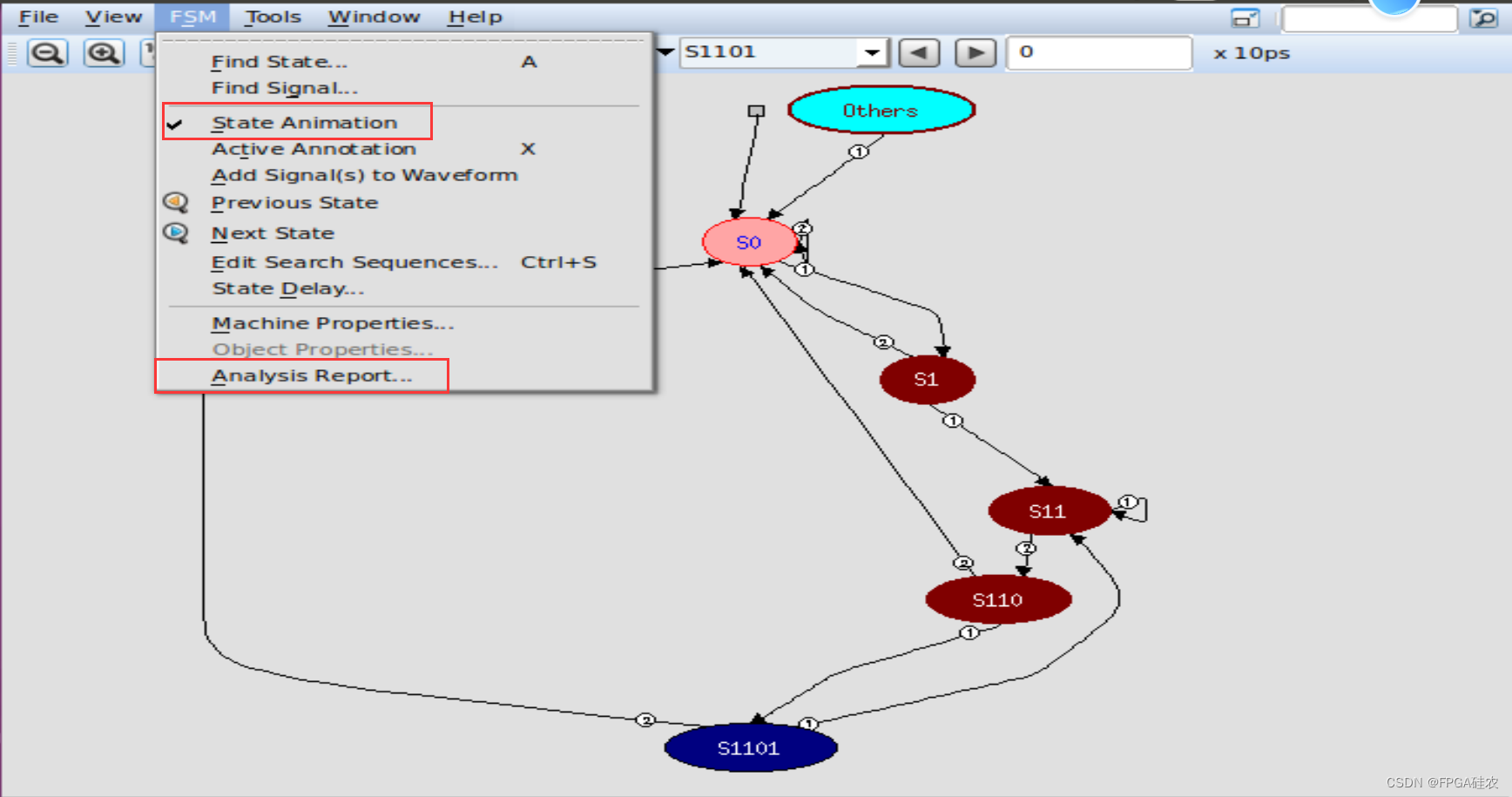

最后,点击FSM,选中State Animation,然后点击Analysis Report…。

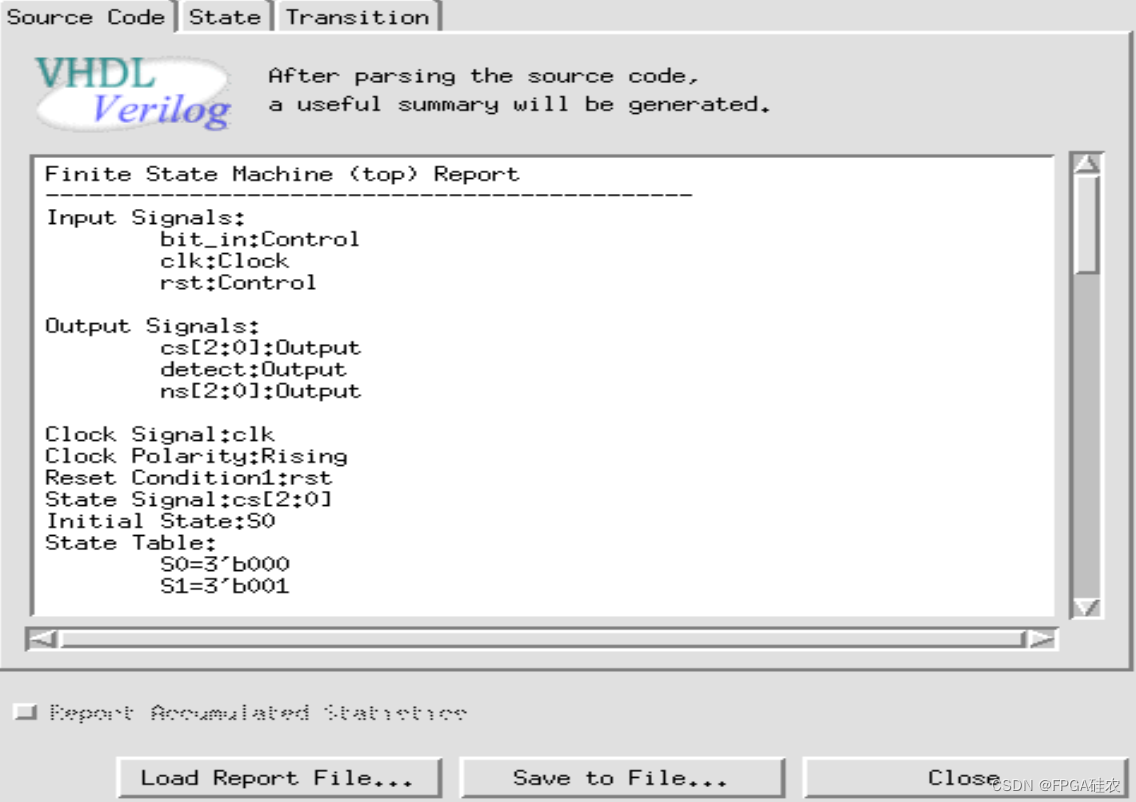

状态机报告如下图所示:

该图给出了状态机的整体信息,包括输入、输出信号,时钟信号的名称及其极性,复位条件以及状态信号、初始状态和状态表。等等。

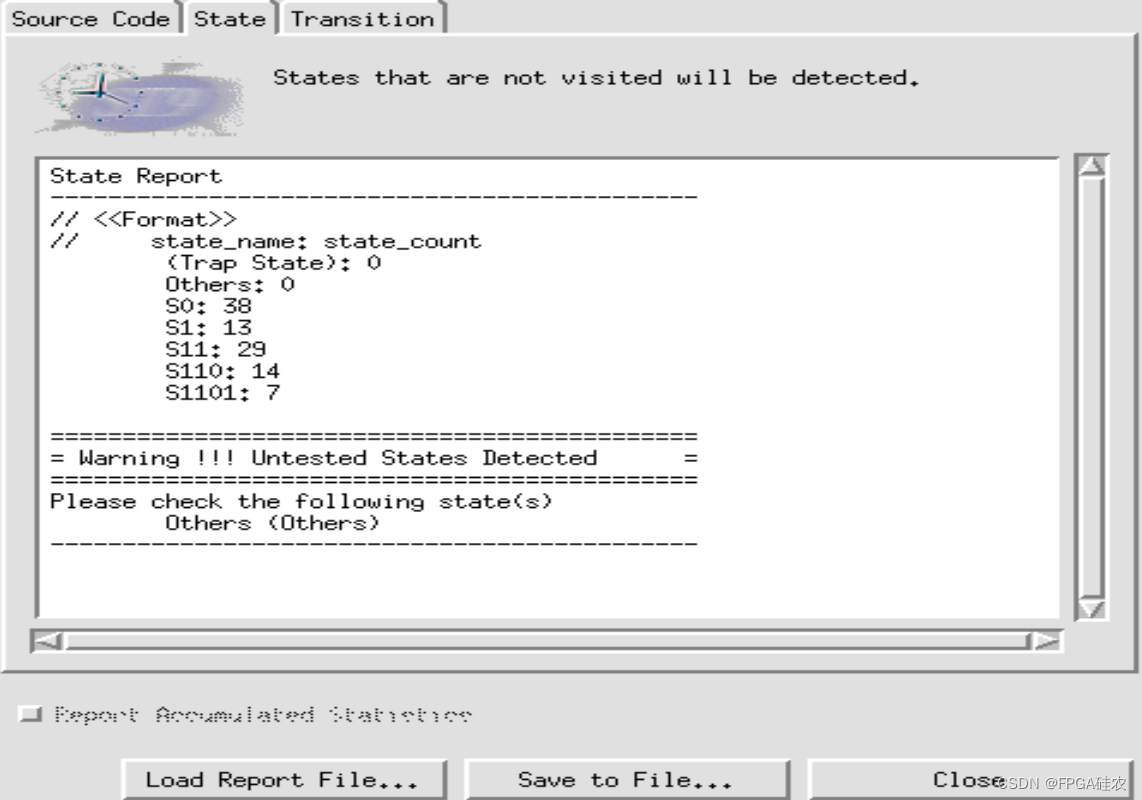

State栏则给出了每一个状态在仿真中出现的次数。同时会警告从未出现过的状态。

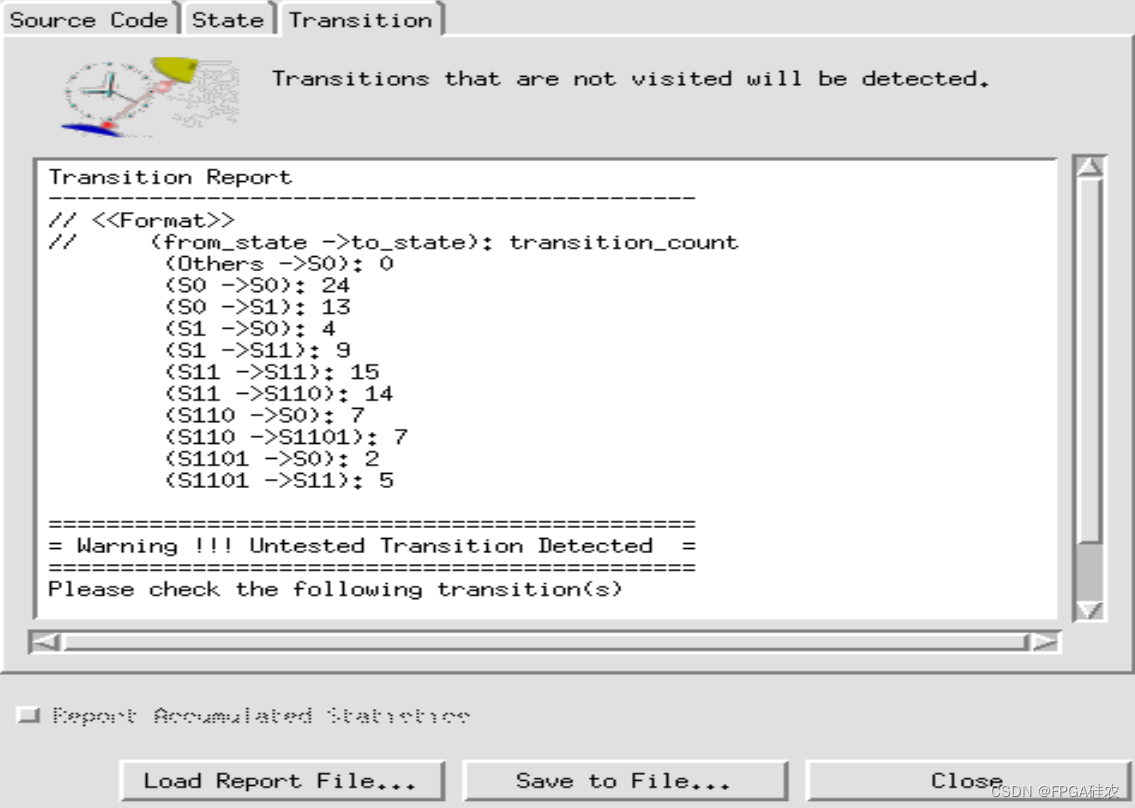

Transition栏则给出了每一种状态跳转情况出现的次数。