第三章系统控制

目录

第三章系统控制

3.1关于系统控制

3.2寄存器汇总

3.3寄存器描述

3.3.1辅助控制寄存器

3.3.2cpu基寄存器

3.3.3 Cache Level ID寄存器

3.3.4缓存大小ID寄存器

3.3.5缓存大小选择寄存器

3.3.6指令和数据紧密耦合的存储器控制寄存器

3.3.7 AHBP控制寄存器

3.3.8 L1缓存控制寄存器

3.3.9辅助母线故障状态登记

3.3.10指令错误库寄存器0-1

3.3.11数据错误银行寄存器0-1

3.3.12 AHB从控制寄存器

本章描述了对处理器进行编程的寄存器。它包含以下部分:

关于系统控制,见第3-2页。

注册摘要在3-3页。

注册3-6页的描述。

3.1关于系统控制

本章描述控制处理器操作的寄存器。这包括:

- 系统控制空间。

- 访问控制空间。

- 识别空间。

- 缓存维护空间。

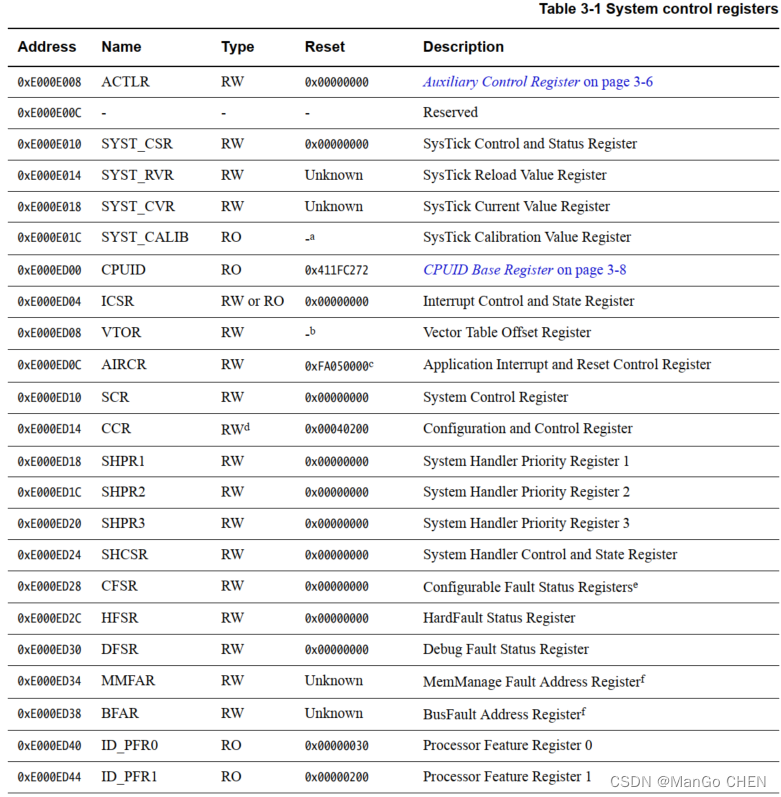

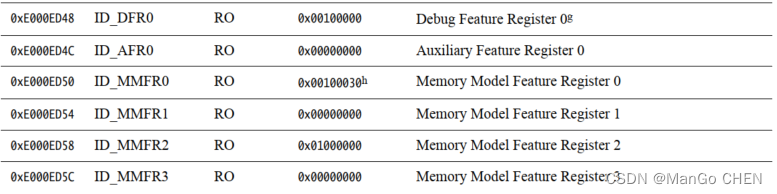

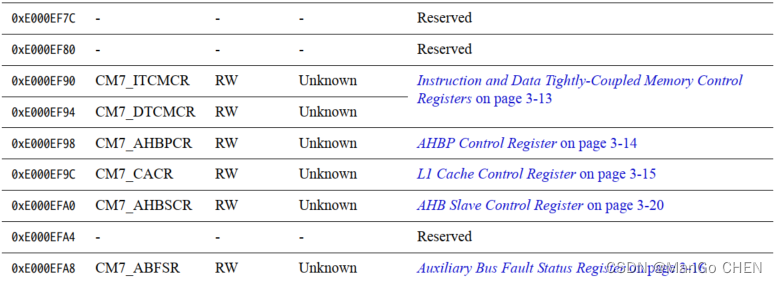

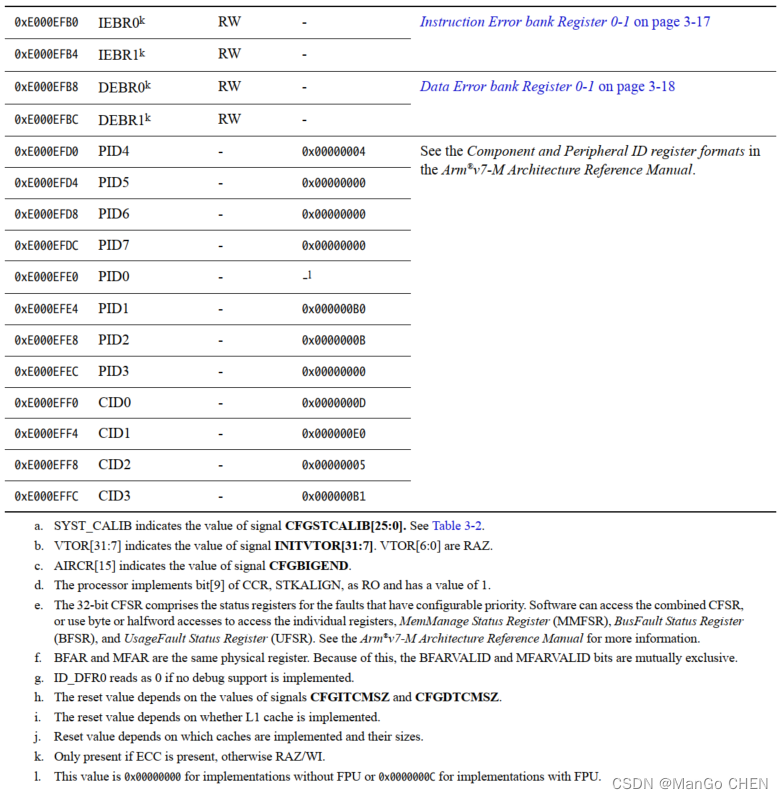

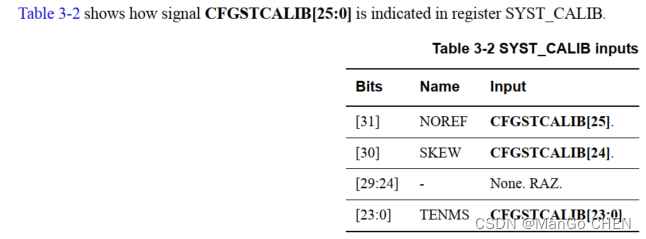

3.2寄存器汇总

系统控制寄存器如表3-1所示。本章没有描述的寄存器在Arm*v7-M架构参考手册中有描述。

3.3寄存器描述

本节描述下列系统控制寄存器,其实现特定于此处理器

- 辅助控制寄存器。

- CPUID Base Register见第3-8页。

- Cache Level ID Register在3-9页。

- Cache Size ID Register在3-10页。

- 缓存大小选择寄存器在第3-12页。

- 第3-13页的指令和数据紧密耦合内存控制寄存器。

- AHBP控制登记册3-14页。

- 第3-15页的Ll缓存控制寄存器。

- 辅助总线故障状态寄存器见第3-16页。

- 指令错误银行3-17页的0-1寄存器。

- 数据错误银行3-18页0-1寄存器。

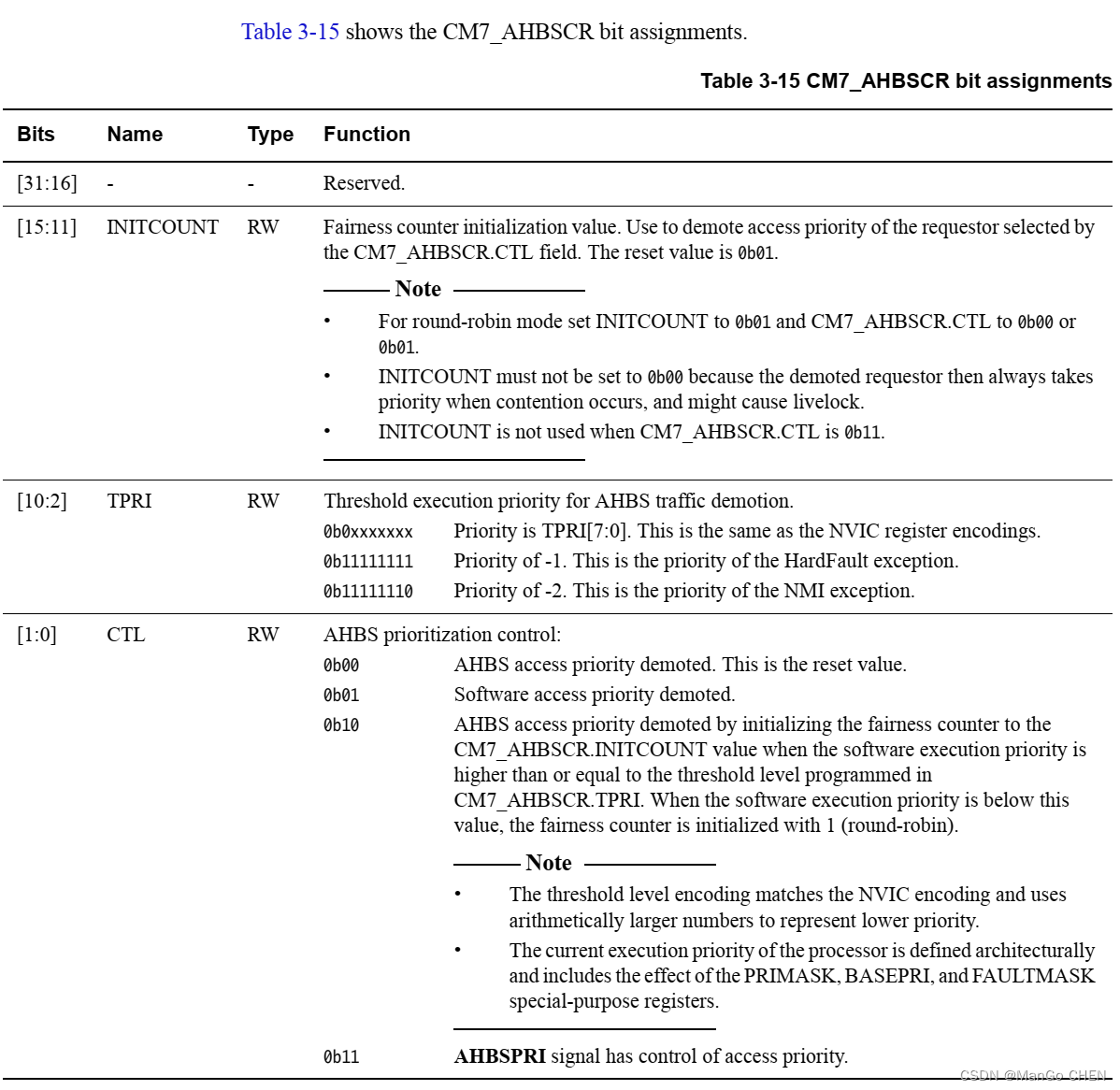

- AHB从控制寄存器在第3-20页。

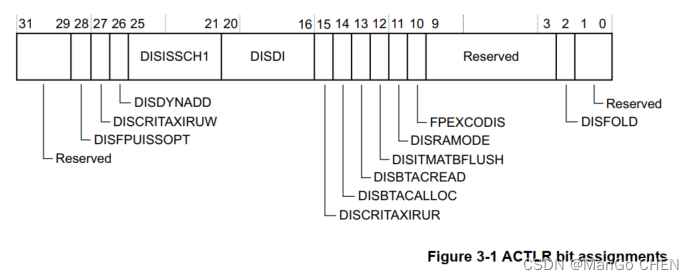

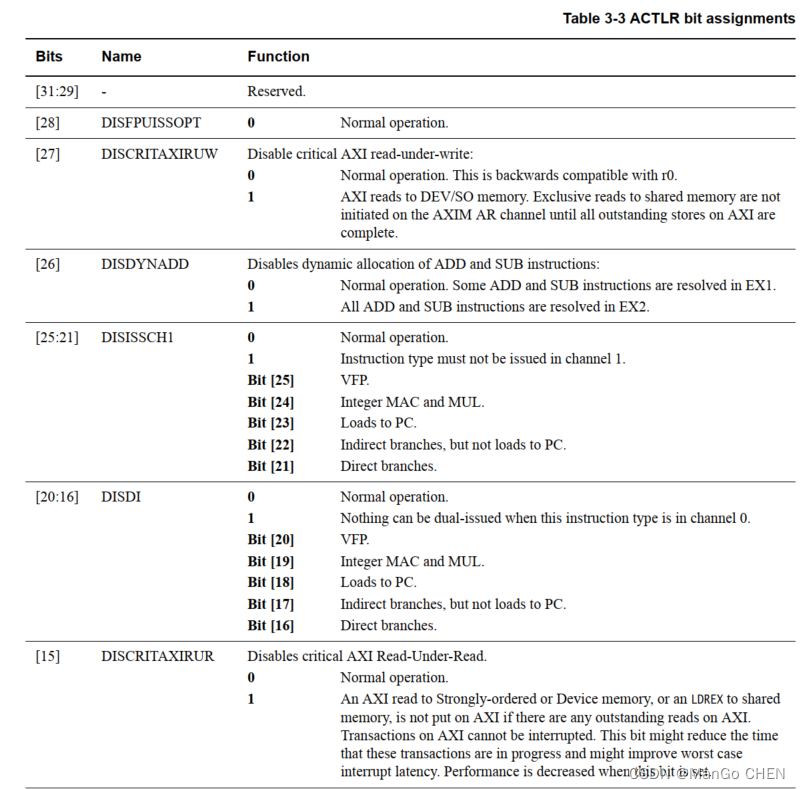

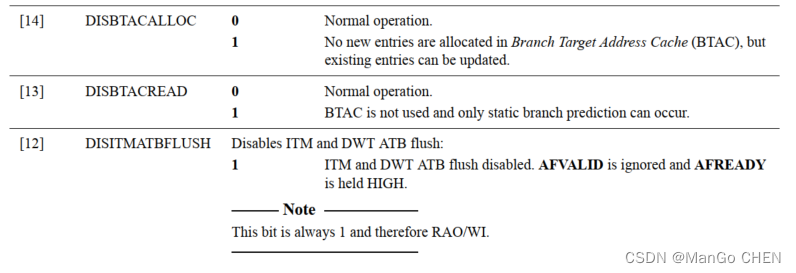

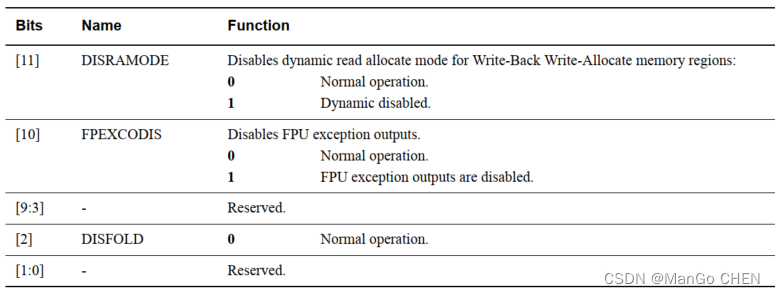

3.3.1辅助控制寄存器

ACTLR的特点是:

目的:为处理器提供实现定义的配置和控制选项。

使用约束:没有使用约束。

配置:可用于所有配置。

属性:请参见第3-3页表3-1中的寄存器汇总。

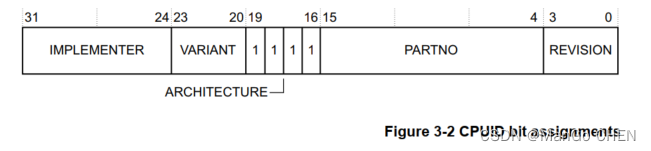

3.3.2cpu基寄存器

CPUID的特性如下:

目的指定:

处理器核心的ID号。

处理器核心的版本号。

处理器核心的实现细节。

使用约束没有使用约束:

配置属性可用于所有配置。

请参见第3-3页表3-1中的寄存器汇总。

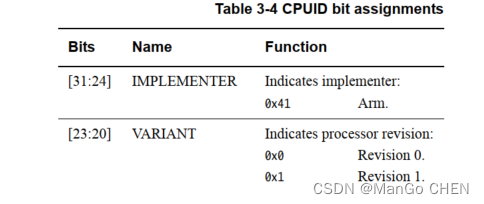

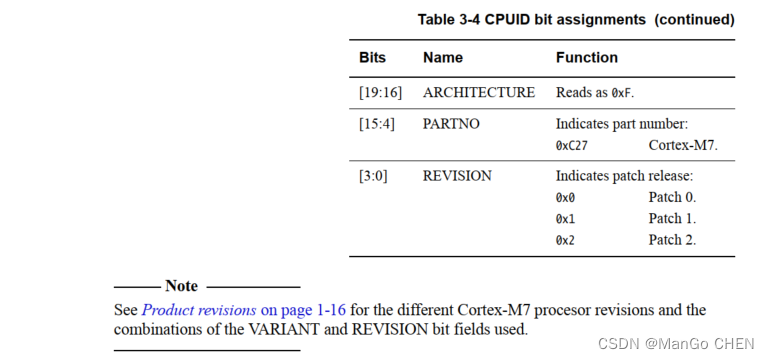

CPUID的位分配如图3-2所示。

CPUID的位分配如表3-4所示。

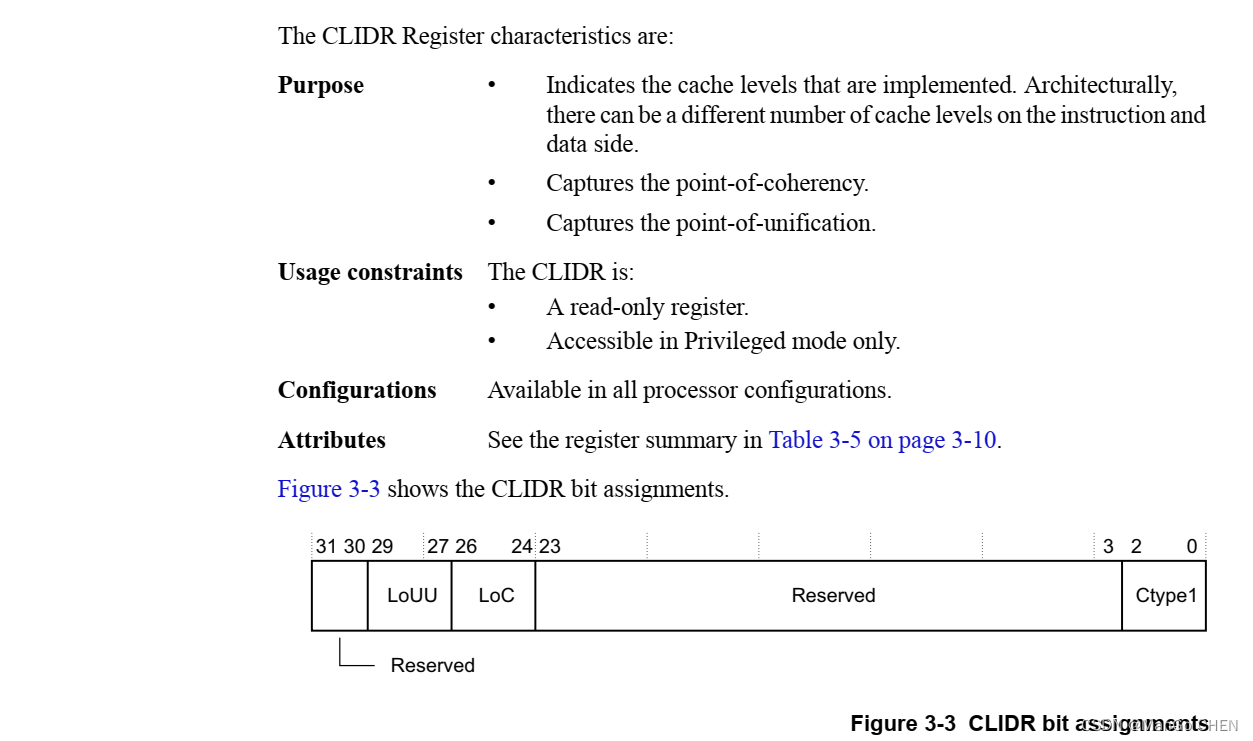

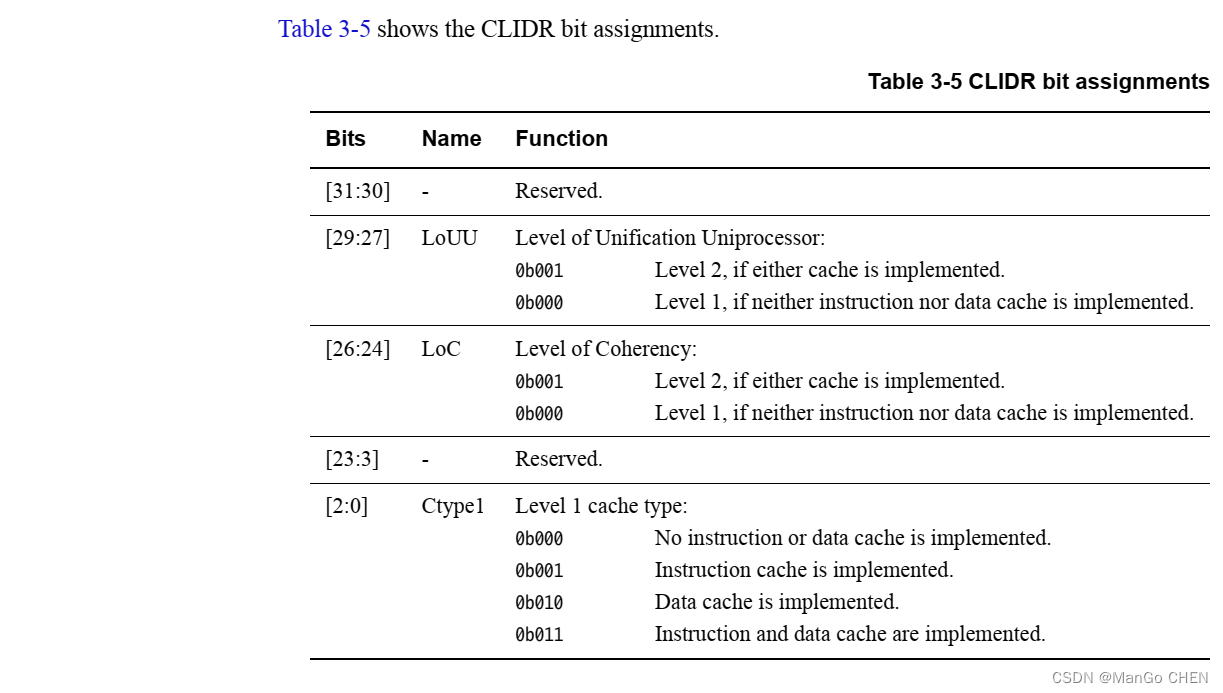

3.3.3 Cache Level ID寄存器

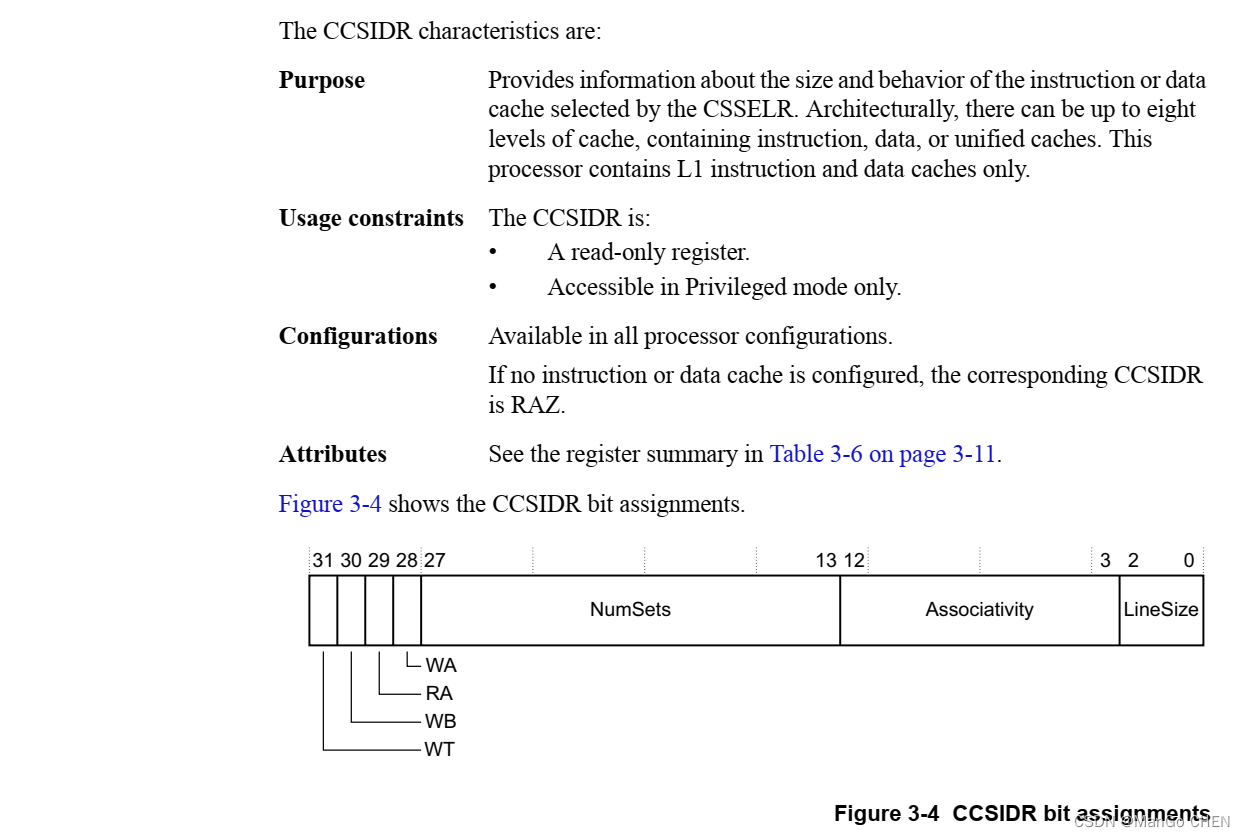

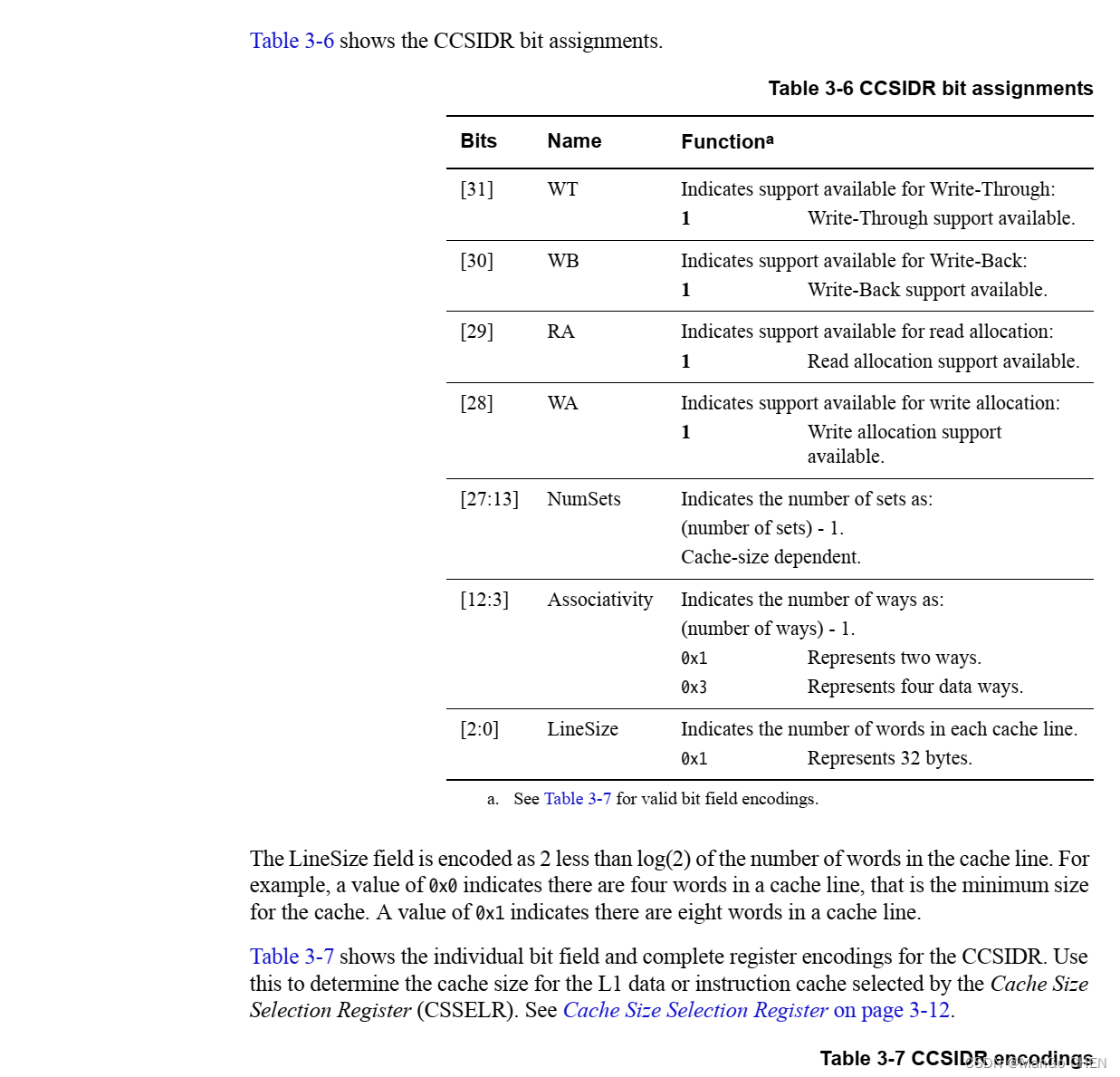

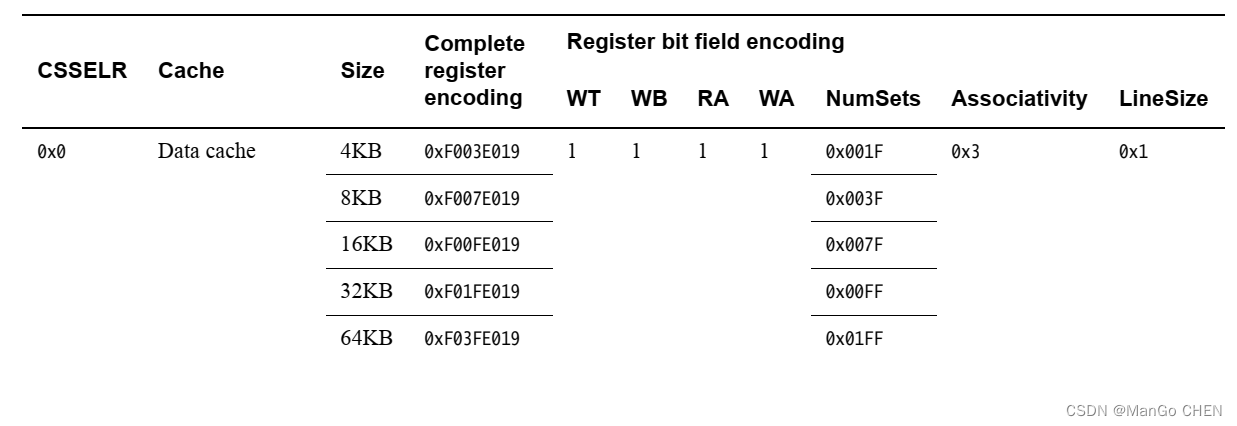

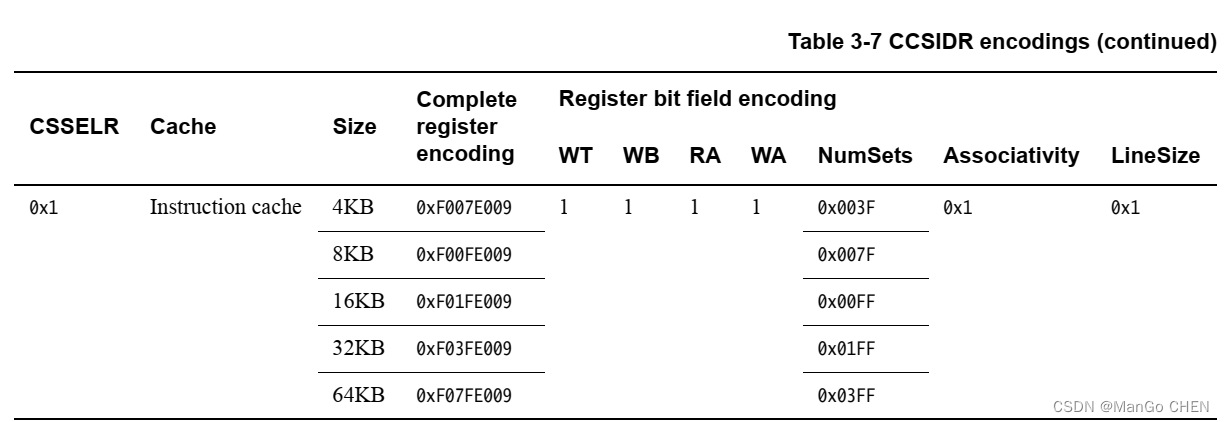

3.3.4缓存大小ID寄存器

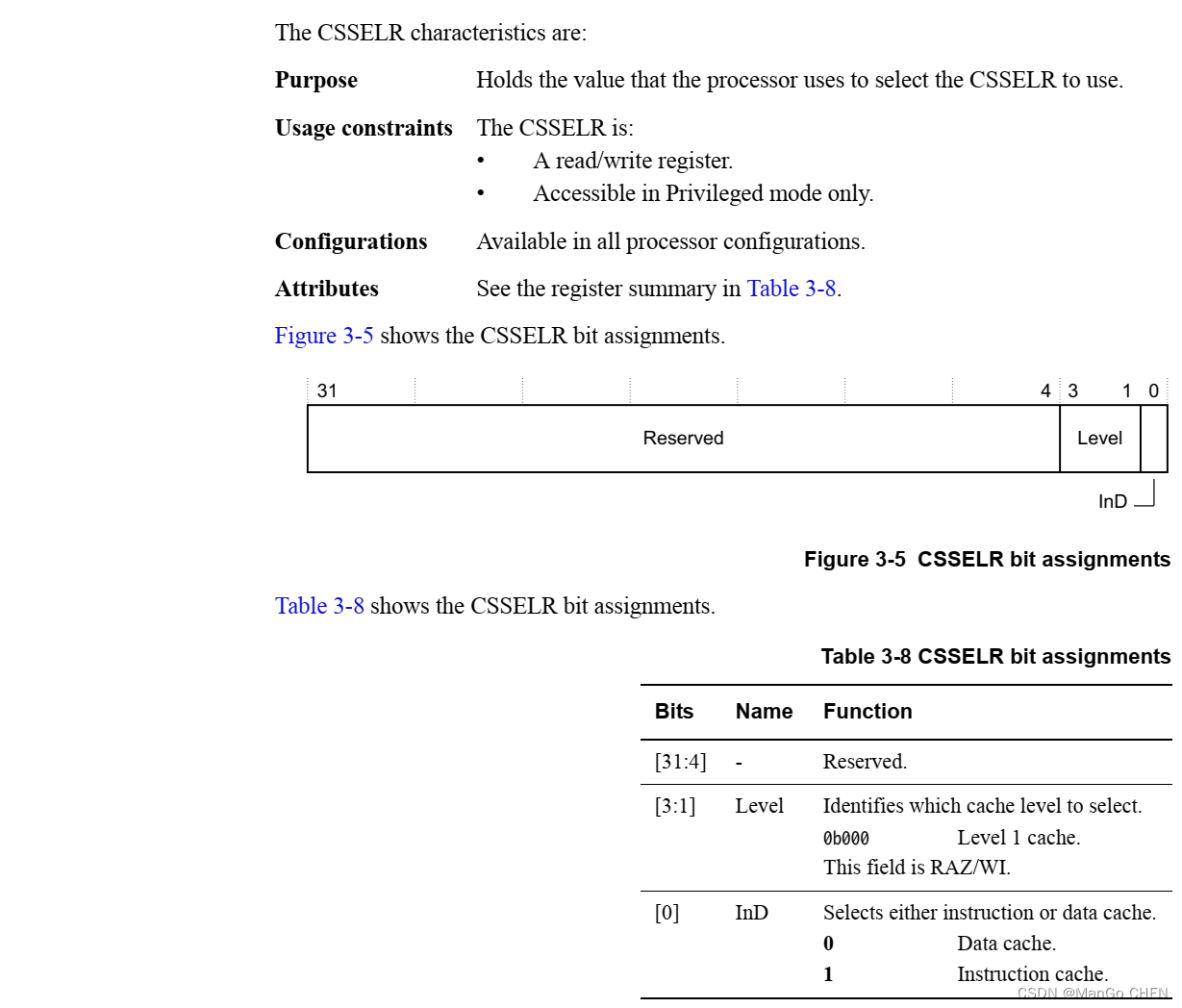

3.3.5缓存大小选择寄存器

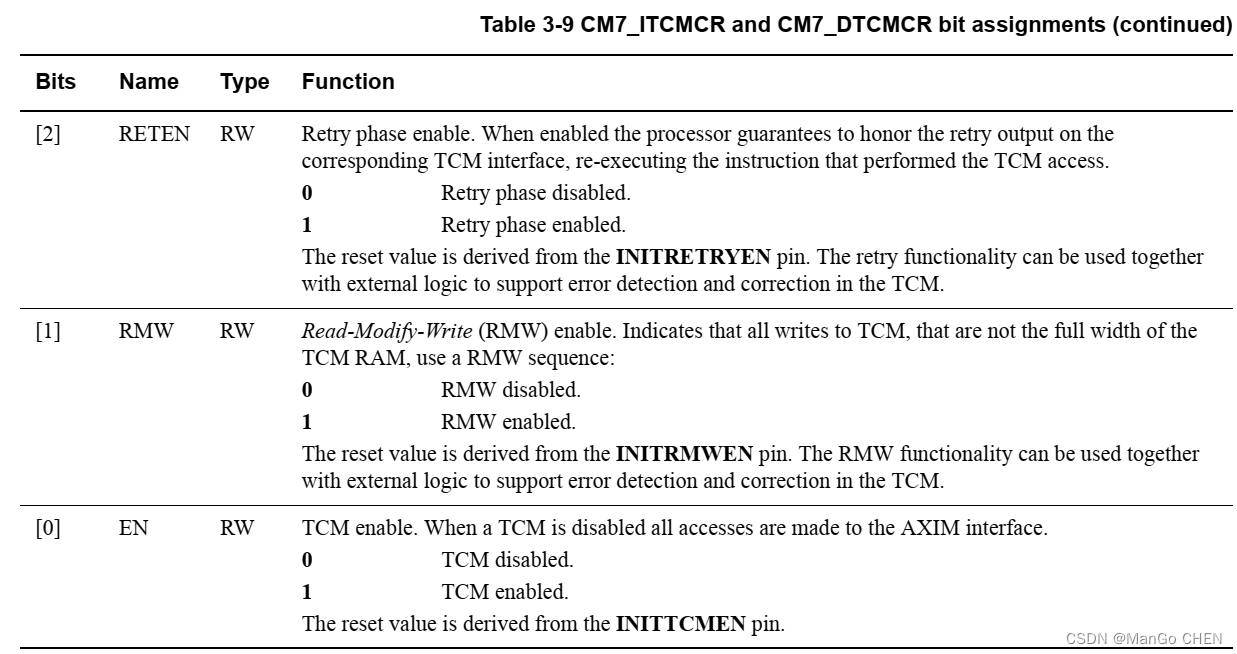

3.3.6指令和数据紧密耦合的存储器控制寄存器

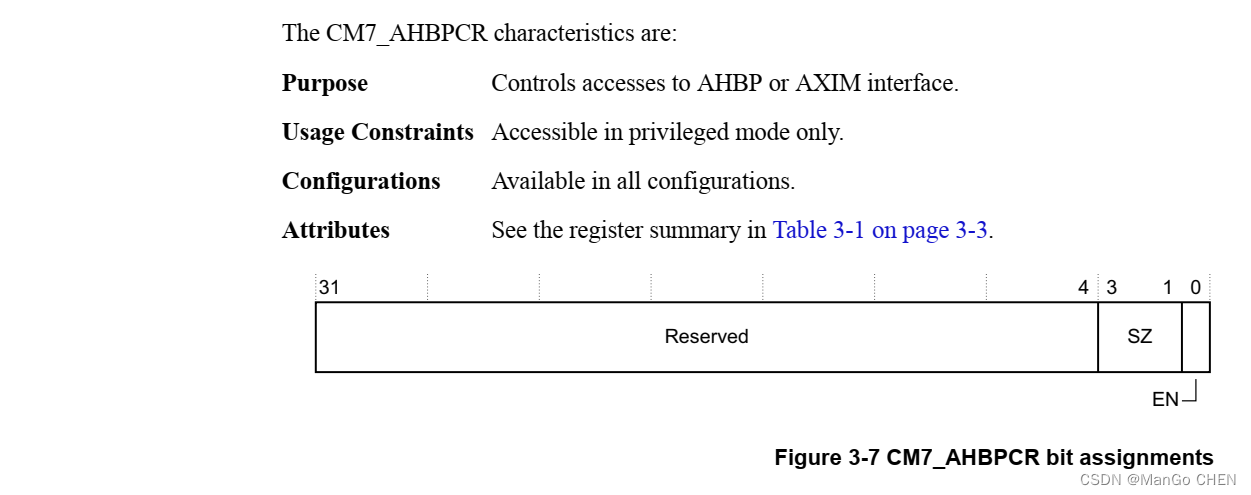

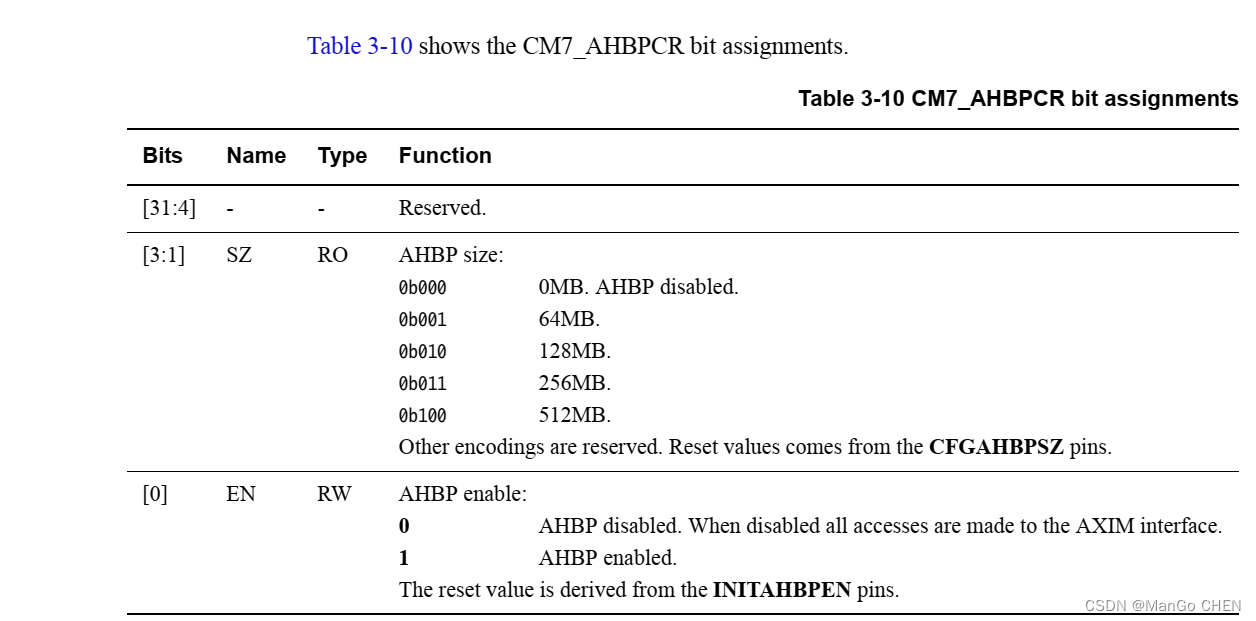

3.3.7 AHBP控制寄存器

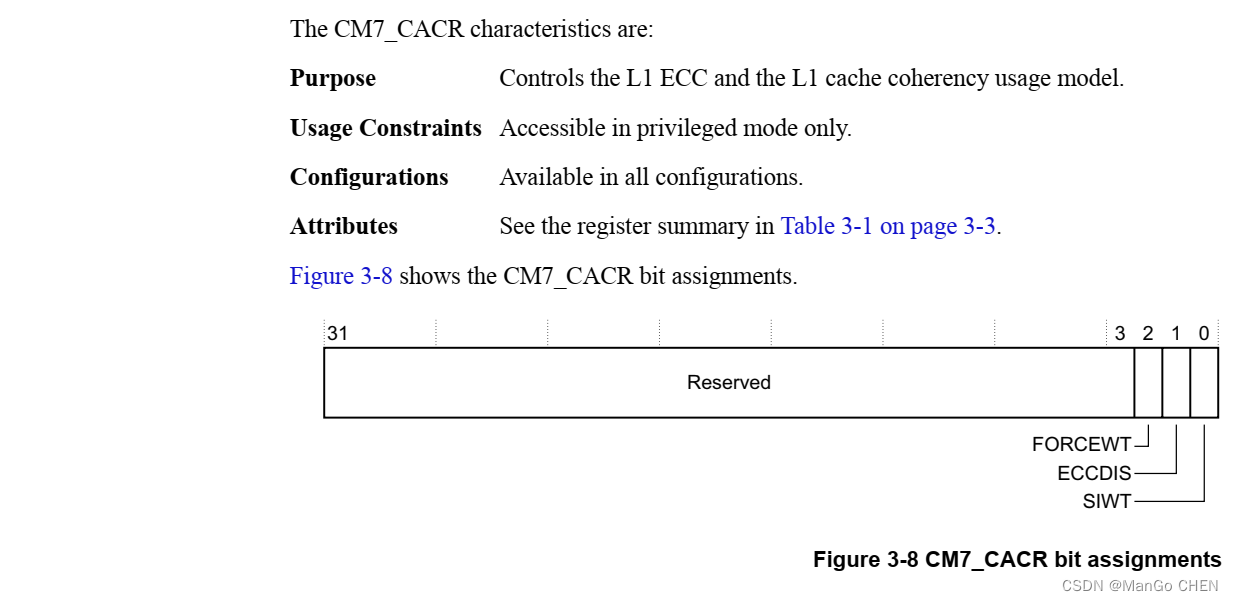

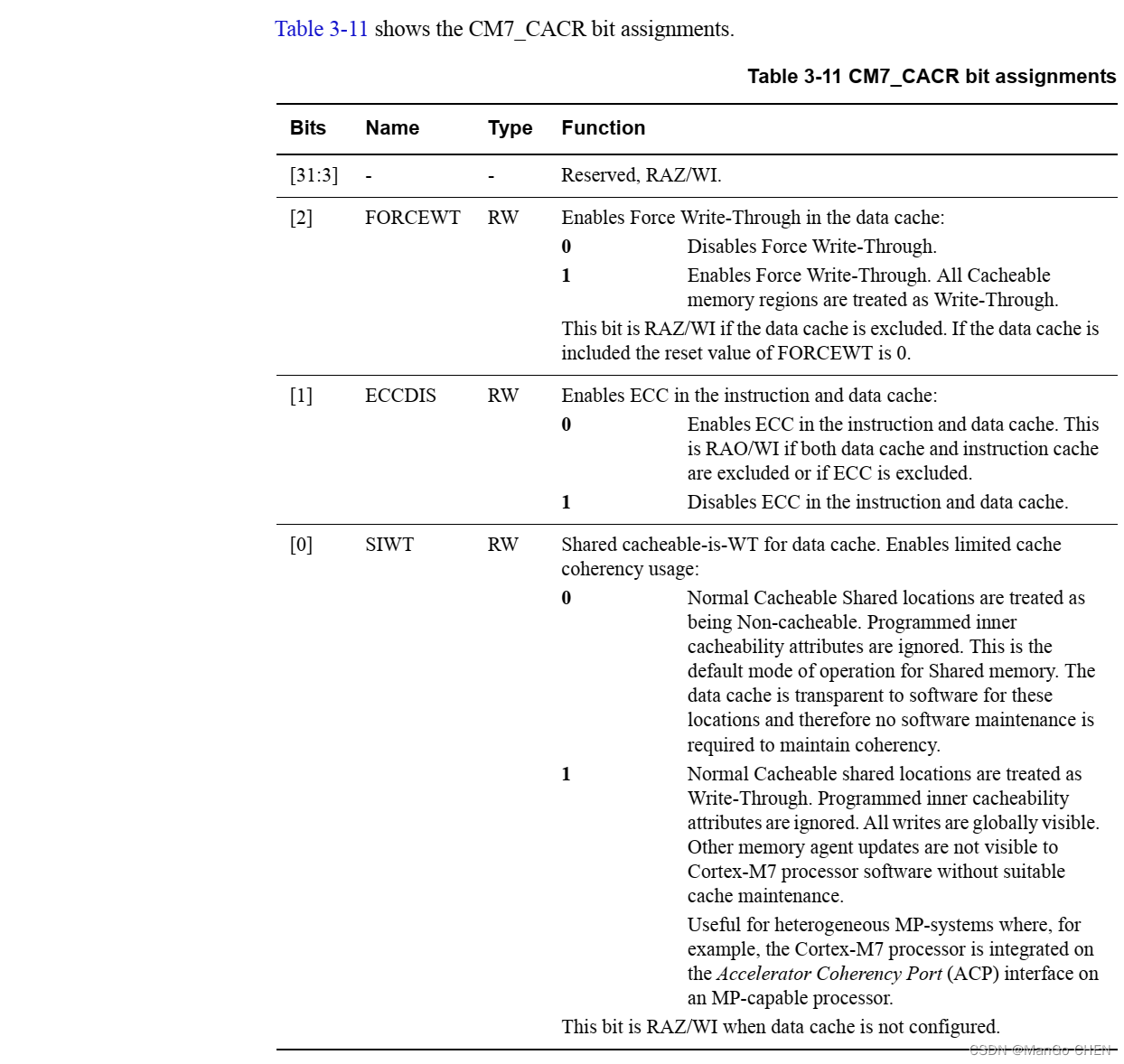

3.3.8 L1缓存控制寄存器

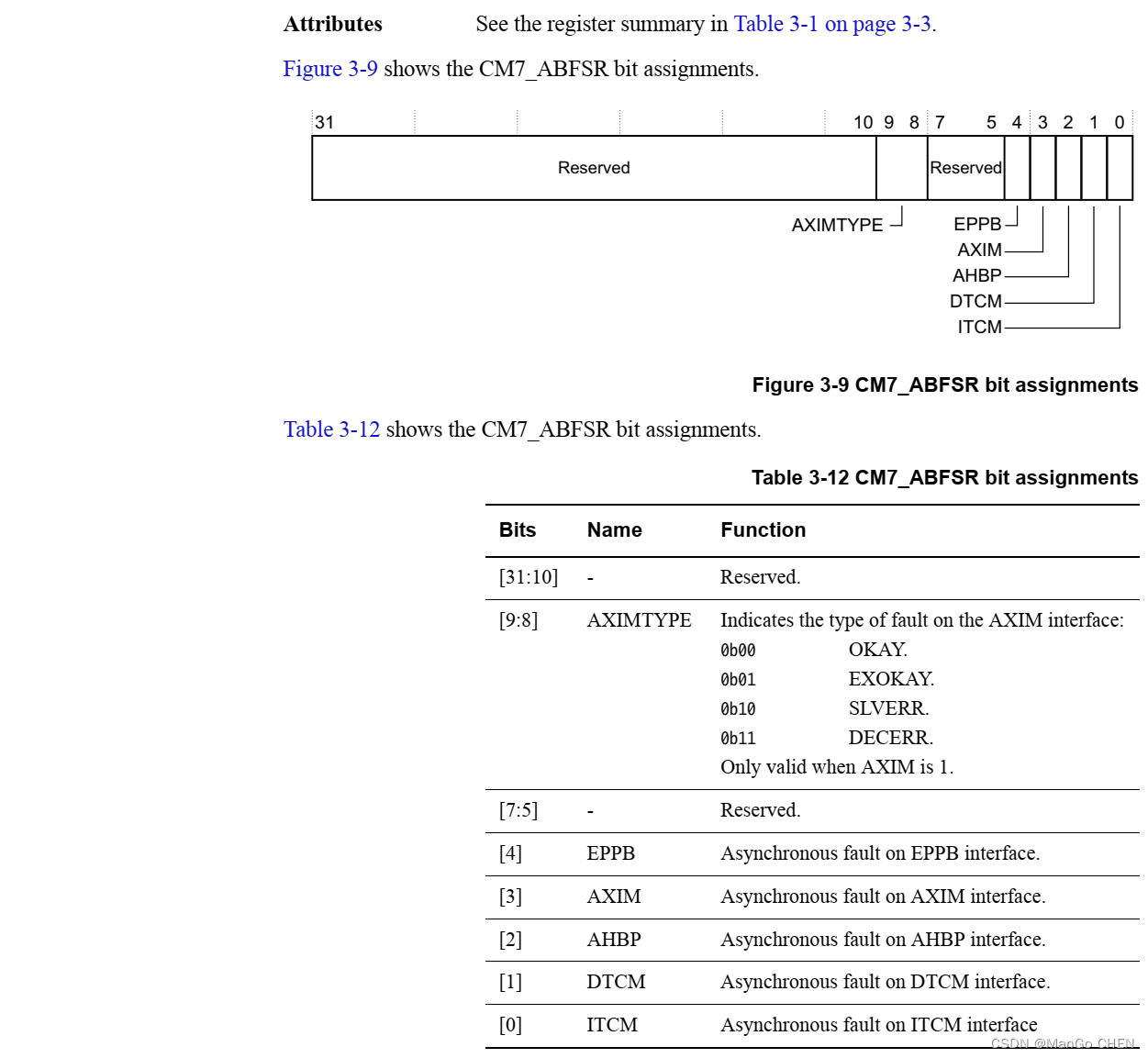

3.3.9辅助母线故障状态登记

3.3.10指令错误库寄存器0-1

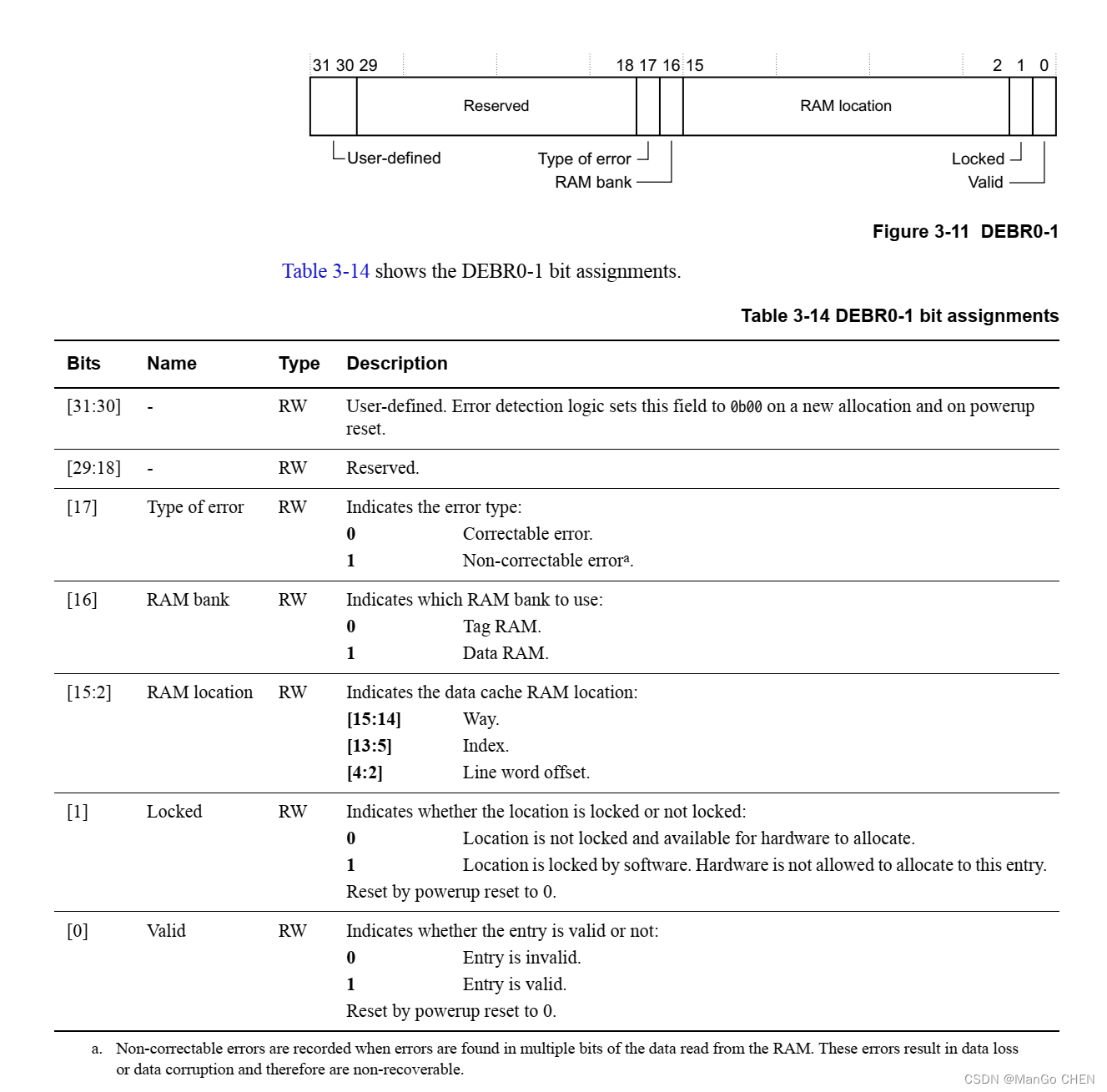

3.3.11数据错误银行寄存器0-1

3.3.12 AHB从控制寄存器