文章目录

- 一、实验环境

- 二、实验任务

- 三、实验过程

- 3.1 编写verliog程序

- 3.2 引脚配置

- 四、仿真

- 4.1 仿真代码

- 4.2仿真结果

- 五、实验结果

- 六、总结

一、实验环境

quartus18.1

vscode

Cyclone IV开发板

二、实验任务

每间隔1S实现led灯的亮灭,实现流水灯的效果。

三、实验过程

3.1 编写verliog程序

//每间隔1S实现LED的亮灭

module led(

input clk ,

input rst_n ,

output reg [3:0] led

);

//计时1S

//parameter CNT0_2S = 24'd9;//如果要进行仿真的话就使用这个计数器

parameter CNT0_2S = 24'd9_999_999;

reg [23:0] cnt ;//保存时钟上升沿的个数

reg [1:0] state ;

always @(posedge clk or negedge rst_n) begin//对寄存器赋值要使用always

if(!rst_n)begin

cnt <= 24'd0;

end

else if(cnt == CNT0_2S)begin

cnt <= 24'd0;

end

else begin

cnt <= cnt + 1'd1;

end

end

always @(posedge clk or negedge rst_n) begin

if(!rst_n)begin

state <= 2'd0;

end

else if(state == 2'd3 && cnt == CNT0_2S)begin

state <= 2'd0;

end

else if(cnt == CNT0_2S)begin

state <= state + 1'd1;

end

end

always @(posedge clk or negedge rst_n) begin

if(!rst_n)begin

led <= 4'b0000;

end

else begin

case (state)

2'd0: led <= 4'b0001;

2'd1: led <= 4'b0010;

2'd2: led <= 4'b0100;

2'd3: led <= 4'b1000;

default:led <= 4'b0000;

endcase

end

end

//0001,0010,0100,1000,0001

// always @(posedge clk or negedge rst_n) begin

// if(!rst_n)begin

// led <= 4'b0001;

// end

// else if(cnt == CNT0_2S)begin

// led <= {led[2:0],led[3]};//使用位拼接可以更简单的实现流水灯

// end

// else begin

// led <= led;

// end

// end

endmodule

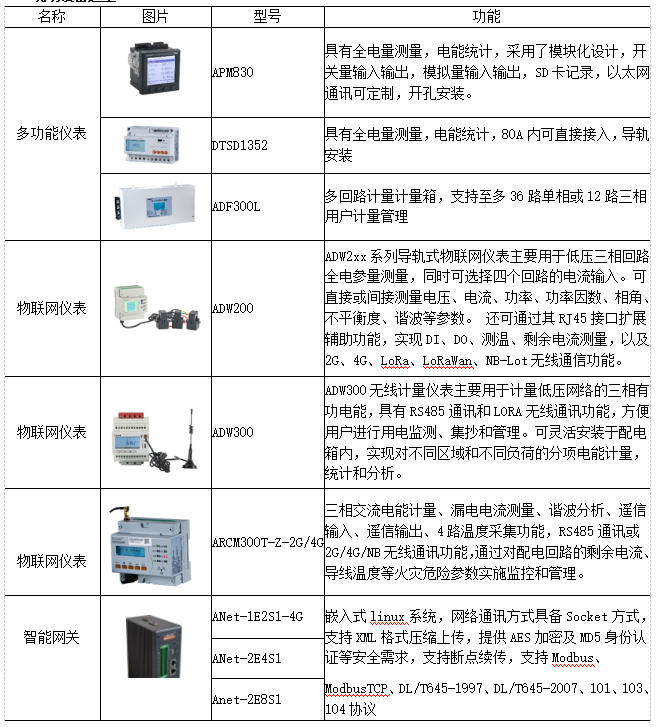

3.2 引脚配置

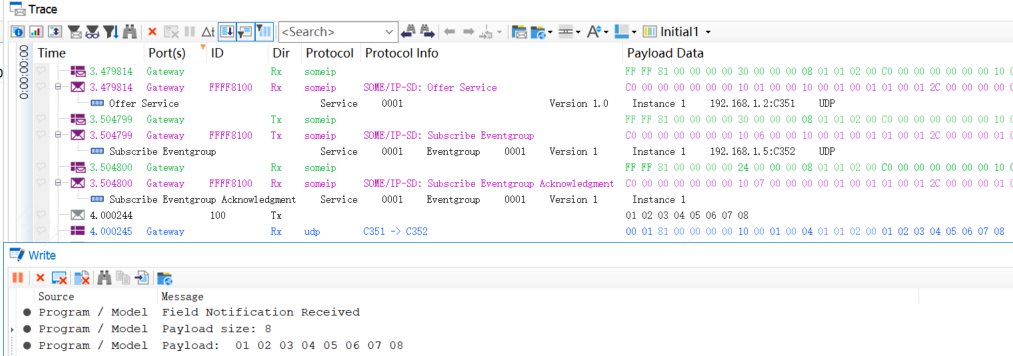

四、仿真

4.1 仿真代码

`timescale 1ns/1ns

module led_tb();

reg clk;

reg rst_n;

wire [3:0] led;

always #10 clk = ~clk;

initial begin

clk = 1'b0;

rst_n = 1'b0;

#10 rst_n = 1'b1;

#1000 $stop ;

end

led u_led(

.clk (clk),

.rst_n (rst_n),

.led (led)

);

endmodule

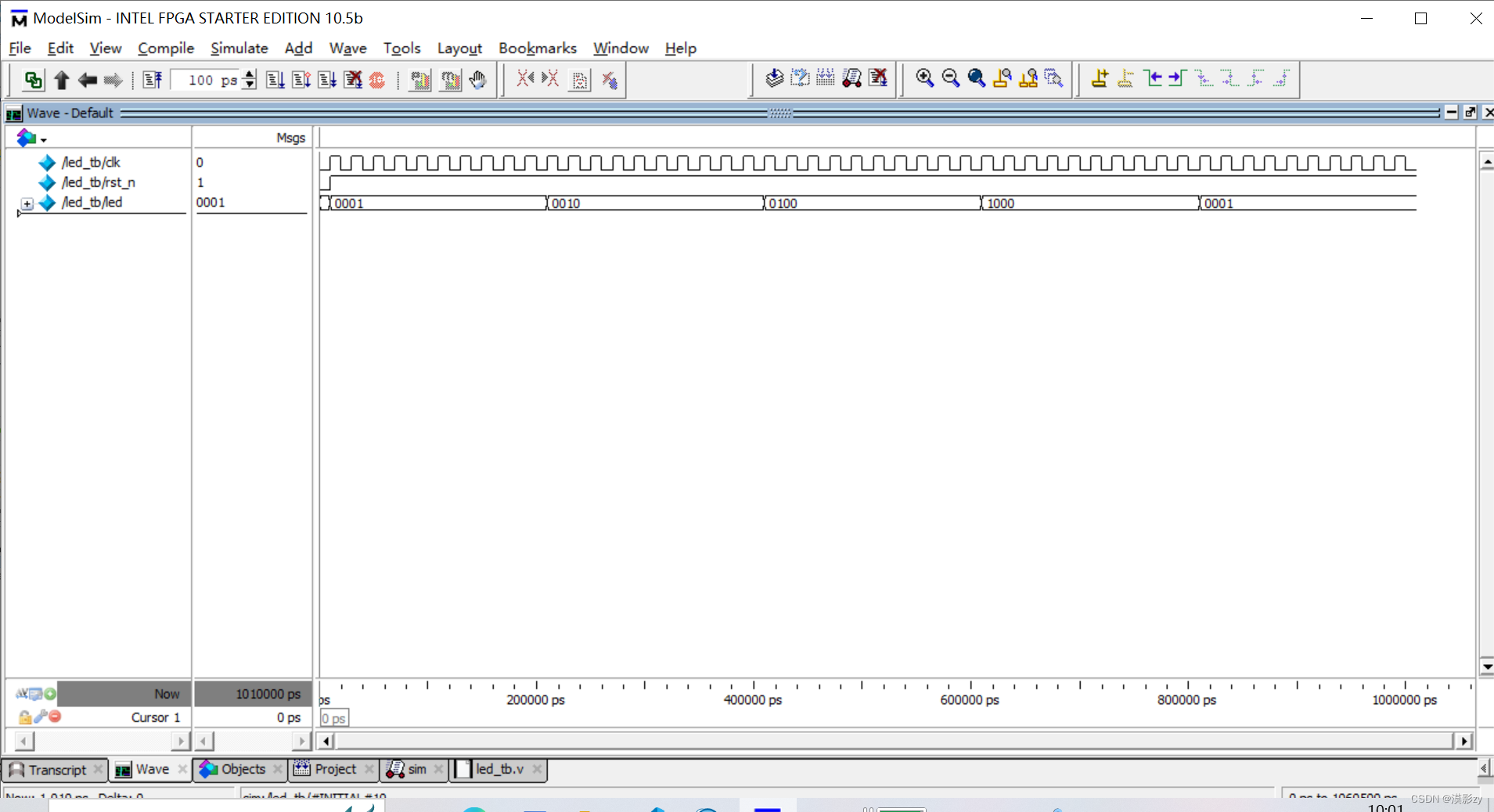

4.2仿真结果

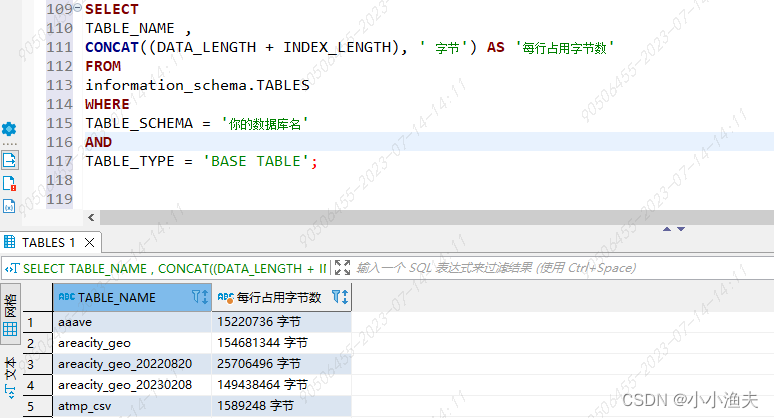

五、实验结果

六、总结

本次实验主要是学习verilog的基础语法,掌握计数器的编写以及时序逻辑的设计方法。另外在进行仿真的时候需要修改计数器的大小,因为我们仿真设计的是延时1000ns,如果不把计数器改小的话就只能看到最开始的0001的状态,就无法判断逻辑是否出错。