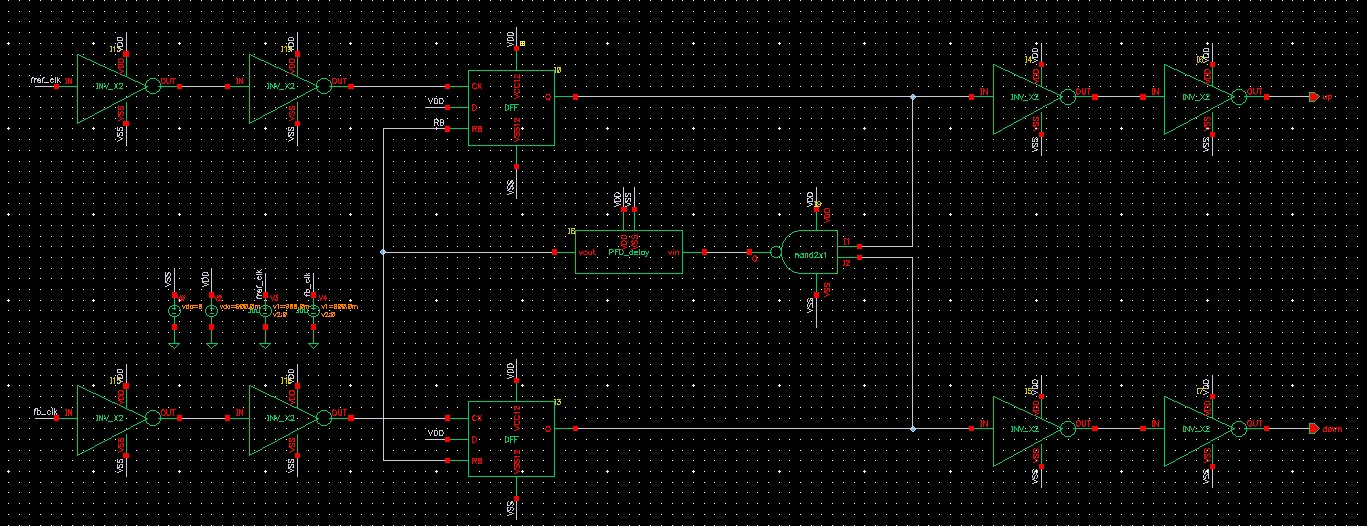

鉴相器一般用两个D触发器,一个与非门和一个延迟单元

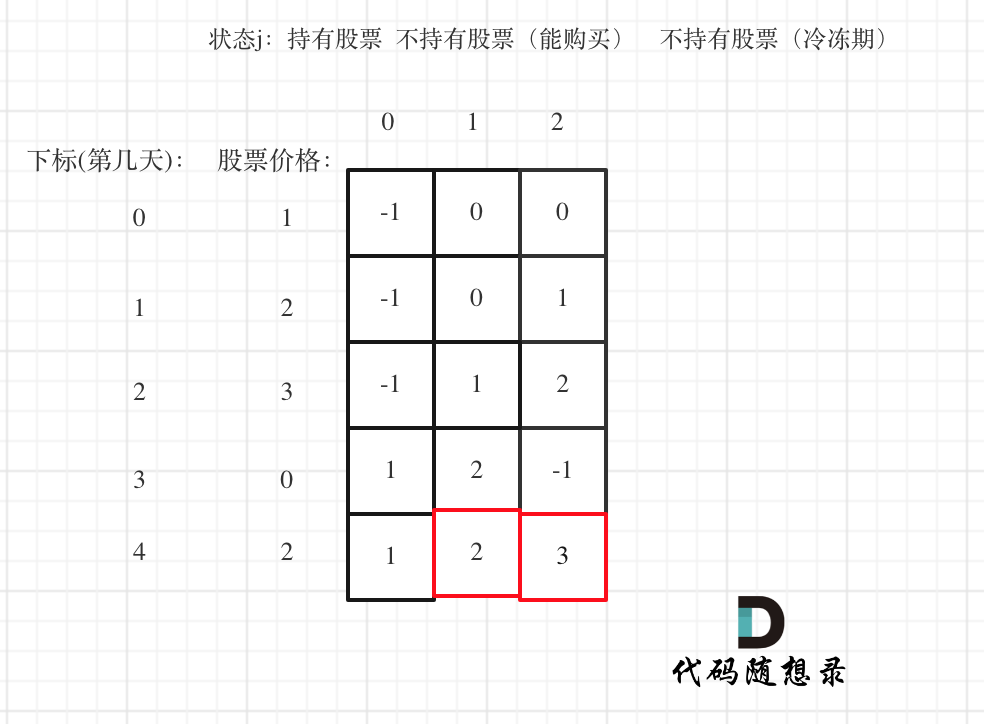

假设两个D触发器脉冲信号完全相同,查看D触发器输出端可以看到,在脉冲信号到来之后,D触发器输出端电压随脉冲信号升高,两个DFF输出同时为高时,与非门输出低电平。再经过一定的延时之后,reset将D触发器置0,D触发器输出端电压随之降低

通过增加延迟单元反相器的数量来增加延迟时间,延时时间的选择主要在于要使得D触发器的输出脉冲能将下一级的开关驱动即可。开关开启的时间过短会导致开关不能完全驱动,开启时间过长会把一些phase noise引入。一般200ps-500ps。

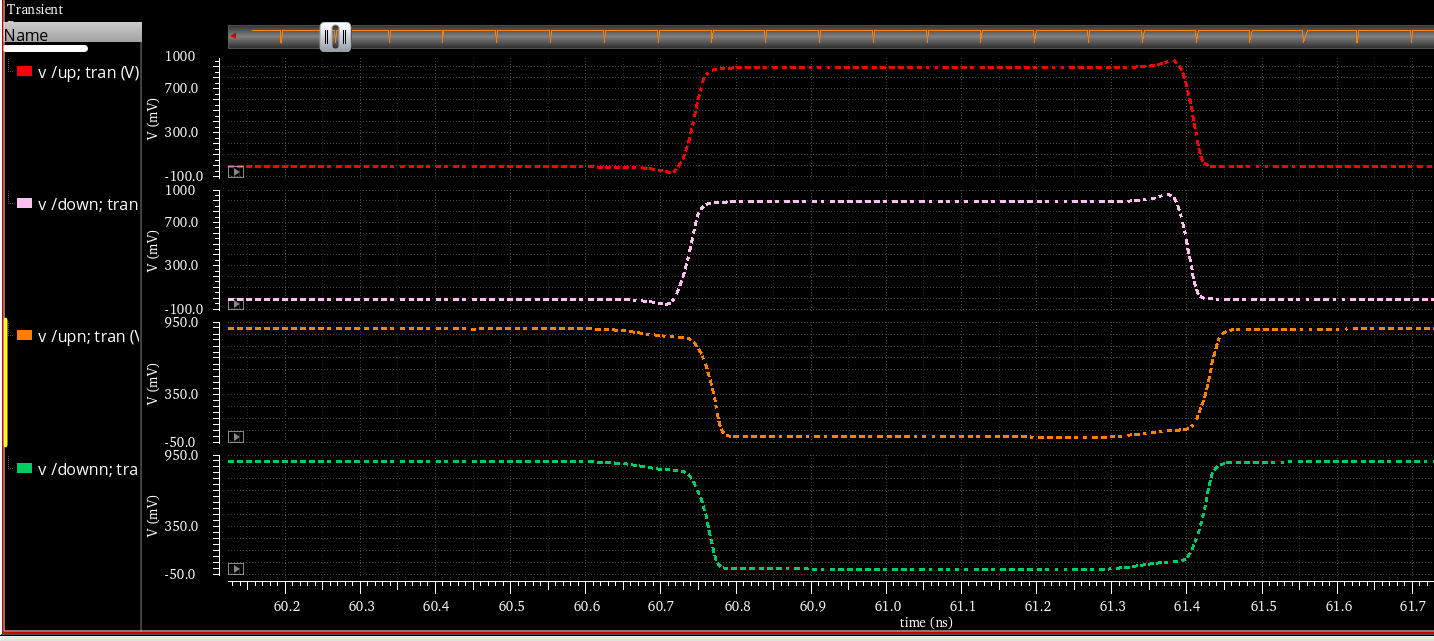

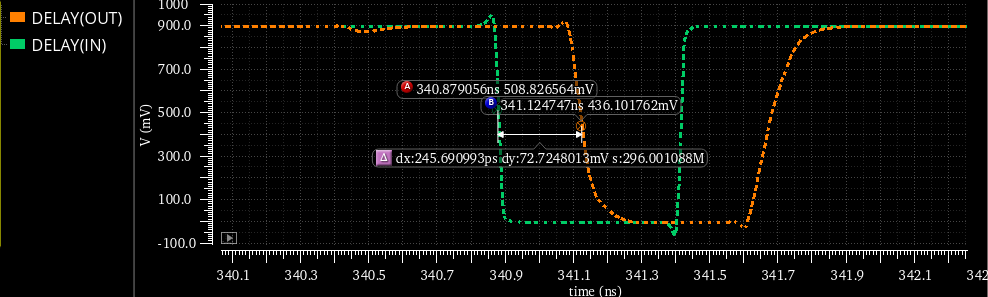

如图可以看出四个反相器时delay为132ps

将反相器个数增加至8个后,可以看出delay时间增加至245ps

假设两个DFF时钟信号有1ns的差值,DFF输出结果如图所示。

理论上D触发器的输出经过两个反相器的延迟时间和经过一个反相器和一个传输门的延迟时间是相同的。但是实际上这两个延迟时间很难达到,所以需要做匹配。可以通过做两个支路的延迟,一个支路是3个反相器,一个支路是一个反相器,两条支路的延时叠加就能做一个较好的匹配。