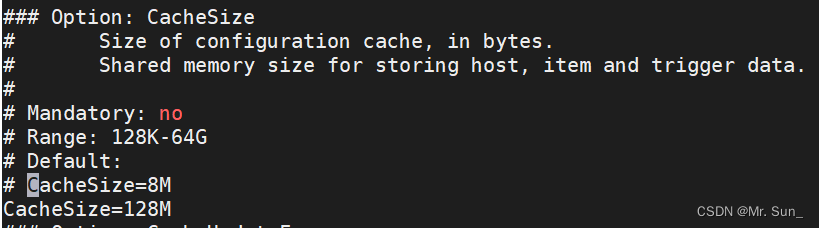

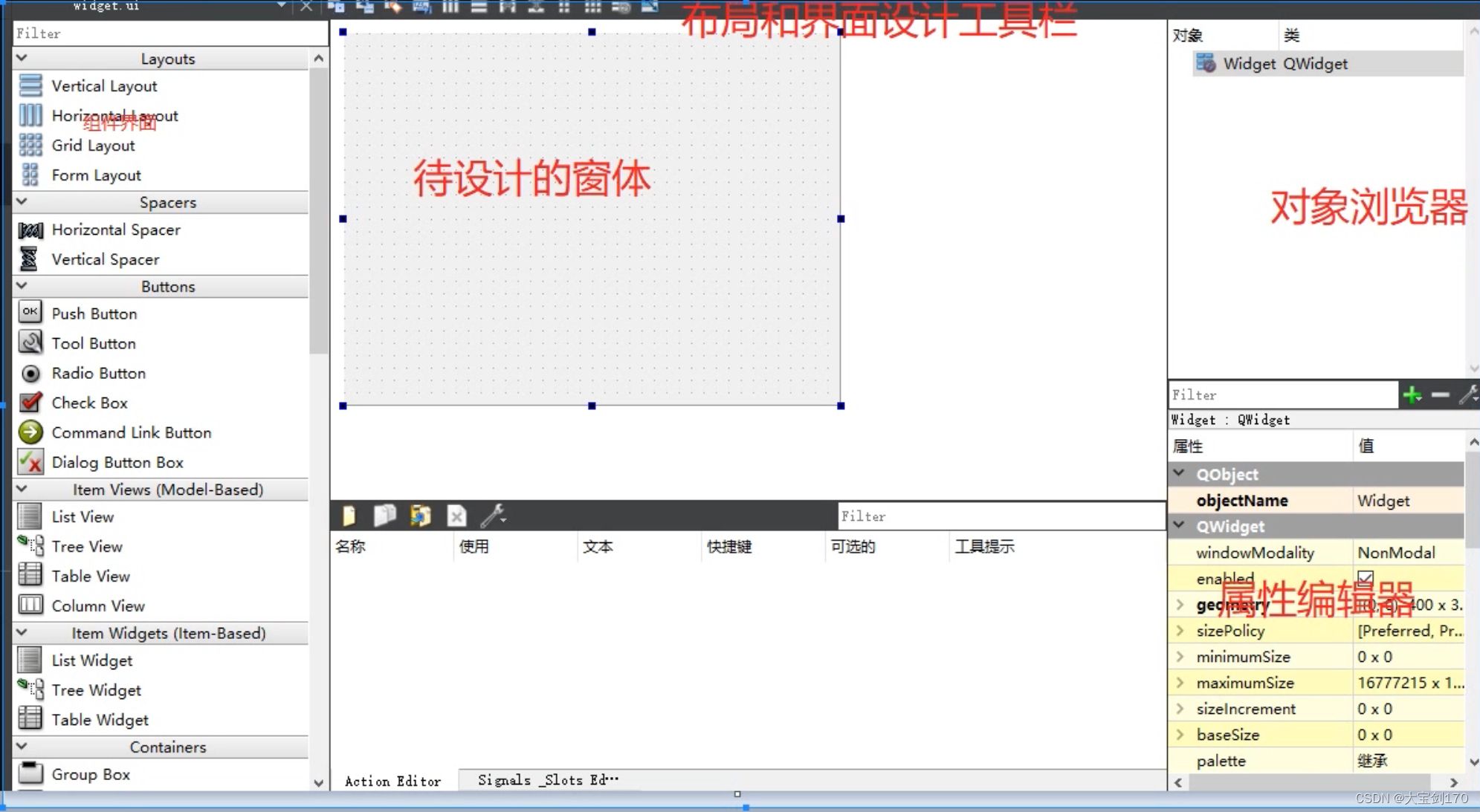

5.1 从PCIe的速度说起

为什么SSD要用PCIe接口?因为它快,比SATA快。

Lane:通道,PCIe最多可以有32个通道。

1. PCIe的工作模式

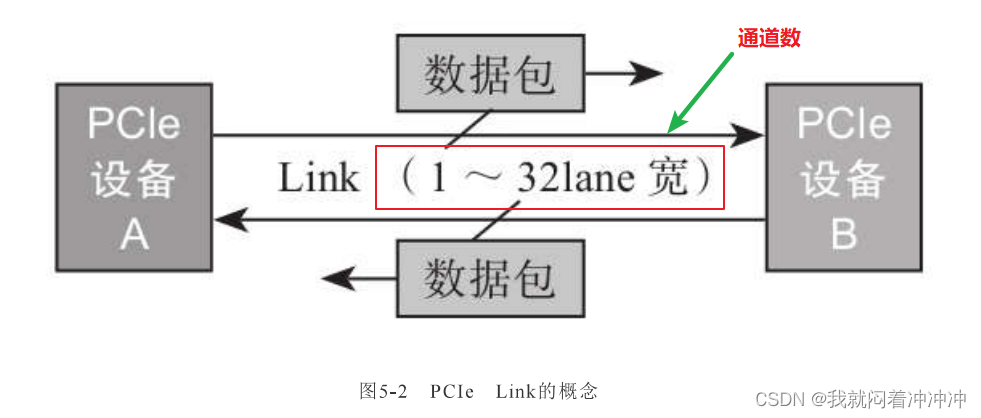

两个设备之间的PCIe连接,叫做一个Link。如下图,设备A和设备B是个双向连接,两个PCIe设备之间,有专门的发送和接收通道,数据可以同时往两个方向传输,PCIe Spec称这种工作模式为双单工模式(Dual-Simplex),可以理解为全双工模式。

2. SATA的工作模式

和PCIe一样,SATA有独立的发送和接收通道。但与PCIe工作模式不一样,同一时间,SATA只有一条通道可以进行数据传输。这种工作模式称为半双工模式。

与SATA单通道不同,PCIe连接可以通过增加通道数扩展带宽。

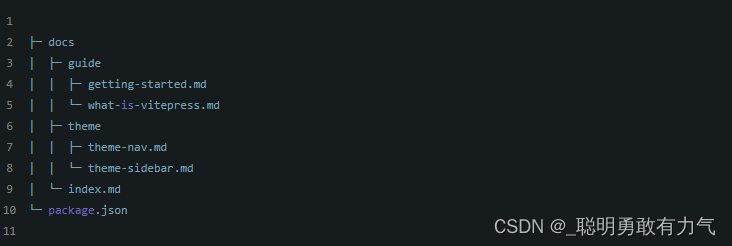

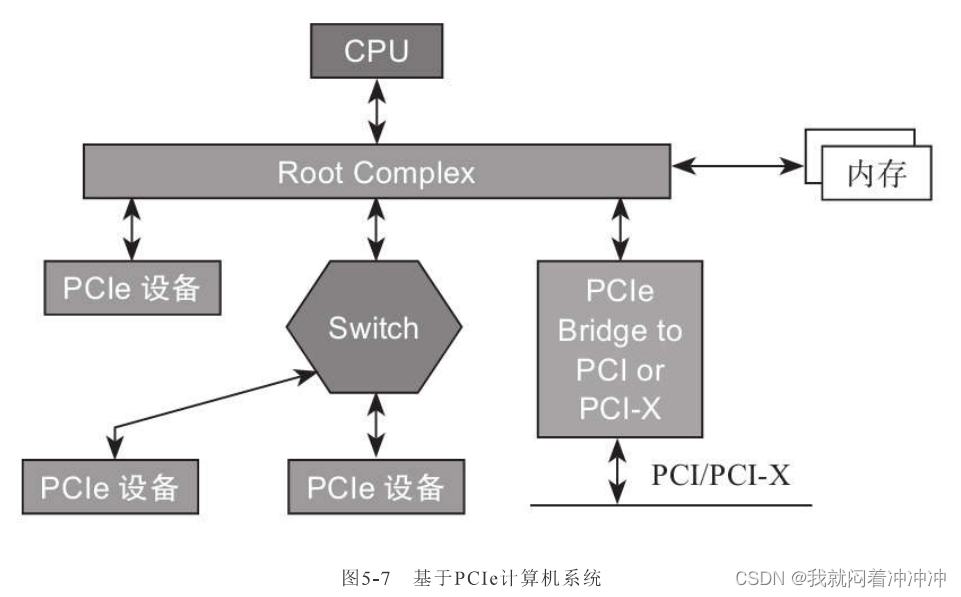

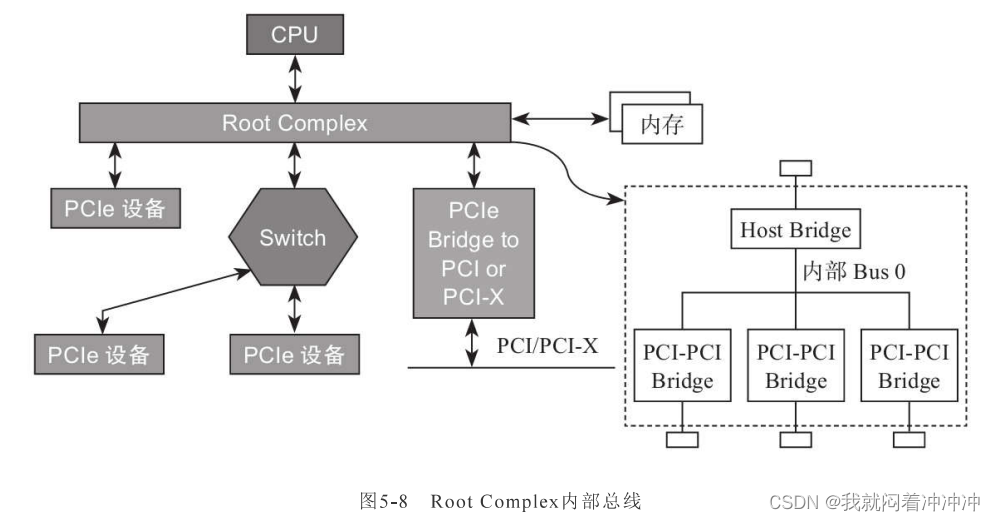

5.2 PCIe拓扑结构

把网络中的计算机和通信设备抽象为一个点,把传输介质抽象为一条线,由点和线组成的几何图形就是计算机网络的拓扑结构。

计算机网络主要的拓扑结构有:总线型拓扑、环形拓扑、树形拓扑、星形拓扑、混合型拓扑以及网状拓扑。

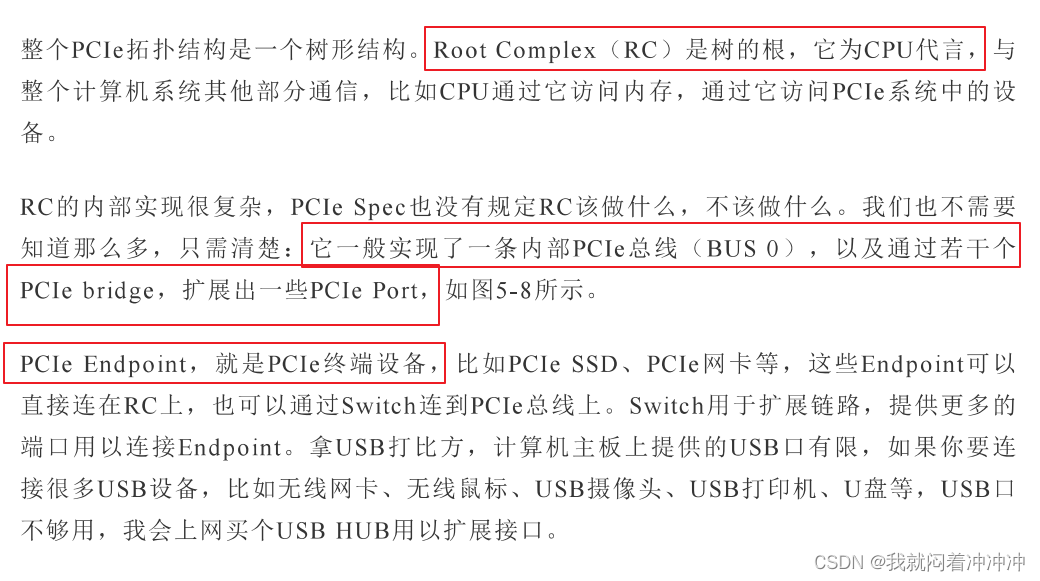

PCIe采用树形拓扑结构,如下:

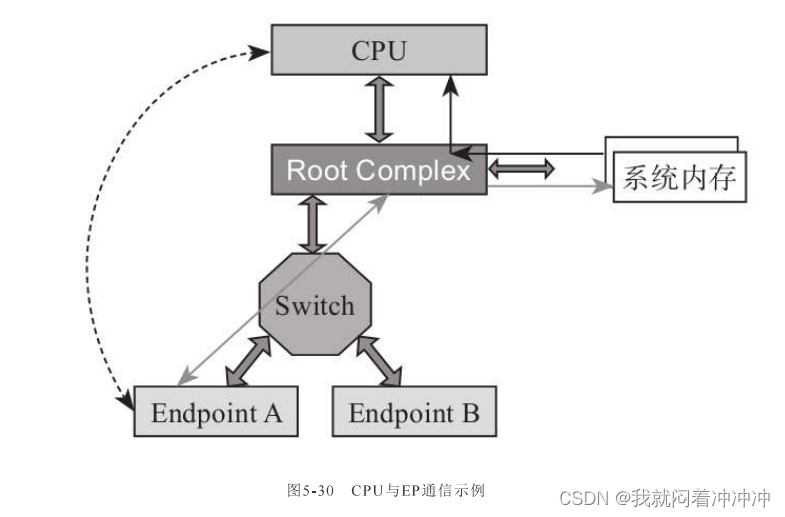

CPU只能直接访问主机内存空间(或IO空间),不能对PCIe等外设进行直接操作。

小结:

(1)PCIe采用树形拓扑结构,RC是树的根或主干,它为CPU代言,与PCIe系统的其他部分通信,一般为通信的发起者。

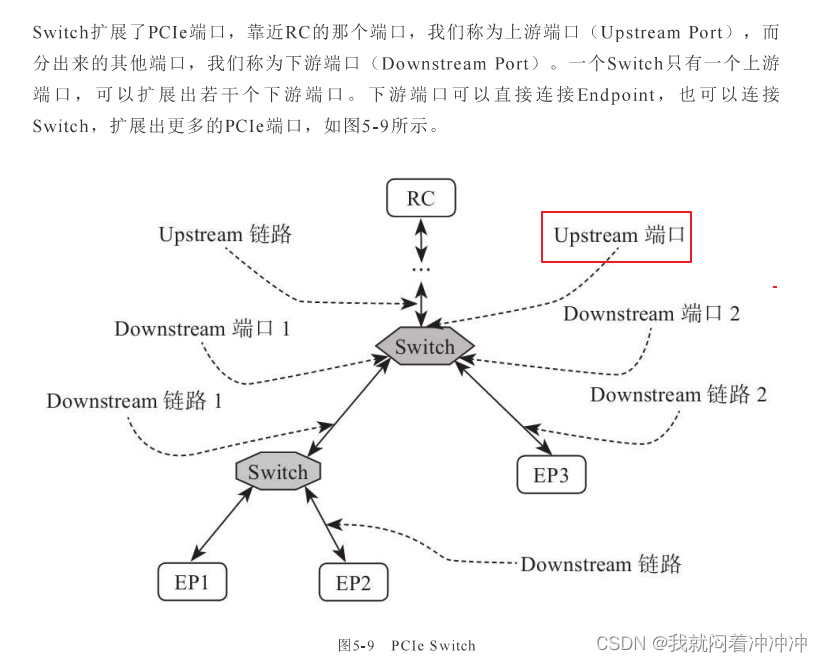

(2)Switch是树枝,树枝上有叶子(Endpoint),也可节外生枝,即Switch上连Switch,归根结底,是为了连接更多的叶子Endpoint。

(3)Switch为它下面的Endpoint或Switch提供路由转发服务。

(4)Endpoint是树叶,诸如SSD、网卡、显卡等,实现某些特定功能(Function)。

(5)PCIe采用点到点(Endpoint to Endpoint)的通信方式,每个设备独享通道带宽。

5.3 PCIe分层结构

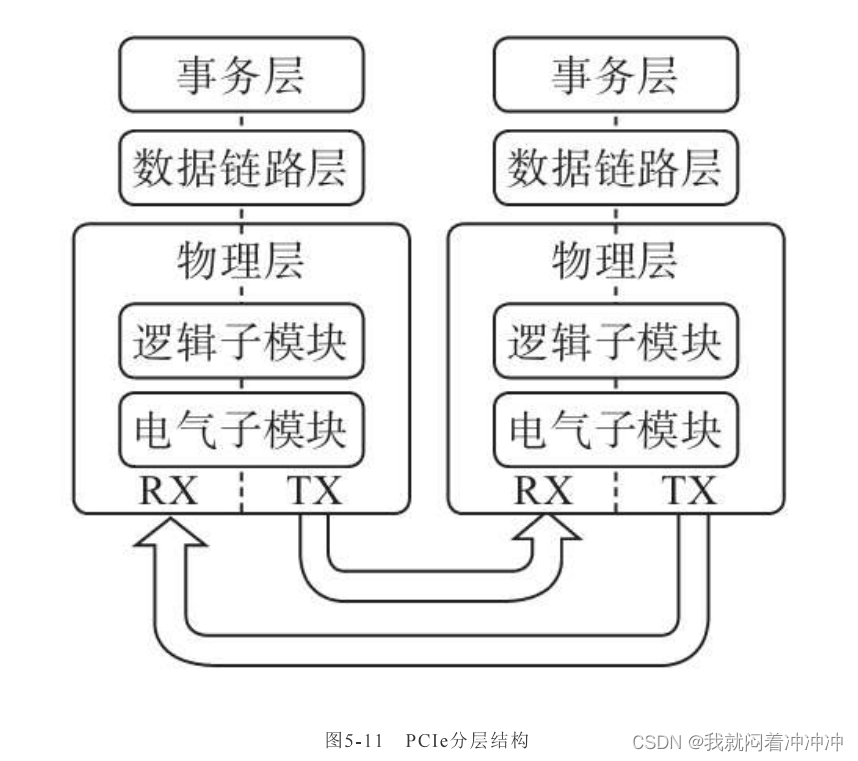

绝大多数总线或者接口都是采用分层实现的。PCIe的层次结构如下:

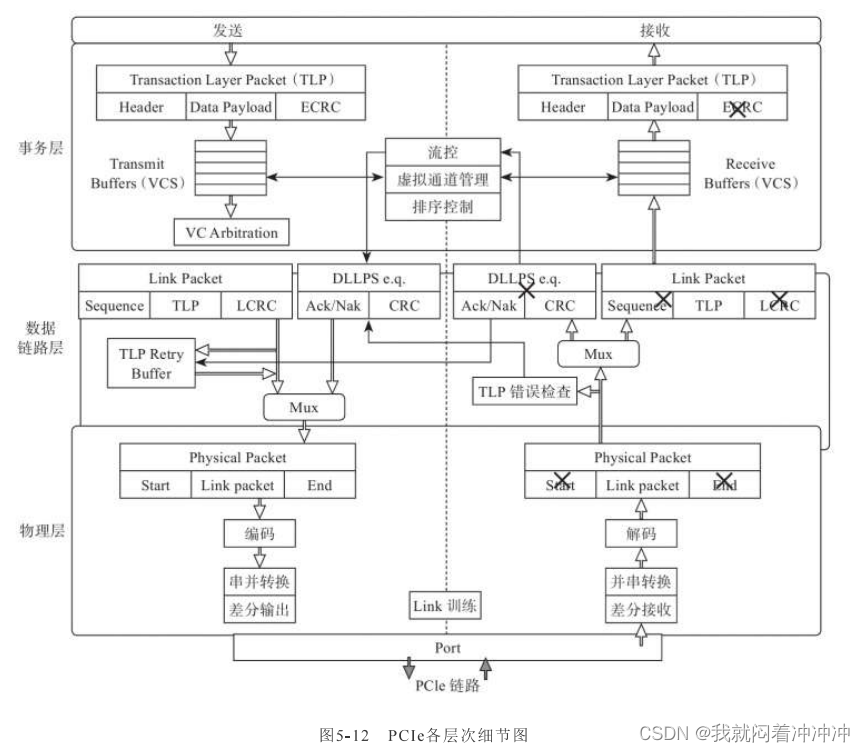

PCIe定义了以下三层:事务层(Transaction Layer)、数据链路层(Data Link Layer)和物理层(Physical Layer,包括逻辑子模块和电气子模块),下层总是为上层服务。

PCIe传输的数据从上到下,都是以数据包(Packet)的形式传输的,每层数据包都是其固定的格式。

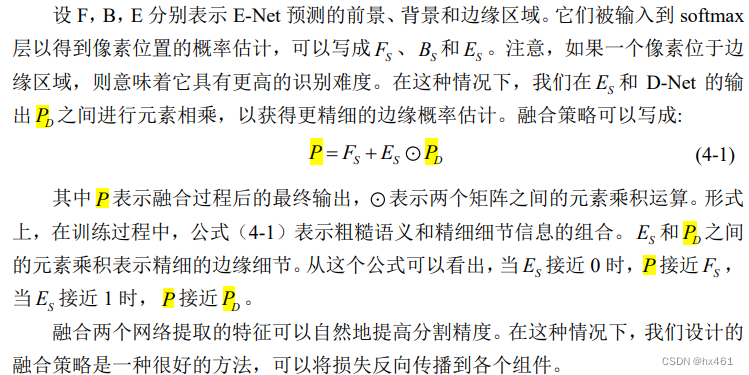

(1)事务层

事务层主要负责创建(发送) 或 解析(接收) TLP(Transaction Layer Packet)、流量控制、QoS、事务排序等。

(2)数据链路层

主要负责创建(发送) 或 解析(接收) DLLP(Data Link Layer Packet)、Ack / Nak协议(链路层检错和纠错)、流控、电源管理等。

(3)物理层

主要负责处理所有的Packet数据物理传输,发送端数据分发到各个Lane传输(Stripe),接收端把各个Lane上的数据汇总起来(De-stripe),每个Lane上加干扰(Scramble,目的是让0和1均匀分布,去除信道的电磁干扰EMI)和去扰(De-Scramble),以及8 / 10 或者 128 / 130 编码解码等。

8 / 10:8bit的数据,实际在物理线路上是需要传输10bit的,多余的2bit用来校验。

各层的细节图如下:

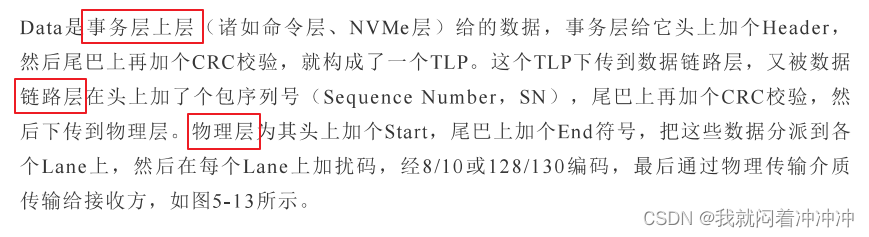

发送方打包TLP的过程如下:

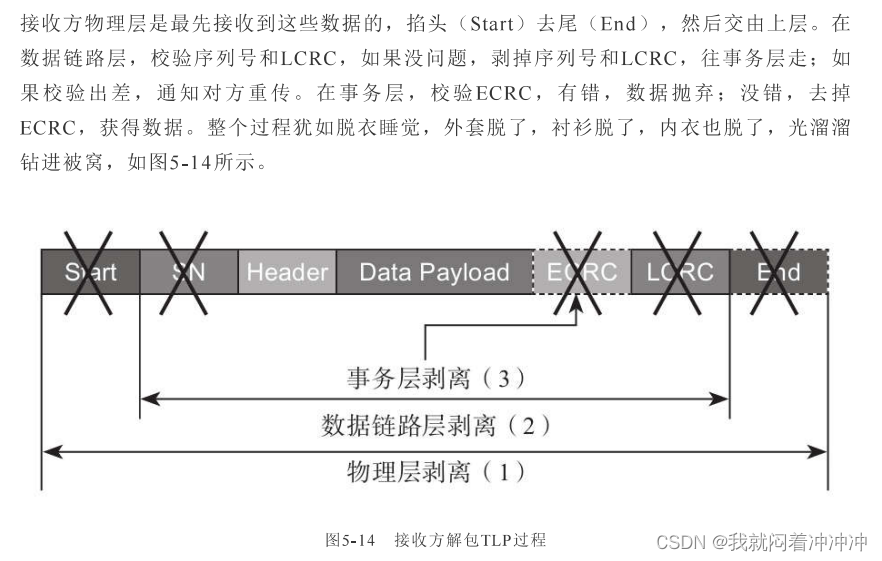

接收方解包TLP的过程如下:

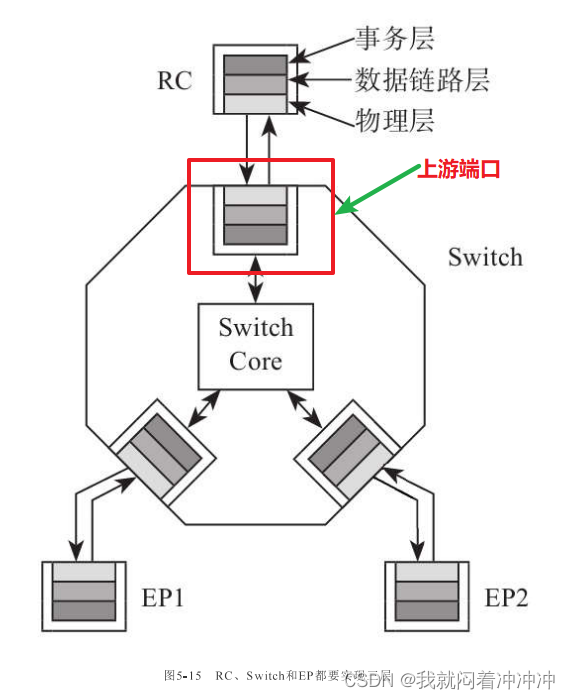

每个Endpoint都需要实现这三层,每个Switch的Port也需要实现这三层!!如下:

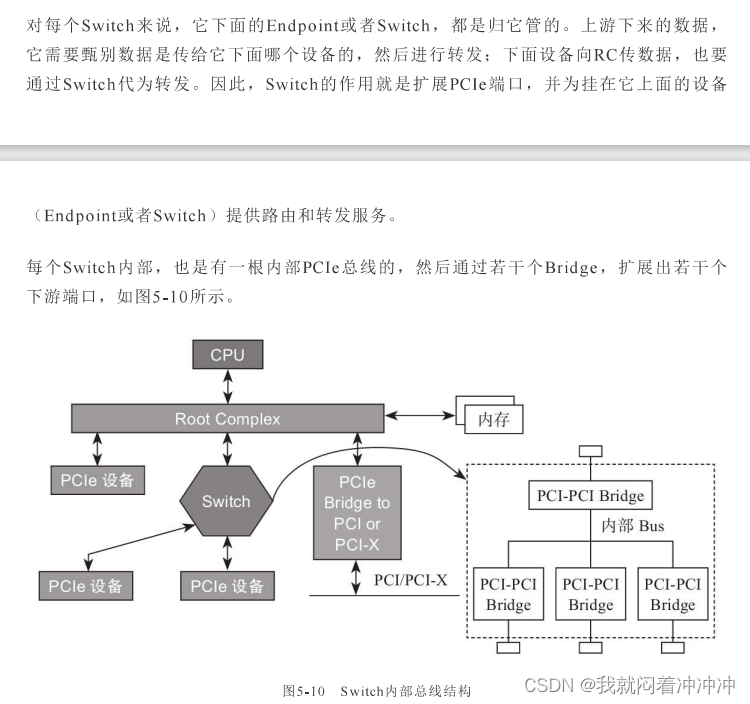

Switch的主要功能是转发数据,那么它为什么也要实现这三层呢???

答:数据的目的地信息是包含在TLP里的,如果不实现这三层,就无法知道目的地,也就无法实现数据寻址路由。

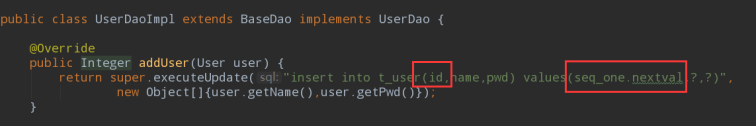

5.4 PCIe TLP类型

主机与PCIe设备之间,或PCIe设备与设备之间,数据传输都是以Packet形式进行的。事务层根据上层( 应用层 或 软件层 )请求(Request)的类型、目的地址和其他相属性,将这些请求打包,生成TLP(事务层数据包),然后历经数据链路层、物理层,最终到达目标设备。

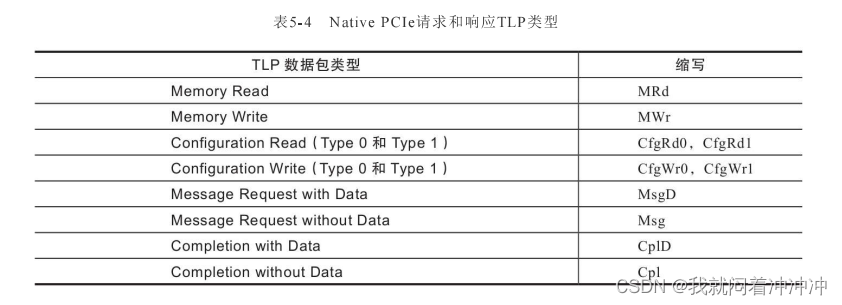

根据软件层的不同请求,事务层产生四种不同的TLP请求:Memory、IO、Configuration、Message。

前三种分别用于访问内存空间、IO空间、配置空间,Message用于传输中断信息、错误信息等。

一个设备的物理空间,可以通过内存映射(Memory Map)的方式映射到主机的主存。

所有配置空间(Configuration)的访问,都是主机发起的,确切的说是RC发起的,往往只在上电枚举和配置阶段会发起对配置空间的访问,才会有Configuration TLP;

只有在中断或有错误的情况下,才会有Message TLP;

故而,PCIe线上主流传输的是Memory访问相关的TLP。

这四种TLP请求,如果需要对方回应(对方返回一个Completion TLP),称之为Non-Posted TLP;不需要对方回应,称之为Posted TLP。

(1)Non-Posted TLP:Configuration、IO、 Memory Read;

(2)Posted TLP:Memory Write、Message。

由以上可知,PCIe里面所有的TLP = Request TLP + Completion TLP !!!

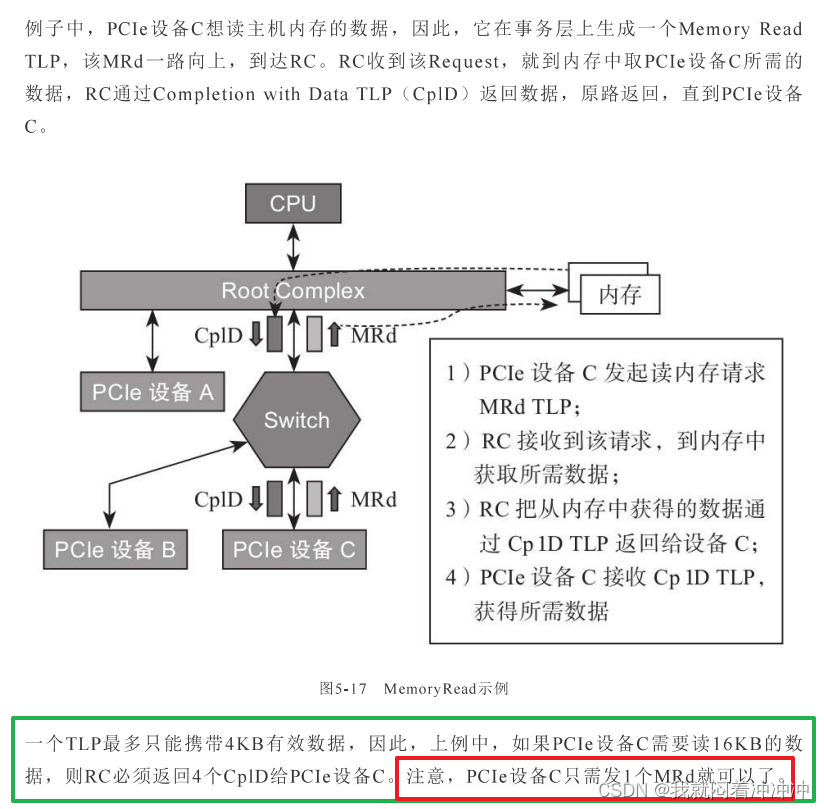

以Memory Read为例,说明请求的过程:

5.5 PCIe TLP结构

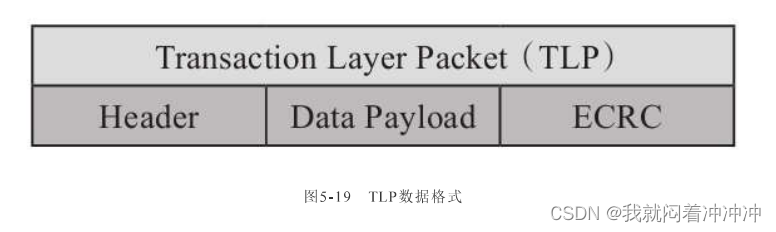

无论是Request TLP,还是作为回应的Completion TLP,都由以下部分组成:

TLP主要由三部分组成:Header、Data(可选,取决具体TLP类型)和ECRC(可选)。

TLP都是始于发送端的事务层,终于接收端的事务层。

(1)Header

每个TLP都有一个Header。

事务层根据上层请求的内容,生成TLP Header。

Header中的内容包括发送者的相关信息、目标地址、TLP类型(如Memory Read)、数据长度等。

一个Header的大小可以是3DW(Double Word,1DW = 4byte),也可以是4DW。

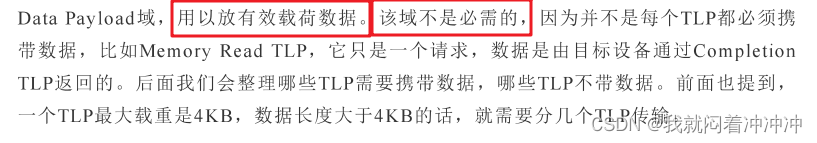

(2)Data Payload域

(3)ECRC(End to End CRC)域

下面分别介绍具体TLP的Header。

1. Memory TLP

对一个PCIe设备来说,它开放给主机访问的设备空间首先会映射到主机的内存空间,主机如果想访问设备的某个空间,TLP Header当中的地址应该设置为该访问空间在主机内存的映射地址。

TLP在经过Switch的时候,Switch会根据地址信息,把该TLP转发到目标设备。

Memory TLP的目标地址是通过内存地址告知的,来源则是由“Requester ID”告知的。

每个PCIe设备(RC、Switch或Endpoint)在PCIe系统中,都有唯一的ID,该ID由总线(Bus)、设备(Device)、功能(Function)三者唯一确定。

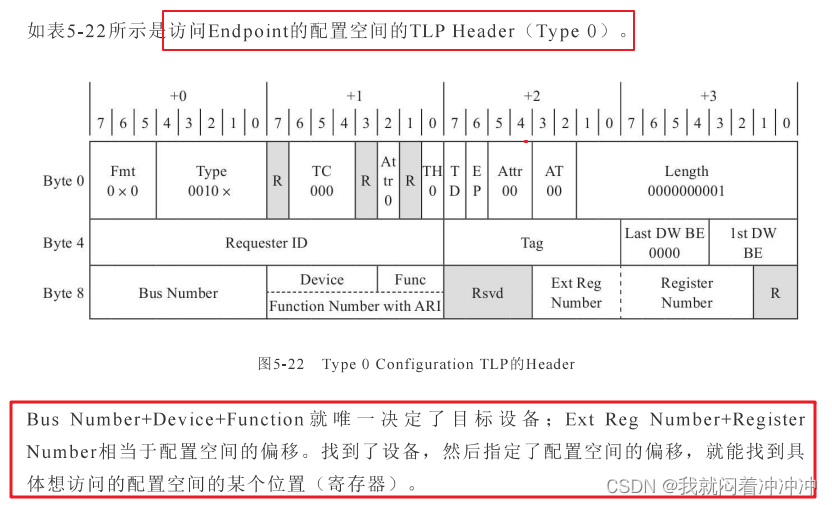

2. Configuration TLP

Endpoint和Switch的配置(Configuration)格式不一样,分别由Type 0 和Type 1 来表示。

配置可以认为是一个Endpoint或Switch的标准空间,这段空间在初始化时需要映射到主机的内存空间。

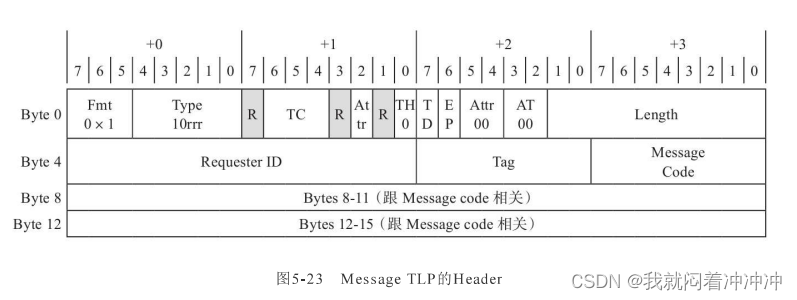

3. Message TLP

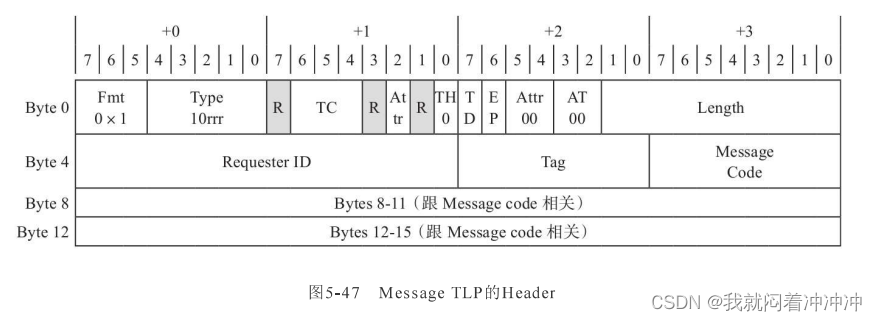

Message TLP用于传输中断、错误、电源管理等信息,它的Header大小是4DW。

Message Code指定该Message的类型。

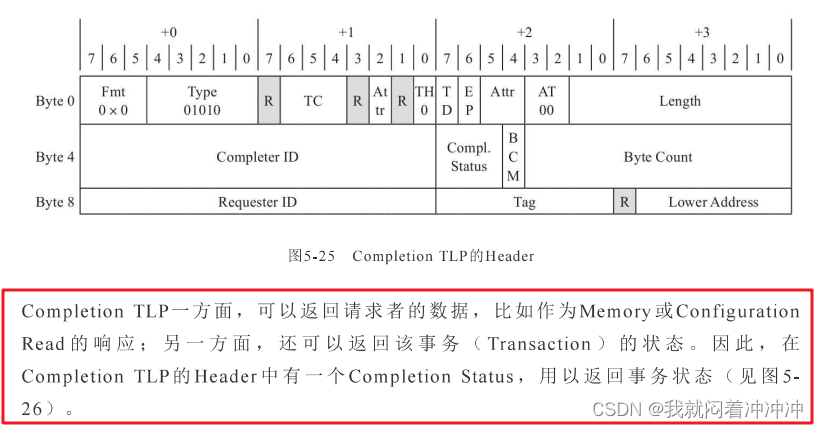

4. Completion TLP

只有Non-Posted Request TLP,才会有Completion TLP。

从前面三个Requester TLP可知,它们的Header中都有Requester ID 和 Tag,来告知接收者和发起者是谁。那么响应者的目标地址就是发起者的源地址。

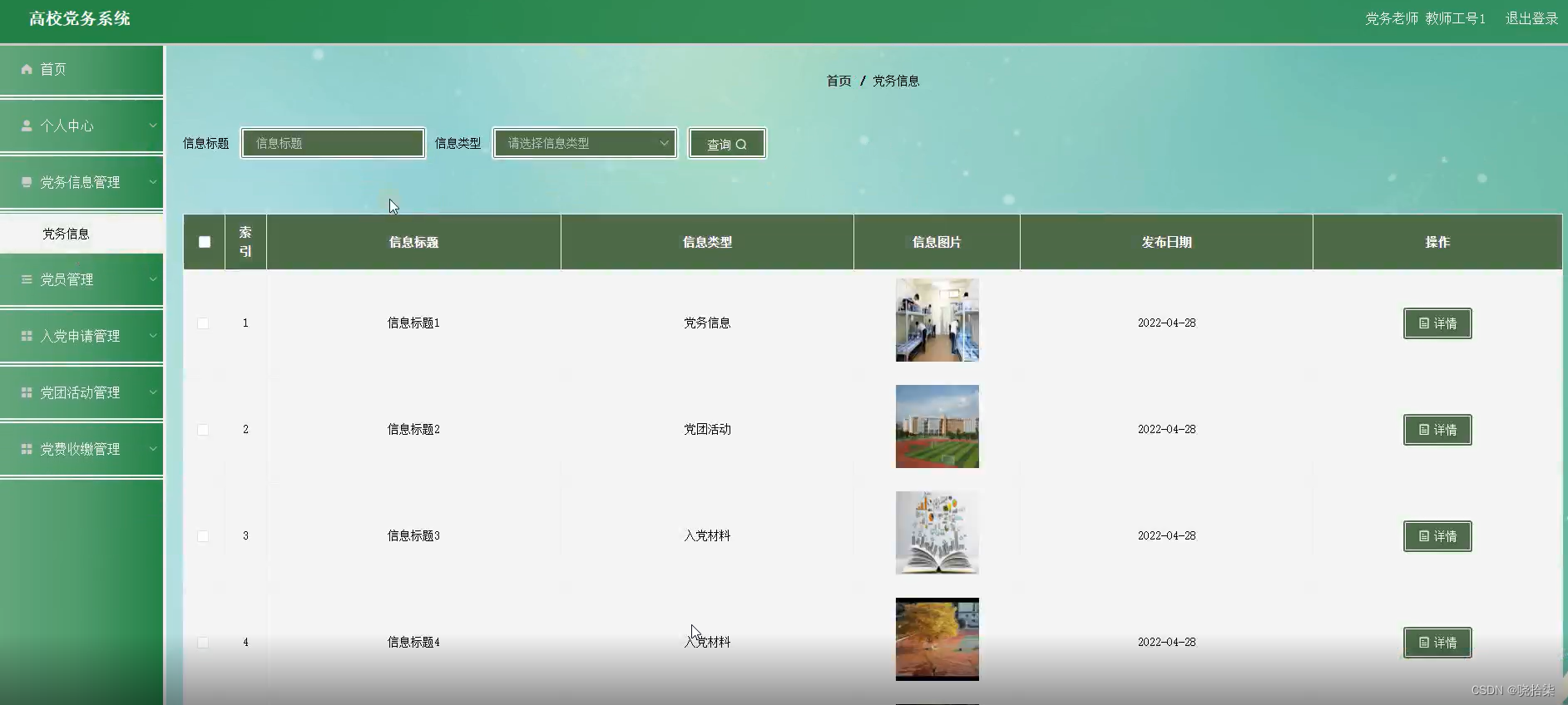

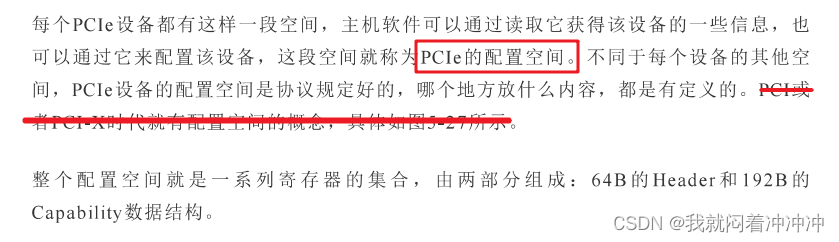

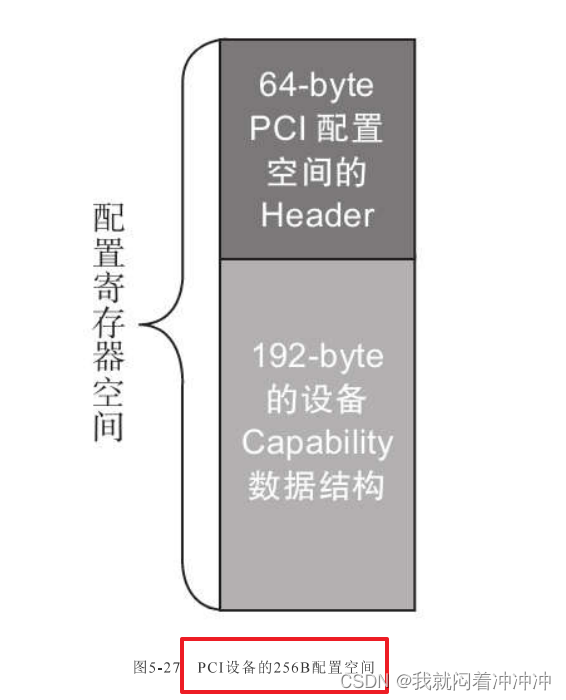

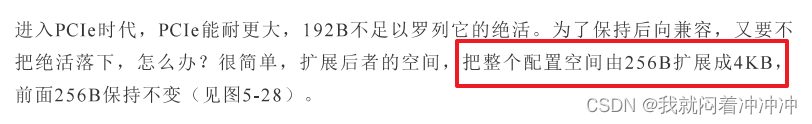

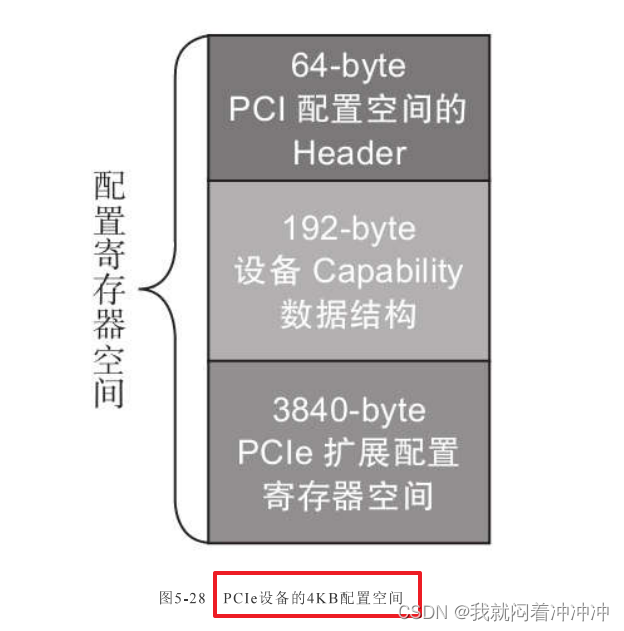

5.6 PCIe配置空间和地址空间

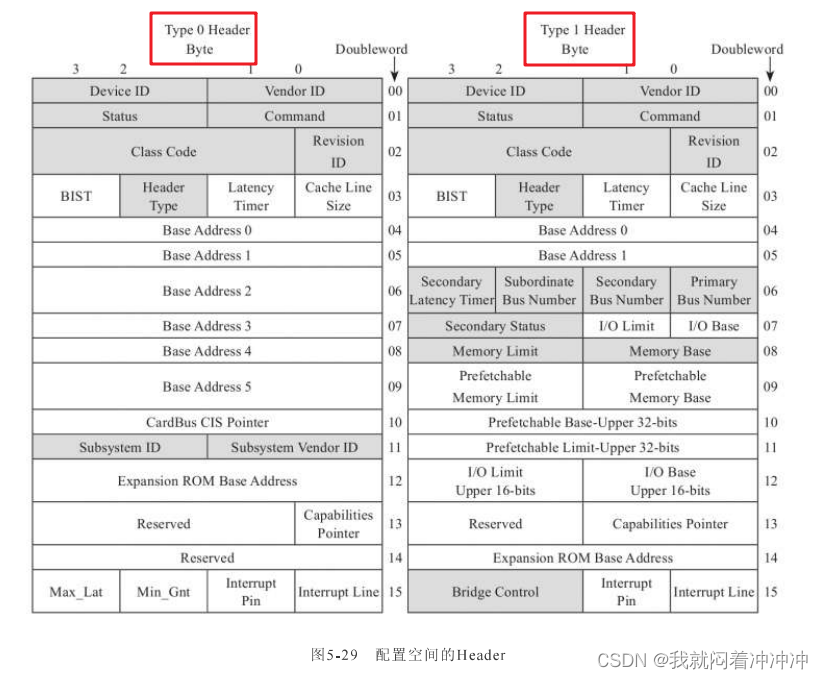

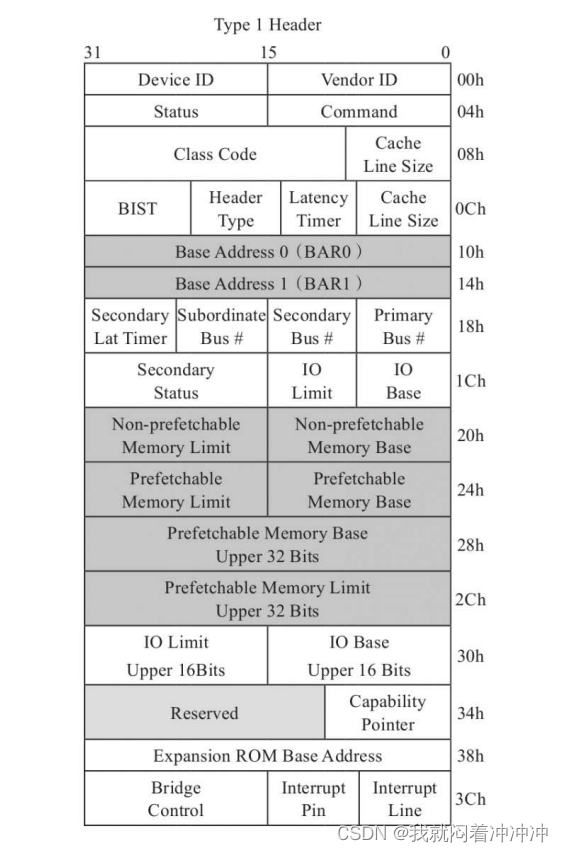

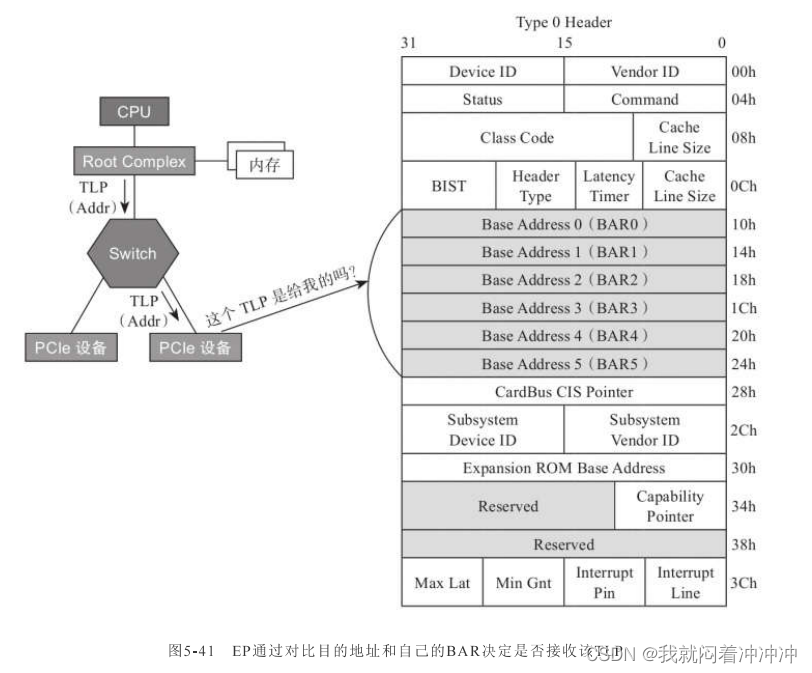

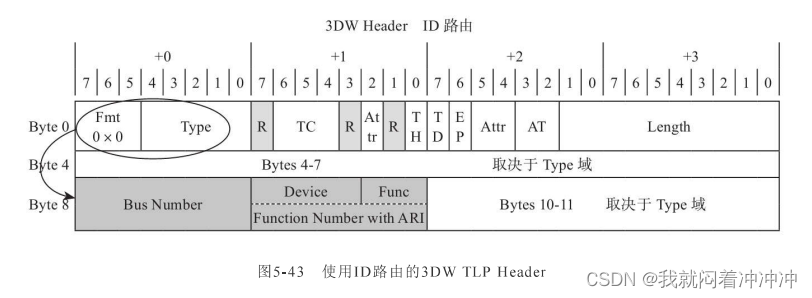

上图中,64byte代表的是Configuration Header。下面看看它的内部(Type 0 Header是Endpoint的Configuration Header,Type 1 Header 是Switch的Configuration Header):

上图中,比较重要的是BAR(Base Address Register),Type 0 提供了6个BAR,Type 1只有2个。BAR是做什么的呢???

答:

在一个PCIe拓扑结构中,一个总线下面可以挂多个设备,而每个设备可以具有几个功能,如下:

在整个PCIe系统中,只要知道了Bus No. + Device No. + Function No. ,就能找到唯一的Function。

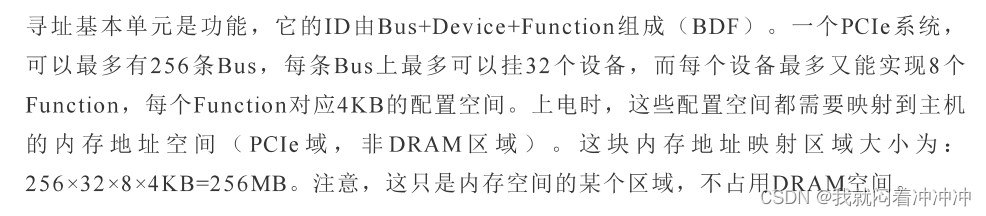

寻址基本单元是功能,它的ID由Bus + Device + Function组成(BDF)。

请注意:只有RC才能发起Configuration的访问请求,其他设备是不允许对别的设备进行Configuration读写的。

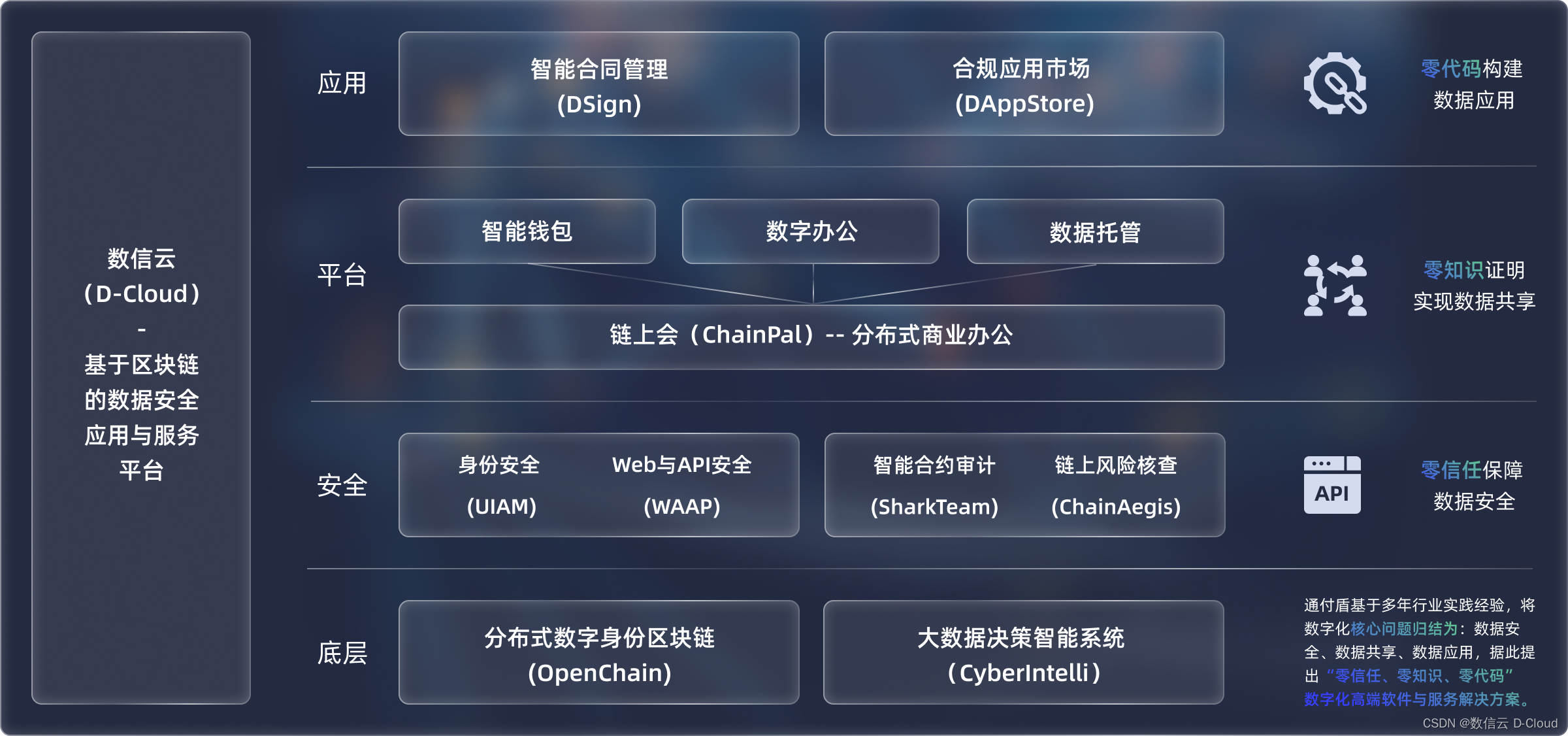

5.7 TLP的路由

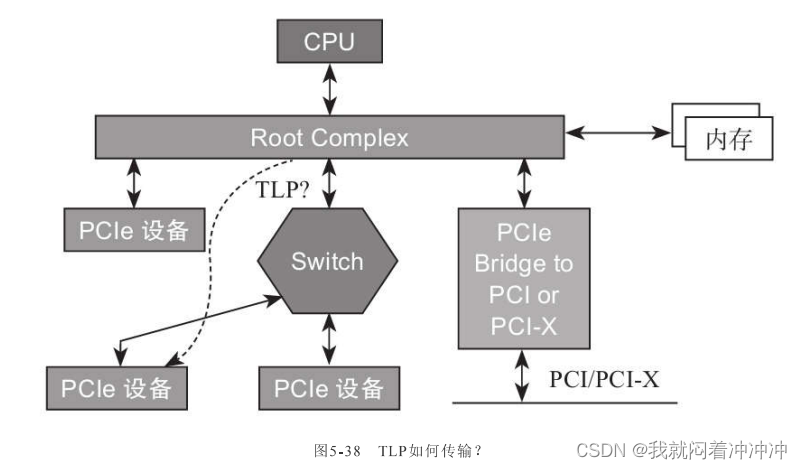

一个TLP是经历了什么后,才能顺利到达目的地的呢??? 以下图为例,讨论一个TLP是怎样从发起者到达接收者,即TLP的路由问题。

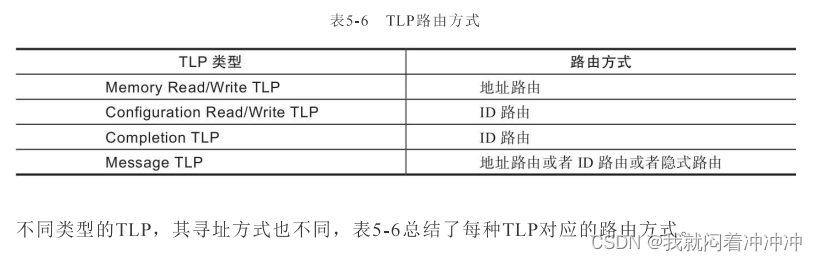

PCIe有三种路由方式:基于地址(Memory Address)路由、基于设备ID(Bus Number + Device Number + Function Number)路由、隐式(Implicit)路由 。

1. 地址路由

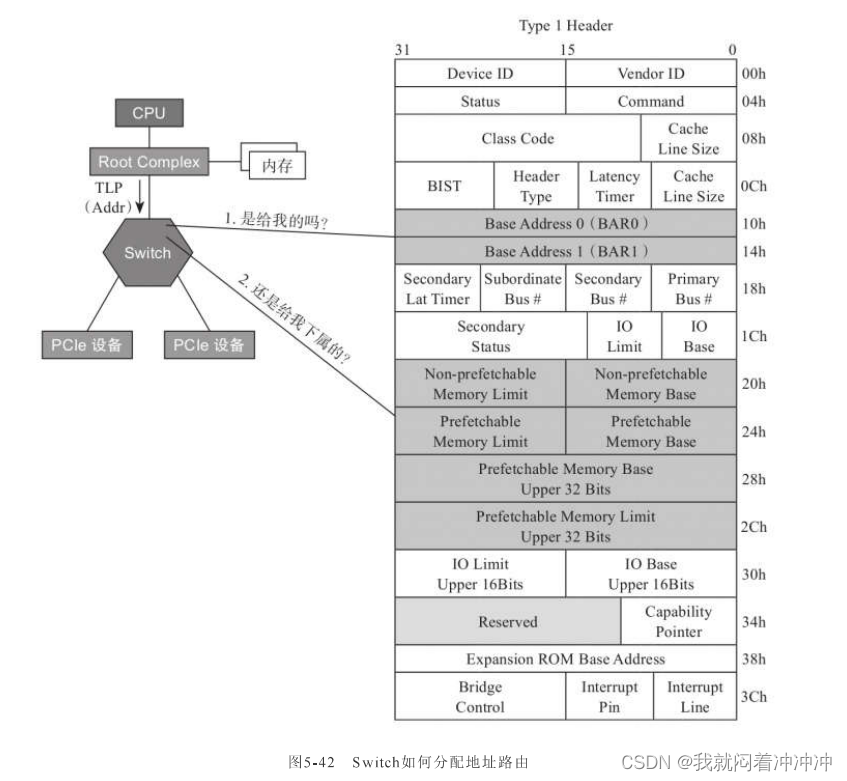

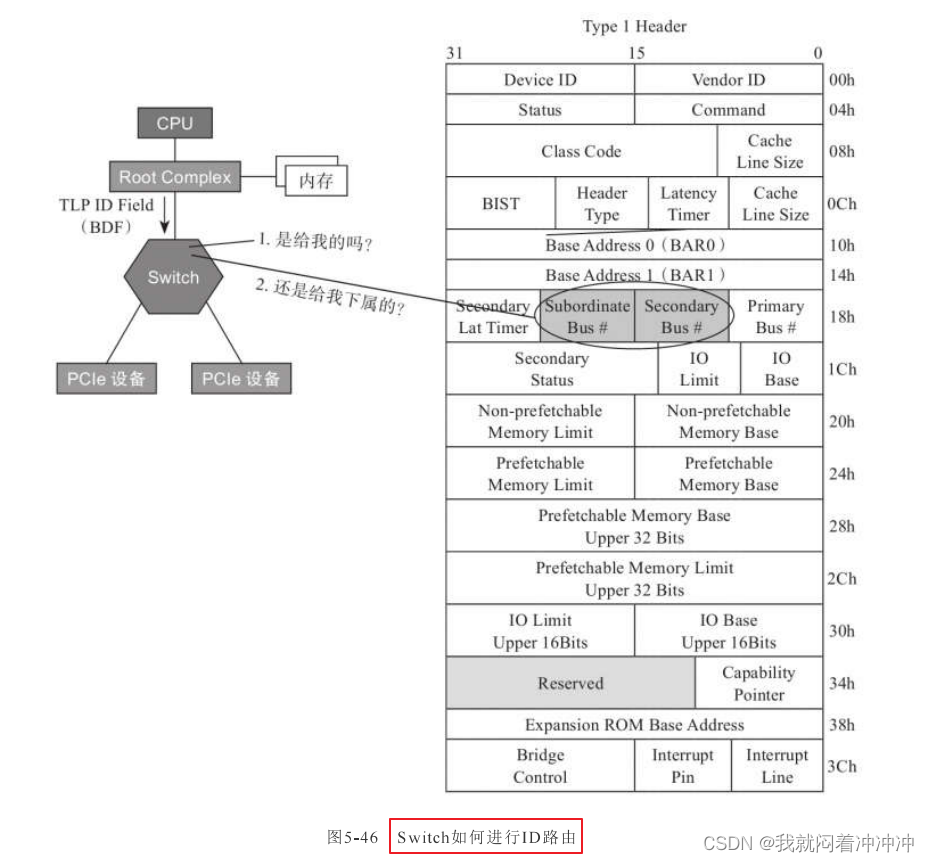

Switch负责路由和TLP的转发,而路由信息是存储在Switch的Configuration空间的。Type 1 Configuration Header如下:

Switch的Configuration中的BAR0 和 BAR1 存放的是Switch内部空间在主机内存空间的映射基址。

Switch有一个上游端口和若干个下游端口,每个端口是一个Bridge,都有一个Configuration,每个Configuration描述了其下面连接设备的空间映射的范围,分别由Memory Base 和 Memory Limit来表示。

根据前文可以知道,Memory Read TLP 或 Memory Write TLP 的Header里都有一个地址信息,该地址是PCIe设备内部空间在内存中的映射地址。

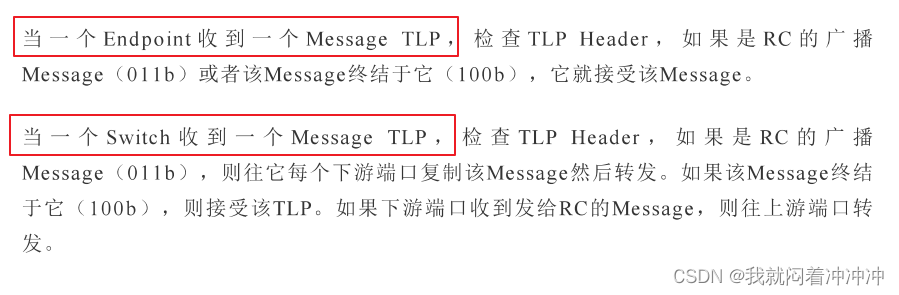

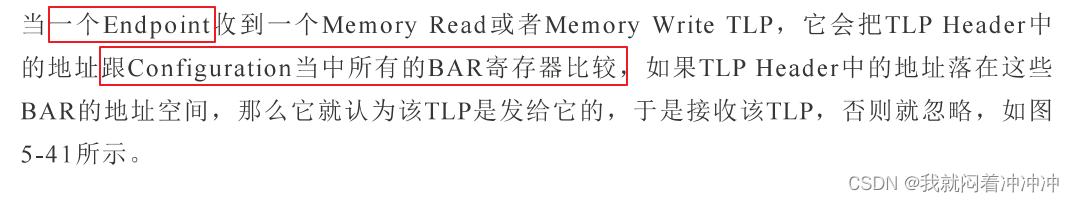

(1)Endpoint收到这样的TLP

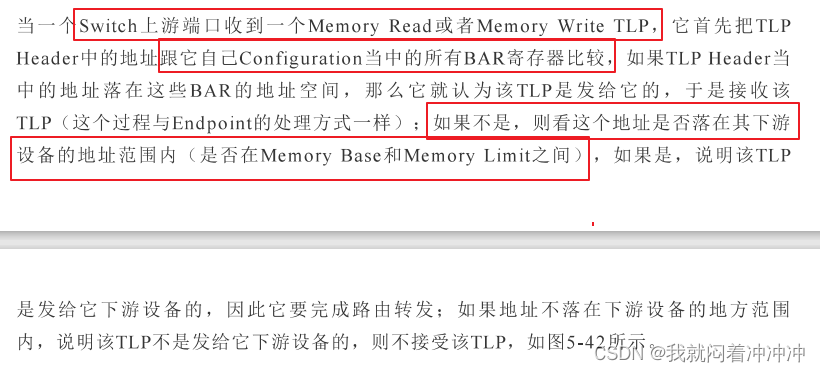

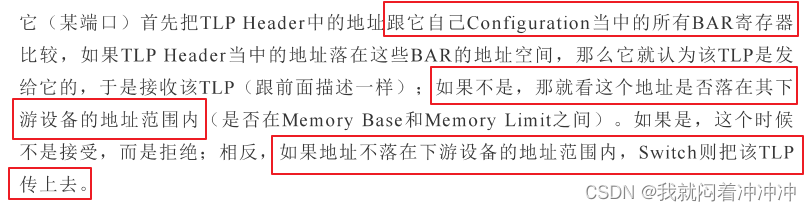

(2)Switch 收到这样的TLP

上面描述的是TLP从Upstream 流到 Downstream 的路由。如果TLP从下游往上游走呢???

2. ID路由

在一个拓扑结构中,由 ID = Bus Number + Device Number + Function Number(BDF)能唯一找到某个设备的某个功能。

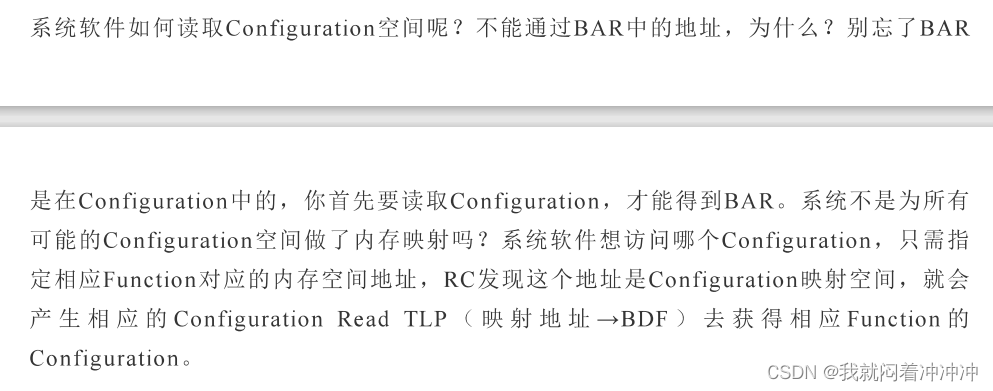

这种按设备ID号来寻址的方式叫做ID路由。Configuration TLP 和 Completion TLP(CplD)按ID路由来寻址,Message在某些情况下也是ID路由来寻址。

使用ID路由的TLP,其TLP Header中包含BDF信息。

(1)Endpoint收到这样的TLP

当一个Endpoint收到一个这样的TLP,它用自己的 ID 和收到TLP Header 中的 Header比较,如果是给自己的,就收下TLP;否则就拒绝。

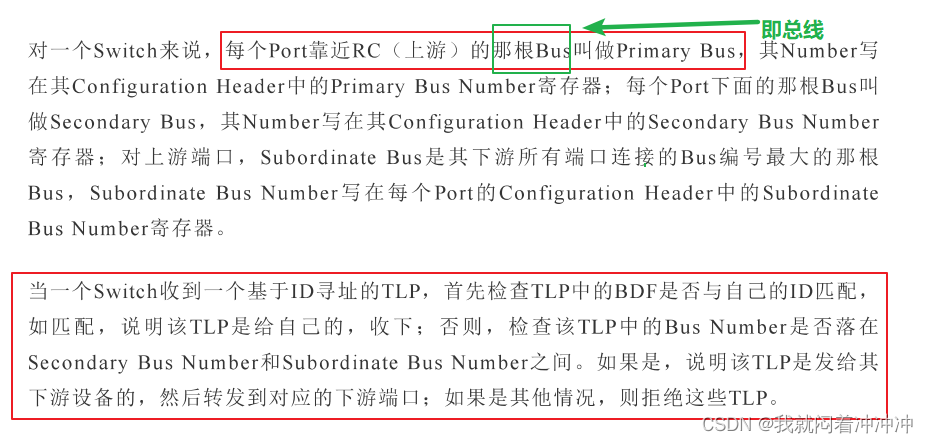

(2)Swtich收到这样的TLP

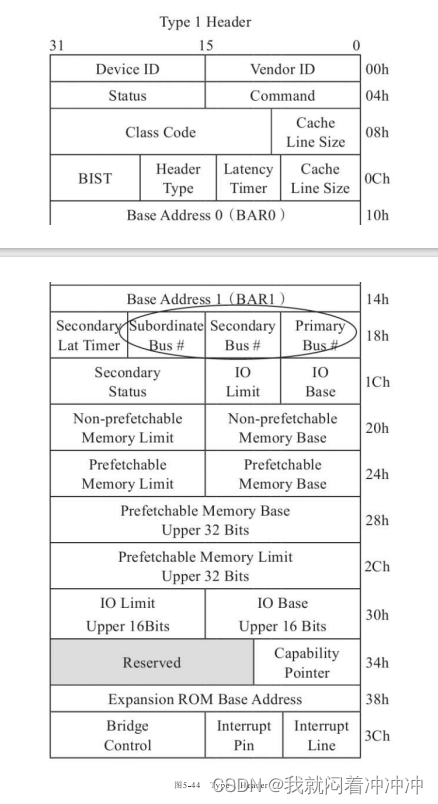

注意:不是一个Switch对应一个Configuration空间,而是Switch的每个Port都有一个Configuration空间。

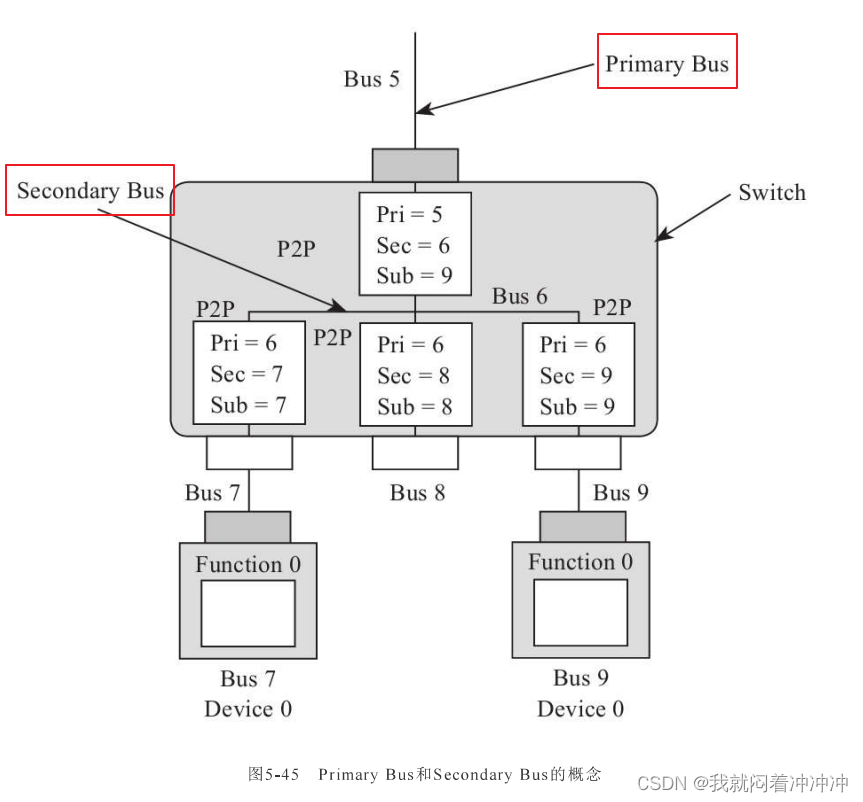

先看看Switch的Configuration Header,如下:

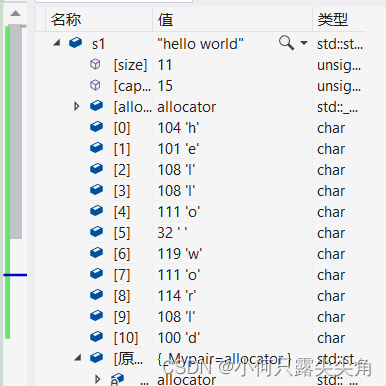

看三个寄存器:Subordinate Bus Number、Secondary Bus Number 和 Primary Bus Number,如下:

3. 隐式路由

只有Message TLP才支持隐式路由。

在PCIe总线中,有些Message是与RC通信的,RC是该TLP的发送者或接收者,因此没必要明明白白的指定地址或 ID ,这种方式叫做隐式路由。

Message TLP 还支持地址路由和ID路由,但以隐式路由为主。

Message TLP 的Header 总是 4DW。如下:

Type字段,低3位,由 rrr 表示,指明该 Message 的路由方式。