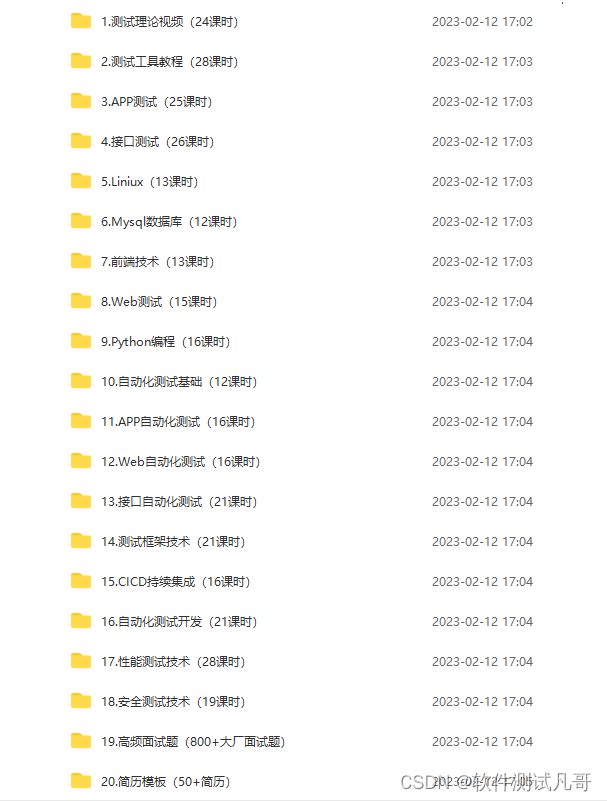

文章目录

- 1.1 Debug Access Port

- 1.2 Access Port

- 1.2.1 IDR 寄存器

- 1.3 Mem-APs 介绍

- 1.3.1 Debug 寄存器访问模型

- 1.3.2 APs 中寄存器的介绍

1.1 Debug Access Port

外部 Debugger(DS-5/Trace32) 会通过JTAG接口或者SWD接口和DAP相连:

JITAG 一般是5个pin:TCK, nTRST(可选), TDI, TDO, TMS

SWD 是两个pin: SWCLKTCK 和 SWDIOTMS(既可以作为JTAG接口TMS接口又可以作为SWD的数据接口)

下图可以看到在DP中有 SWD DP和 JTAG DP,一共两种,中间会有一个选择器(SWD/JTAG select)。

图 1-1

SW-DP 的连接方式是通过 一个时钟线,一个双向的数据线;

SWJ-DP的连接方式是通过五根线:

表 1-1

那么DP如何判断当前连接的是哪种协议呢?

答:SWD 和 JTAG会复用TMS信号线,外部通过TMS发送一定的序列到SWJ-DP,然后再由DP再去根据序列号进行判断,当前传输是JTAG方式还是SWD方式。

1.2 Access Port

ADIv6 specifications 对AP的定义有几点要求:

- 必须有 Identification Register, ADIv5同样要求必须有 IDR寄存器,其偏移地址为0xFC, 并且是AP 寄存器地址空间的最后一个寄存器;ADIv5 规定如果IDR寄存器的值为0,那么表示没有AP存在。

- 任何AP都必须支持DP的访问;

- 所有的AP reserved 寄存器都必须是 RES0

- ABORT 机制是可选的

ADI 支持多个APs,最简单的ADI 只有一个AP,这个AP可以是MEM-AP 或者 JTAG-AP。

ADIs 可以有以下几种情况的AP搭配:

- MEM-AP和JTAG-AP 都有

- 只有MEM-APs

- 只有 JTAG-APs

1.2.1 IDR 寄存器

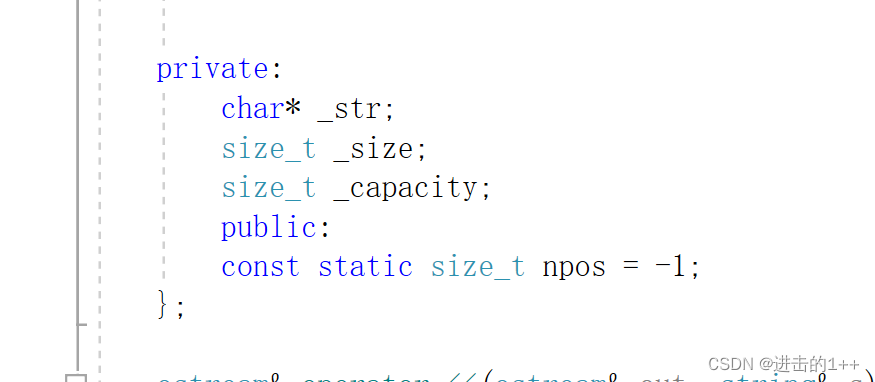

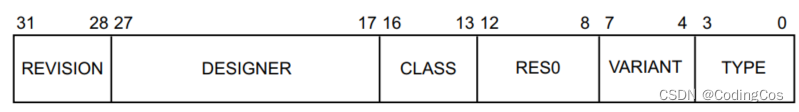

在ADIv5中 IDR 寄存器的定义如下,分为6个域。

bits[31:17] 主要用来显示版本号和公司信息;

bits[16:13] 定义AP所属的类,有以下几种情况:

- 0b0000 No defined class

- 0b0001 COM Access Port(Component AP)

- 0b1000 Memory Access Port

bits[16:13]、bits[7:4]和bits[3:0] 一块定义了AP的类型信息:

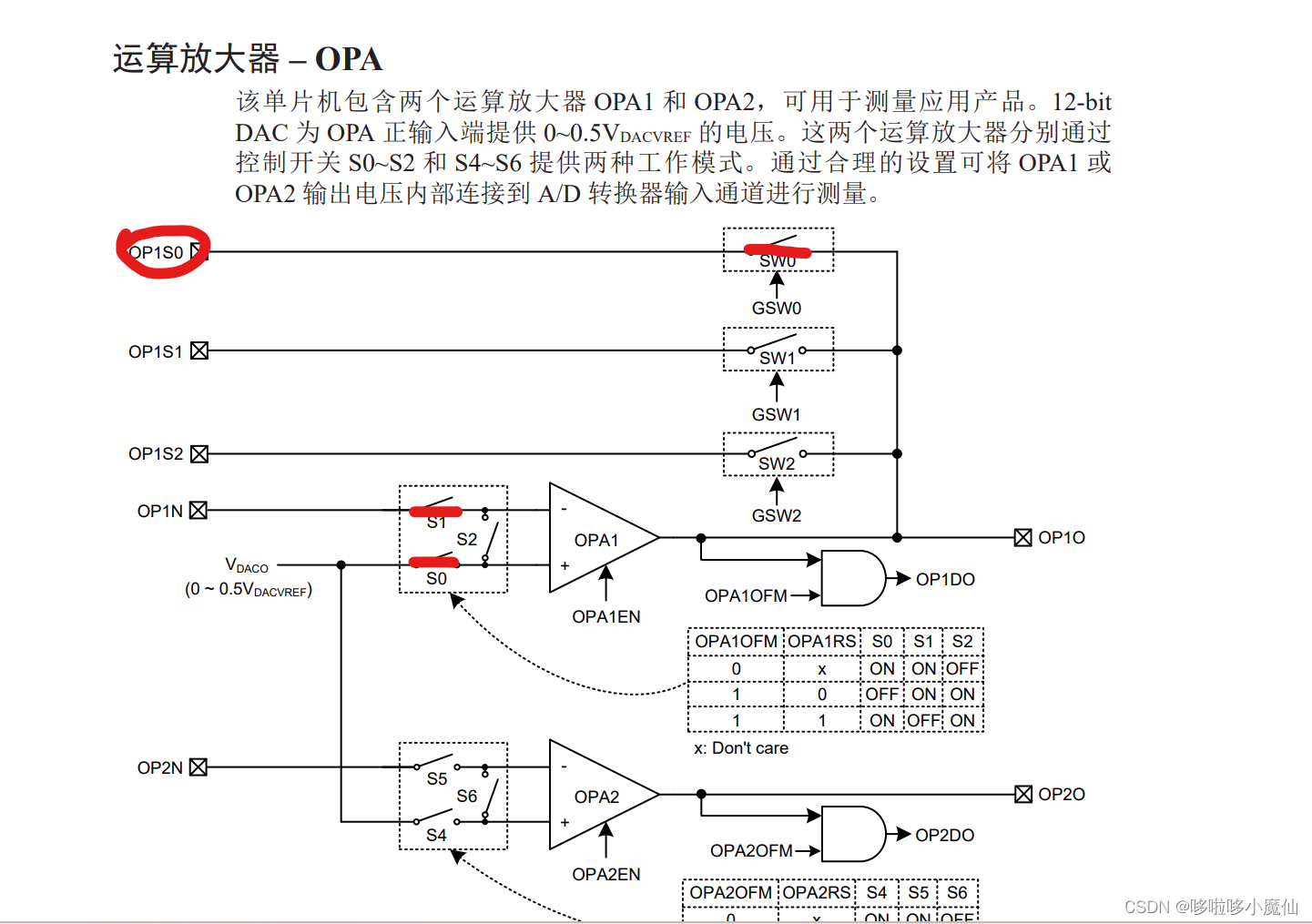

1.3 Mem-APs 介绍

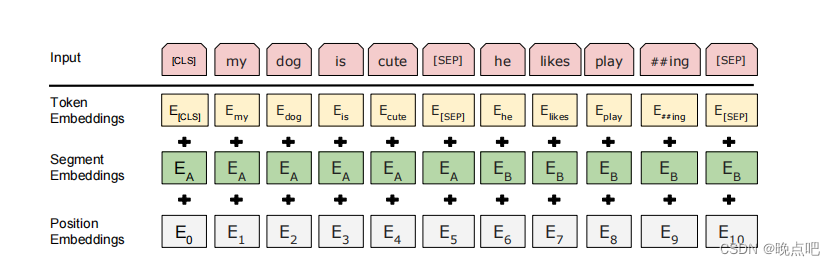

1.3.1 Debug 寄存器访问模型

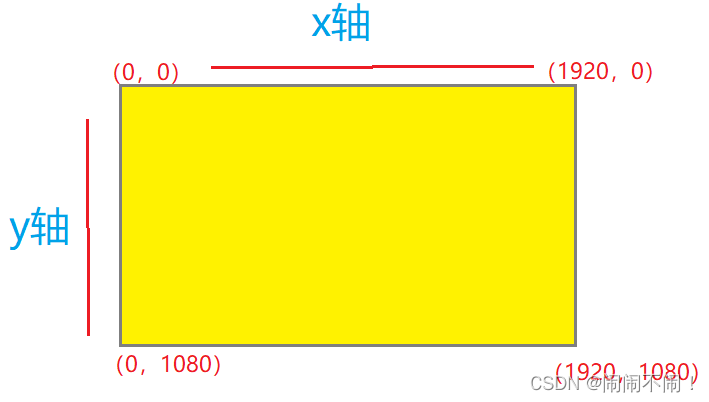

coresight 组件中的寄存器通常会当做外设映射到系统空间,一般会占用4KB的地址空间,当然可以是4KB倍数的地址空间。

对于ARMv8和ARMv9 这种空间粒度的大小可以达到64KB。

ROM Table 可以被看做一组特殊的 debug 寄存器,通常也会占用4KB的地址空间,如果系统中只有一个debug组件连接到AP,这个时候 ROM Table 是可选的,也即硬件可以不实现ROM Table,如果系统中debug 组件的个数超过1个,那么ROM Table 必须实现。

APs 出来的接口可以是 Debug APB,AXI,AHB( 或者JTAG)。

Coresight 图 1-2

- APB Access Port(APB-AP): 一般用于Cortex-A或者Cortex-R Coresight 组件的访问,通常A/R系列会有一个Debug APB的接口;

- AHB Access Port(AHB-AP): Cortex-M系列的 Debug 接口通常是AHB 接口;

- AXI Access Port(AXI-AP): 挂载在系统 memory bus上,可以直接访问到系统memory,比如DDR,SRAM等;

- JTAG Access Port(JTAG-AP): 对

JTAG设备的访问。这个是兼容以前较早的ARM处理器,如ARM9; 这些较早的处理器内部是用 JTAG 来调试的。但是现在的ARM处理器,已经不用这种方式,统一用 memory-mapped 方式进行调试。

1.3.2 APs 中寄存器的介绍

一个 DAP 可以包括多个AP,AP 受 DP 的控制, 只有对 AP 的访问,才可以转化成 memory-mapped 总线,对 SoC 的内部资源进行访问。

根据 TMS 信号线 DP 区分完外部传入的是JTAG还是SWD之后,会去访问 DP 中的 DPACC或者APACC这两个寄存器中的一个 (不管是JTAG还是SWD都是可以访问这个寄存器)。如果访问的是DPACC,那么访问的将是访问DP的一些寄存器;如果访问的是APACC那么,后面将会接着访问AP的一些寄存器。

AP 里面主要有如下几个寄存器:

- CSW(Control/Status Word):用于配置和控制memory interface的transfer;

- TAR(Transfer Address):用于装载当前transfer的地址;

- DRW(Data Read/Write):装载要transfer的数据,如果是读取操作,直接读取这个寄存器即可。

- ROM(Debug ROM Address):装载rom table地址的寄存器;

- IDR(Identification Register):显示当前版本号及memory interface 的类型,如APB-AP,AXI-AP等。

AP出来后 memory interface(memory interface都是有地址的)可以是AXI、AHB 或者APB,memory interface 会将地址配在TAR寄存器中,将数据配置在DRW寄存器中。AP会根据对上面三个寄存器的操作来产生 bus interface 的 transfer。