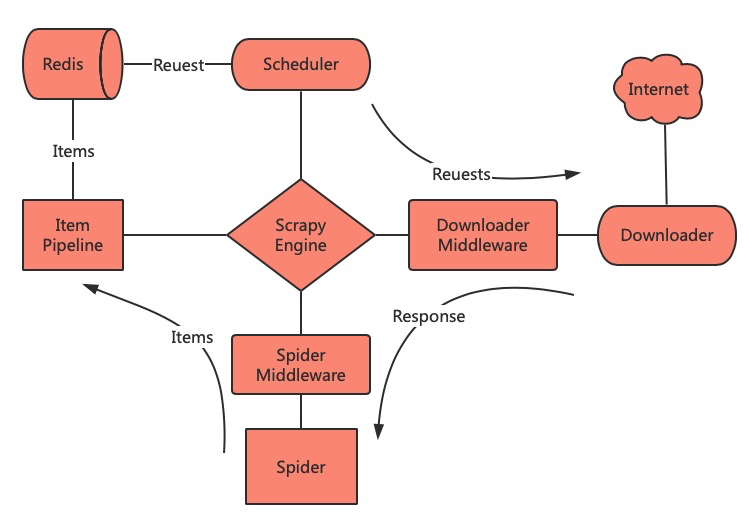

一:xilinx FPGA 在线升级方案:(系统搭建:MicroBlaze软核处理器,uart控制器,Axi-lite-user用户通信接口,MIG DDR3控制器,中断控制器等,以太网控制器)

1.跑一个microblaze,引出一个网口和一个串口。

2.串口实现控制台功能,可以修改本机ip地址。

3.网口有dhcp功能。

4.通过浏览器页面访问microblaze,上传固件,cpu拿到数据后写到flash中,可选做校验。

5.网页做个进度条。

6.可选读出flash内容,指定起始地址和长度。

7.microblaze可访问逻辑寄存器。

8.网页可显示逻辑版本号,即固件版本号

二:流程

设计使用uart接收上位机发送的在线设计程序;在软核中解析uart协议;将烧写程序写到DDR中;利用AXI-LITE用户通信接口,给PL端发送在线更新指令,PL实现将DDR中在线升级程序搬到Flash中。

三:PS端

uart接收数据协议主要在uart接收中断中实现;接收完下载数据后,通过完成标志下发在线更新指令;逻辑收到更新指令,搬运数据到Flash。

四:PL端——PL端接收到在线更新指令,实现将DDR中在线升级程序搬到Flash中

1.设计一个Flash控制器。以便将完成低速数据的存储

2.其中Flash clk管脚配置方法:通过原语STARTUPE2。

3.移植黑金的UART驱动,FLASH(擦除,写,读)代码。

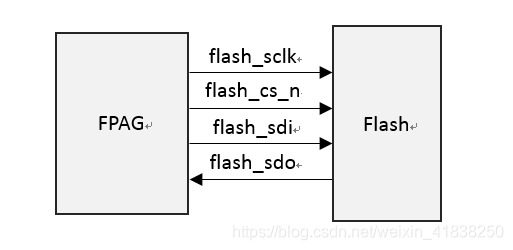

2.1 端口设计

spi_flash_control #(

parameter [31:0] SYSCLK = 32'd100_000_000,

parameter [31:0] SPICLK = 32'd10_000_000

)(

input sys_clk,

input sys_rst,

input cmd_start,

input [31:0] cmd_addr,

input [31:0] wr_data, //write 4 byte

output [31:0] rd_data, //read 4 byte

output reg cmd_done,

output flash_cs_n,

output flash_sclk,

input flash_sdi,

output flash_sdo

);

端口介绍:

cmd_start:发起命令,启动控制器;

cmd_addr:命令与地址;高8bit为命令,低24bit为地址;如果命令与地址无关,则低位为0;

wr_data:写数据;一次写4字节;

rd_data:读数据,一次读4自己;

cmd_done:命令完成,控制器完成一次操作。