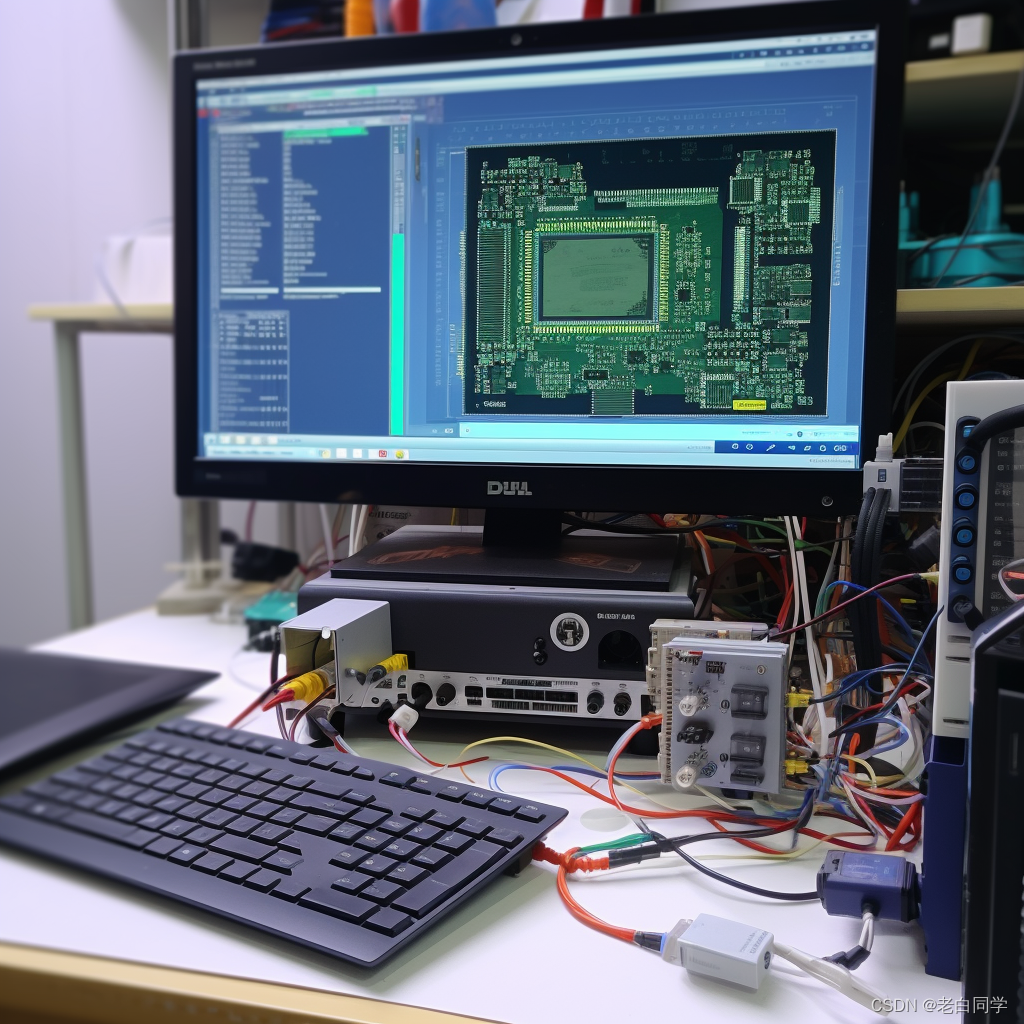

软核工程创建步骤

创建如下工程目录

bin目录:存放SDK工程生成的elf文件(Release编译模式)

hdf目录:存放fpga工程师提供的的hdf文件

prj目录:工程目录(包含SDK工程源码)

doc目录:文档目录

打开Xilinx SDK开发环境,并将workspace目录指向事先建立好的工程目录中的prj目录。

填写工程配置信息。

第一步:选择“Create Applicaton Project”创建一个新的应用工程;

第二步:在“Project name”中填上你的app工程的名字,例如“test_app”;

第三步: 选择你hdf文件,弹出“New Hardware Project”的对话框,接点“Browse..”

选择你的项目的hdf文件(由fpga工程师提供),然后点击“Finish”。

第四步:在“Create New”中填如bsp工程的名称,例如“test_app_bsp”;

第五步:点击“next”进入下一步对话框。

- 在“Templates”对话框中选择“Empty Application”工程,点击“Finish”,完成工程选项配置,等待SDK完成工程创建。

2.SDK工程创建完毕,自动跳转至工作界面,新创建的APP和BSP工程如下图所示。

3.打开prj目录的test_app\src目录。新创建的app工程源码目录中包含lscript.ld和README.txt文件(注意:禁止删除或覆盖lscript.ld文件)。

4.将软件相关代码拷贝到该目录后进行编译。

逻辑HDF文件创建工程编译错误问题解决方式

解决措施:

逻辑重新生成HDF文件进行编译。

FPGA虚拟串口调试步骤

解决措施:

通过仿真器远程连接的方式打印调试信息,调试步骤如下:

(1)在windows命令行界面输入以下命令,启动服务程序

C:\Xilinx\Vivado\2018.2\bin\hw_server.bat

按下图所示打开SDK调试窗口:

在上图红框处依次输入以下命令:

(2)连接服务(ip地址为SDK运行主机的IP)

connect -host 192.168.*.* -port 3121

(3)下载fpga bit文件(bit文件路径根据实际情况设置)

fpga {D:\test.bit}

(4)查看软核目标号

targets,例如:

xsct% targets

1 xc7k325t

3 MicroBlaze Debug Module at USER2

4* MicroBlaze #0 (Running)

2 Legacy Debug Hub

(5)输入目标

targets 4

(6)打开仿真器打印窗口

jtagterminal –start

(7)下载elf程序到软核

dow {D:********\test.elf}

(8)运行软核程序:

con

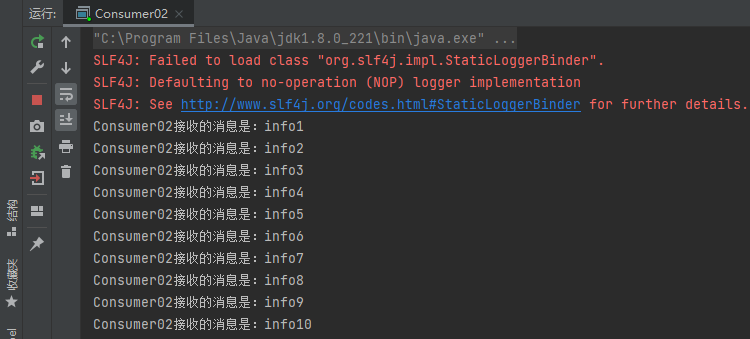

此时可以在打印窗口查看调试信息

此时如果依然没有打印信息需要配置mdm串口:

stdin 和stdout都选mdm_0

Fpga产生发送参考时钟错误

调试console输入jmHdmiMenu “i”查看输出参考时钟,TX无参考时钟(即输入的像素时钟)

从VPHY log上也能看出,没有时钟事件产生

原因:FPGA时钟频率和就绪信号设置错误。

解决措施:Fpga参考时钟频率需要设置成像素时钟,例如输出1920x1080@60的视频需要设置成148.5M,发送参考时钟设置正确后VPHY打印调试信息如下:

但此时发送参考时钟依然没有锁定:

(2)需要根据FPGA锁定方式是高电平有效还是低电平有效来修改时钟就绪信号设置方式,本项目需要将就绪信号GPIO先置高再置低:

上面代码addr为FPGA GPIO地址:

FPGA通过I2C接口配置Si5324时钟芯片产生发送参考时钟,Si5324时钟无输出

I2C接口无输出解决措施:

修改FPGA i2c 配置,重新生成HDF文件。

问题现象:采用新的HDF文件编译运行,FPGA的I2C接口有信号输出,同时没有报以上错误,但SI5324依然无时钟输出。

原因分析:Si5324时钟芯片配置错误,这个错误可能是由于软件配置错误也可能由于硬件电路错误导致。

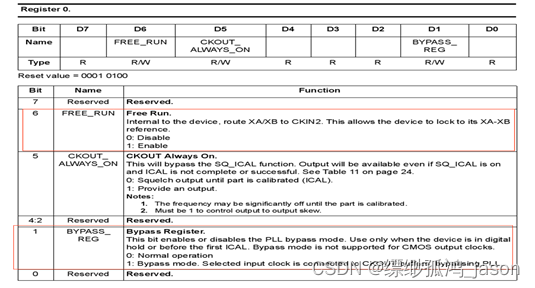

通过查看Si5324芯片手册《si53xx-reference-manual》108页,如下所示:如果晶振输入频率为114.285M,时钟芯片RATE[1:0]引脚需要配置成MM模式。

查看《SI5324C-C-GM.pdf》手册60页可知RATE[1:0]默认为M模式,

因此硬件电路上需要去掉下图的配置电阻,如下图所示,硬件上可以通过测量引脚电压是否为VDD/2来确认。

问题现象:硬件修改完RATE[1:0]电阻后依然没有时钟输出

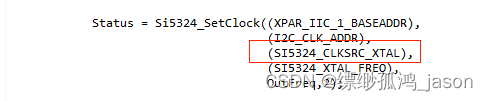

机理分析:查看代码Si5324输入时钟源选择的是外部晶振,如下所示:

读取Si5324寄存器值如下:

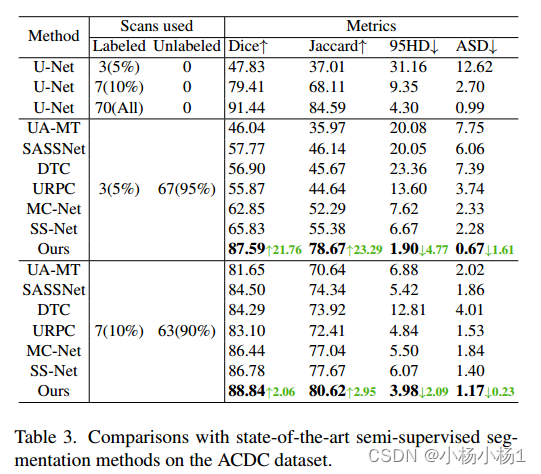

从上图可知寄存器7的值为2A,阅读《SI5324C-C-GM.pdf》寄存器说明文档,30页

从寄存器值来看时钟源配置的是CKIN2,查看时钟设置代码:

....

寄存器7确实没有进行配置,从代码看寄存器0配置成了0x54,寄存器11配置成了0x40。

读取对应寄存器值如下:

查看《SI5324C-C-GM.pdf》手册寄存器说明如下:

当前模式时钟输入CKIN1和CKIN2都disable了,将XA/XB晶振路由到CKIN2作为时钟输入。

通过查看寄存器1说明,将第1位置1可以设置成BYPASS模式,将晶振输入的时钟直接输出,如下所示:

此时通过示波器量可以量到频率为38.8M的时钟输出信号,因此确认此时晶振输入的时钟频率确实只有38.8M。

将时钟设置代码中输入频率由114.285M改为38.8M,0寄存器还是设置成0x54,修改如下所示:

此时示波器量输出时钟评率为148.5M,时钟可正常输出。

考虑相同软件配置其他项目有时钟输出,对比硬件原理图发现晶振电容改了,导致晶振输出时钟只有38.8M而非114.285M。

考虑相同软件配置mwg6422项目有时钟输出,对比6422硬件图发现晶振电容改了,导致晶振输出时钟只有38.8M而非114.285M。

把C1081和C1086改成18pf

将电容替换后,晶振输出时钟频率为114.285M,此时将代码中输入频率SI5324_XTAL_FREQ改回114285000测试,Si5324可正常输出148.5M时钟。

FPGA HDMI输出接口有时钟输出依然无彩条显示

问题现象:软核程序无错误打印信息,示波器可以量到HDMI输出时钟,但显示器依然不能显示彩条

原因分析:

HDMI信号质量问题,需要配置均衡器

解决措施:

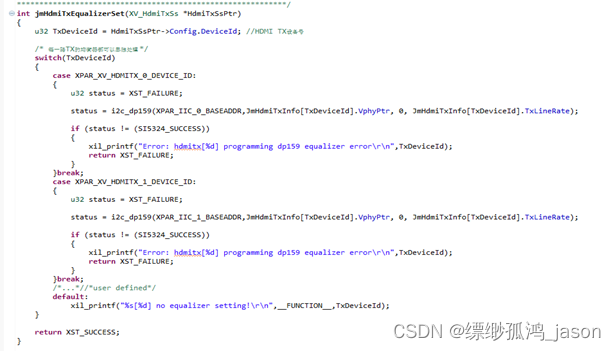

软核增加dp159均衡器配置代码:

JTAG在线调试设置步骤

1、点击虫子旁的下拉键,点击Debug Configurations…

2、弹出如下窗口:

双击(System Debugger),Target Setup选项配置如上图,如果要烧写fpga bit文件需要勾选 program FPGA选项。

3 、点击Application选项,勾选下图选项,提供要停留在main函数入口,勾选Stop at ‘main’选项。

4、 点击Debug开始在线调试,可以在Console控制台窗口查看调试信息,或者输入shell命令进行调试。

替换hdf文件

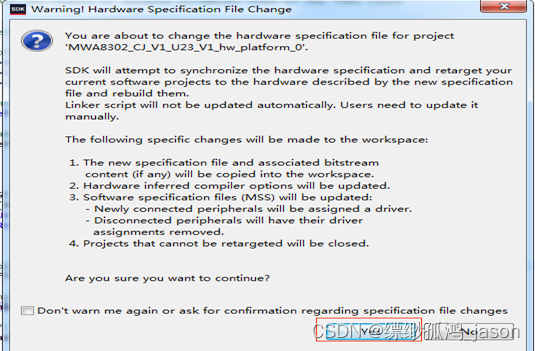

鼠标右键点击下图红色框文件夹弹出窗口中选择红色框选项

弹出以下窗口选择yes

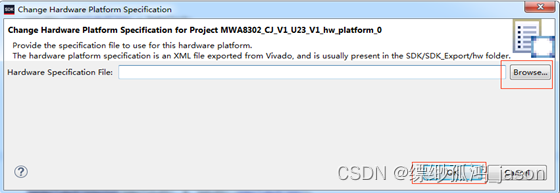

弹出以下窗口,选择hdf文件点击ok按钮。

替换完hdf文件后最好把整个工程重新编译下。

打印接口问题

Xil_printf接口打印不了浮点数,有时候打印只会出错,最好直接用prinf接口。

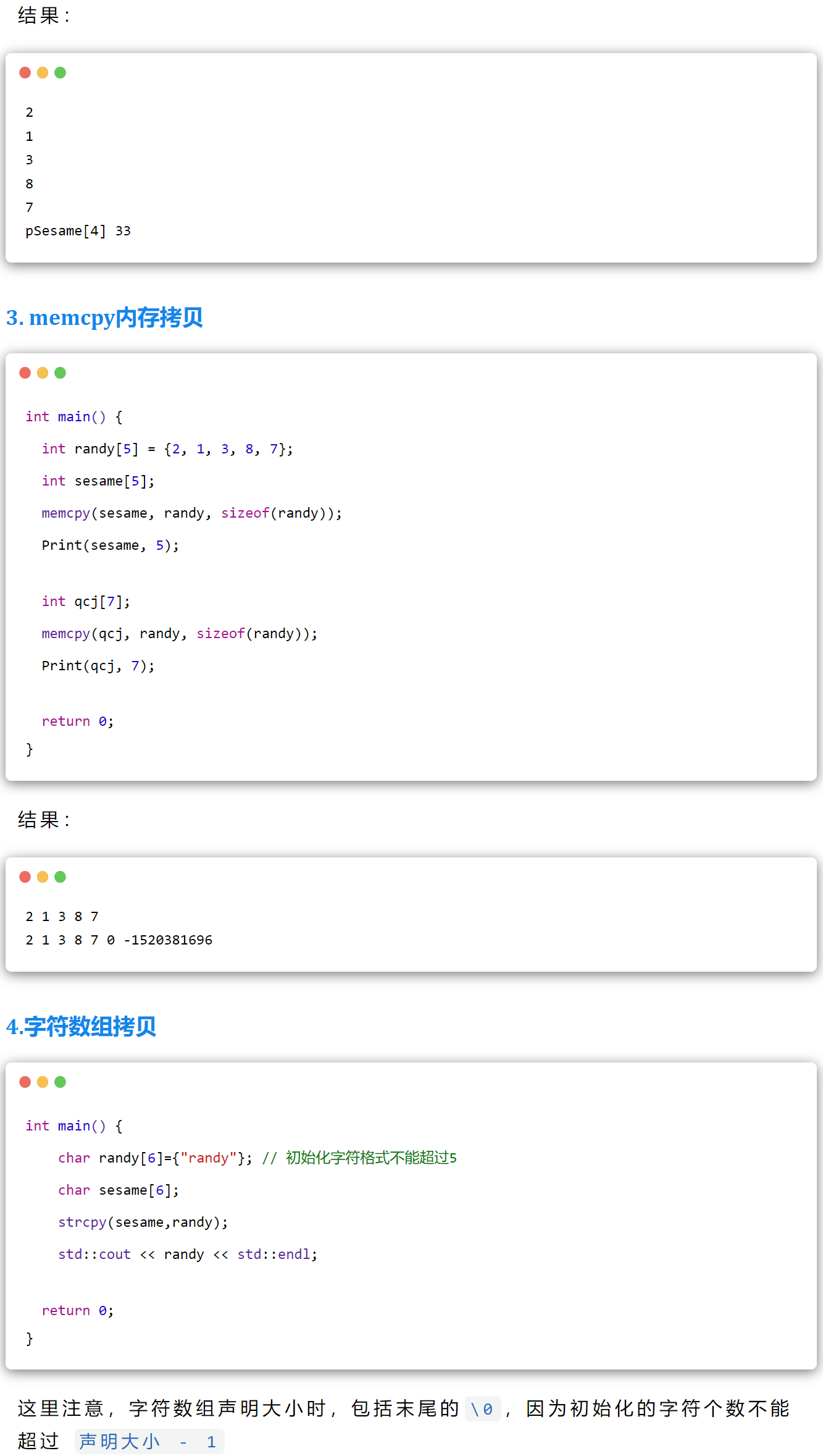

内存设置

通过lscript.ld文件以下参数设置堆和栈空间大小:

通过lscript.ld文件以下参数设置bram和ddr内存空间大小:

通过lscript.ld文件以下参数设置软件运行在bram还是ddr内存空间:

如果代码运行在Bram空间选择:

microblaze_0_local_memory_ilmb_bram_if_cntlr_Mem_microblaze_0_local_memory_dlmb_bram_if_cntlr_Mem。

如果代码运行在ddr空间选择:

mig_7series_0_memaddr。

静态库工程创建

选择file->New->Project

选择Library Project点Next

填写工程名Project name

选择库类型Library Type,例如静态库选static Library

选择操作系统类型OS Platform,例如无操作系统选standalone

选择处理器类型Processor,例如软核选microblaze

然后点Finish创建

工程创建成功后在src目录添加库文件代码,进行编译即可生成名称为libtestlib.a的库文件。

库文件调用

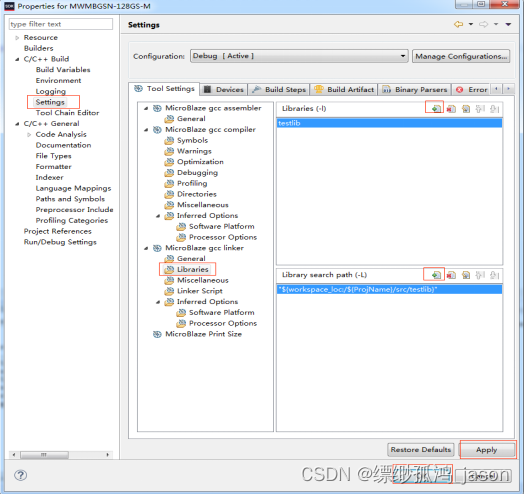

将对应的库文件放入工程所在目录,例如src下的lib目录中,然后设置库名和路径,选中工程点击右键,选择Properties

选择Settings->Libraries

选择Libraries(-l)后的“+”添加库,库名称和gcc链接库规则相同,前面的lib不需要。

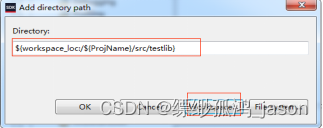

选择Library serach path(-L)后的“+”添加库文件所在路径,点击workspace选择路径。