系列文章目录

一、FPGA学习笔记(一)入门背景、软件及时钟约束

二、FPGA学习笔记(二)Verilog语法初步学习(语法篇1)

三、FPGA学习笔记(三) 流水灯入门FPGA设计流程

四、FPGA学习笔记(四)通过数码管学习顶层模块和例化的编写

五、FPGA学习笔记(五)Testbench(测试平台)文件编写进行Modelsim仿真

六、FPGA学习笔记(六)Modelsim单独仿真和Quartus联合仿真

七、FPGA学习笔记(七)verilog的深入学习之任务与函数(语法篇3)

八、FPGA学习笔记(八)同步/异步信号的打拍分析及处理

九、FPGA学习笔记(九)SPI学习总结及stm32的HAL库下SPI配置

文章目录

- 系列文章目录

- PLL锁相环

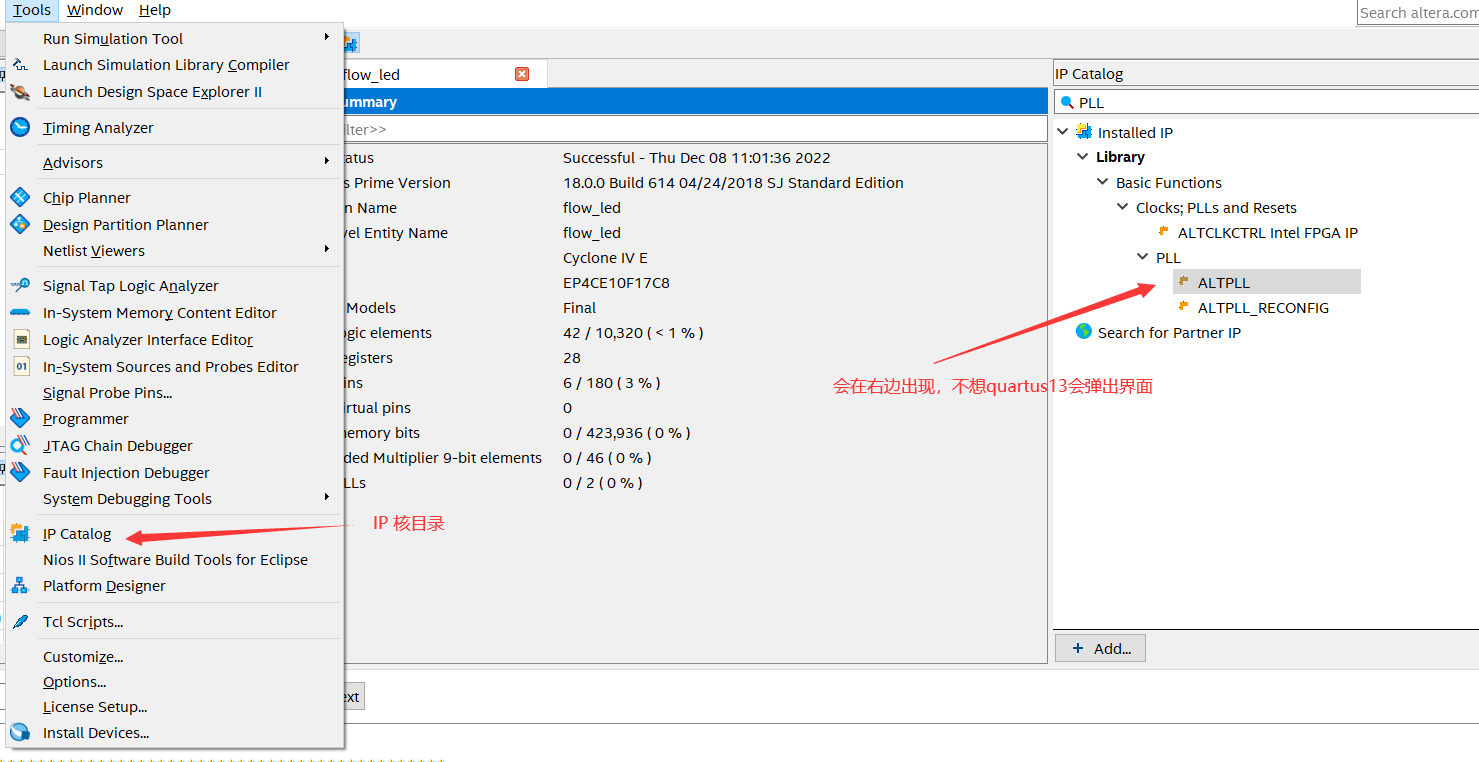

- quartus13的使用方法

- quartus 18的使用方法

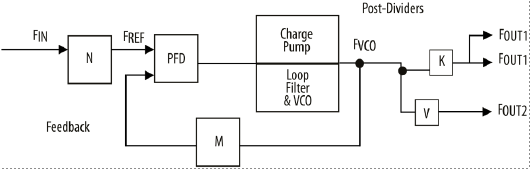

PLL锁相环

锁相环工作中,当输出信号的频率与输入信号的频率相等时,输出电压与输入电压保持固定的相位差值,即输出电压与输入电压的相位被锁住,这就是锁相环名称的由来。

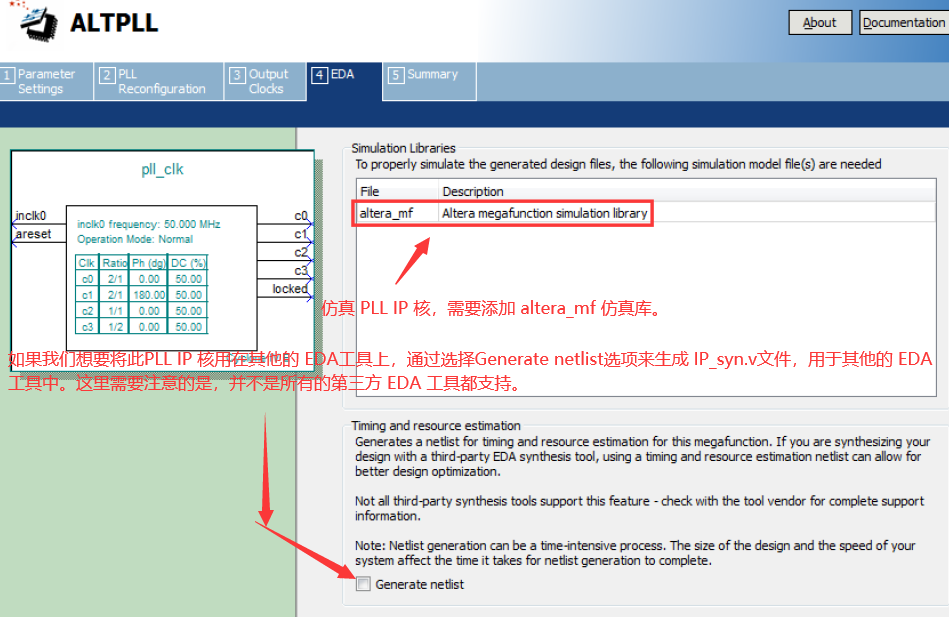

Quartus II软件提供了锁相环PLL的IP核,具有时钟倍频(*2)、分频(/2)、相位偏移(0-360°)和可编程占空比的功能。

具体工作原理就不讨论了,看看怎么使用?

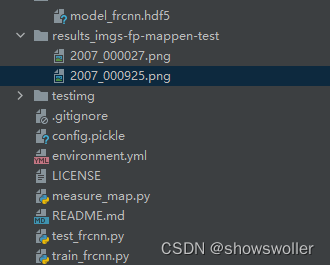

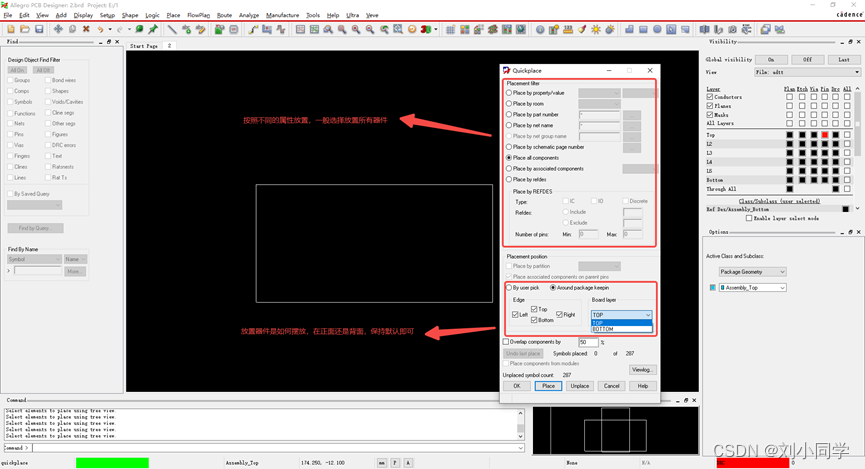

quartus13的使用方法

插件管理:帮助你创建或修改包含自定义变化的设计文件。

创建新的

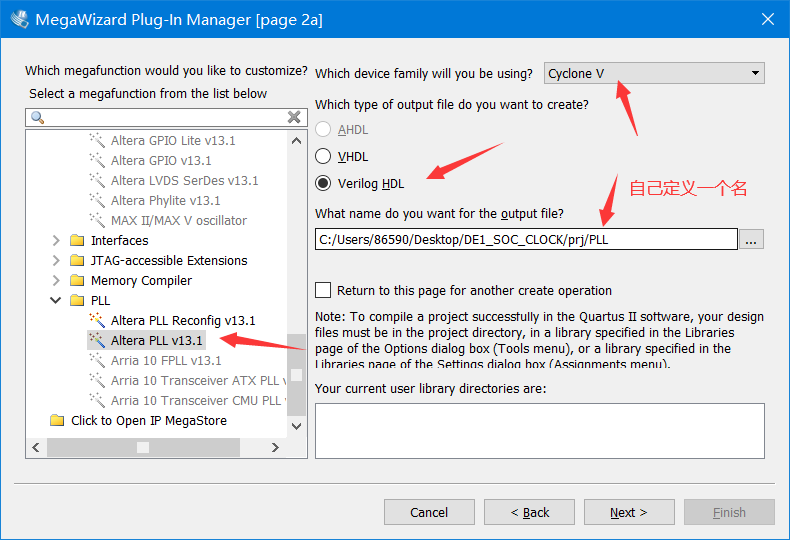

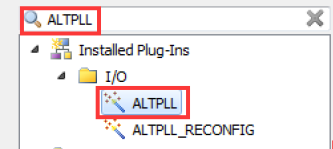

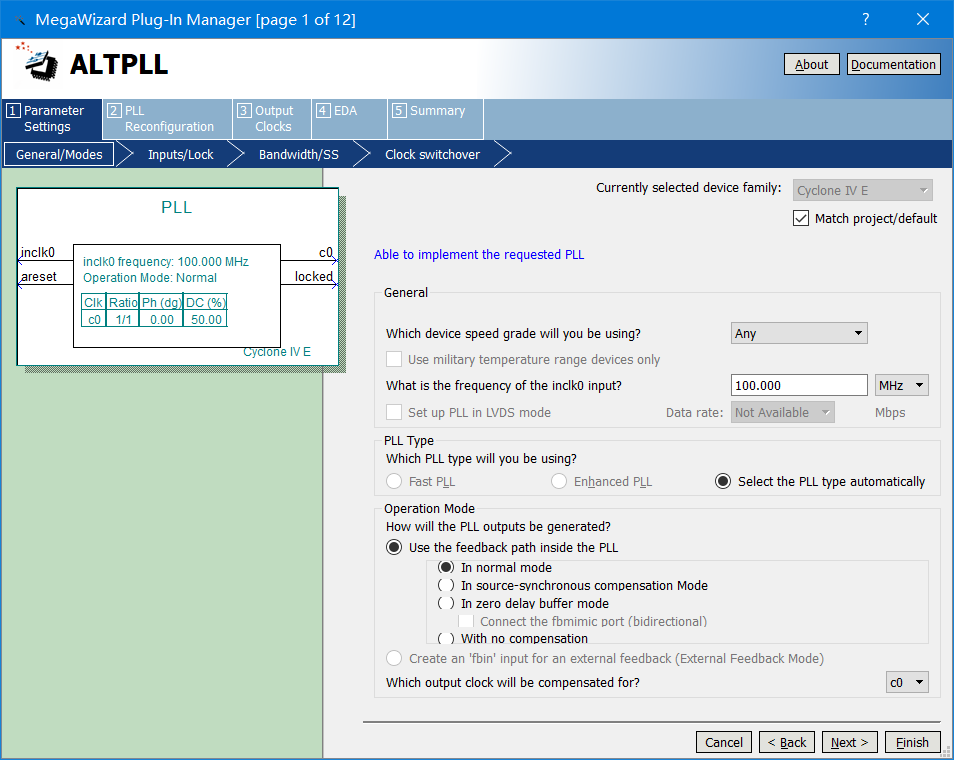

上图应该选ALTPLL IP 核,这个板子没有

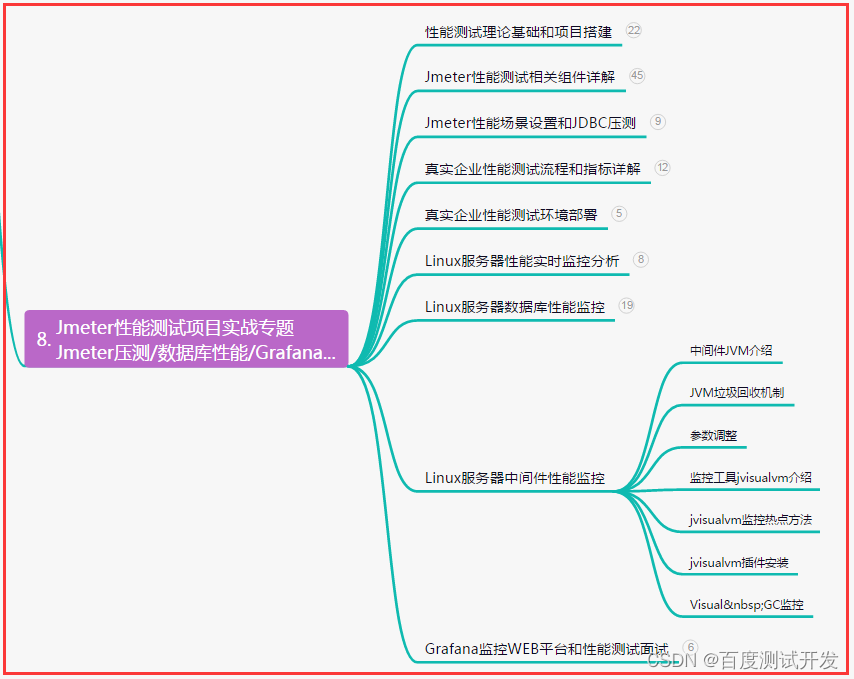

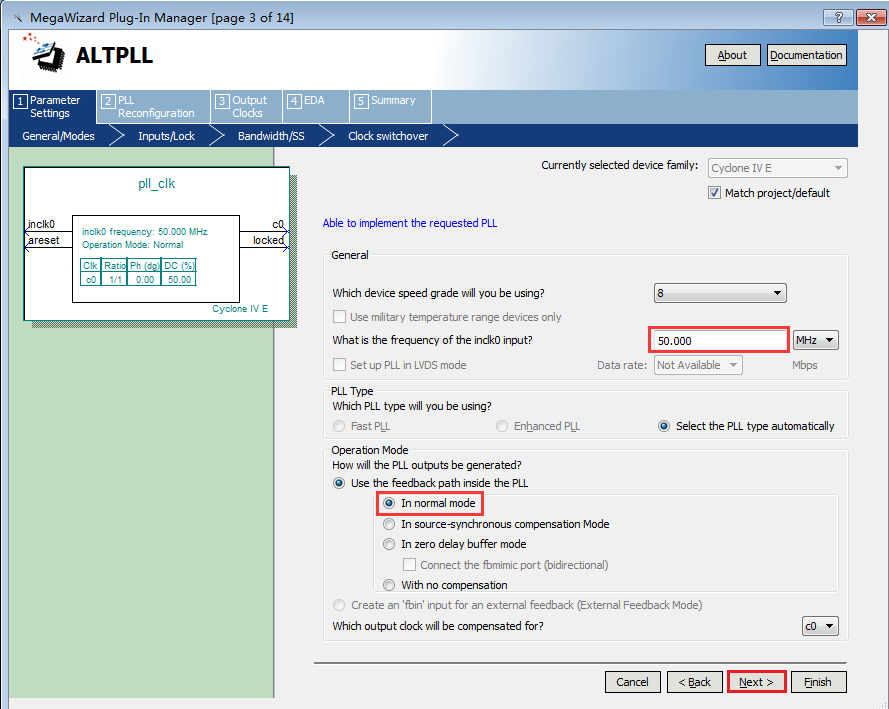

In normal mode(正常模式):PLL 反馈路径源是全局或局域时钟网络,可以最小化时钟类型和指定 PLL寄存器的时钟延时,还可以指定补偿的 PLL 输出。

In source-synchronous compensation mode(源同步模式):数据和时钟信号同时到达输入引脚。从引脚到 I/O 输入寄存器之间的时钟延时与从引脚到 I/O 输入寄存器之间的数据延时匹配,信号可以确保在任何输入/输出使能寄存器的时钟和数据端口有相同的相位关系。

In zero delay buffer mode(零延时缓存模式):PLL 反馈路径限制在专用 PLL 外部输出引脚上。片外驱动的 PLL 反馈路径与时钟输入是相位对齐的,且时钟输入和外部时钟输出之间的延时最小。

Witch no compensation(外部反馈模式):PLL 补偿到 PLL 的反馈输入,这样可以最小化输入时钟和反馈时钟引脚之间的延时。

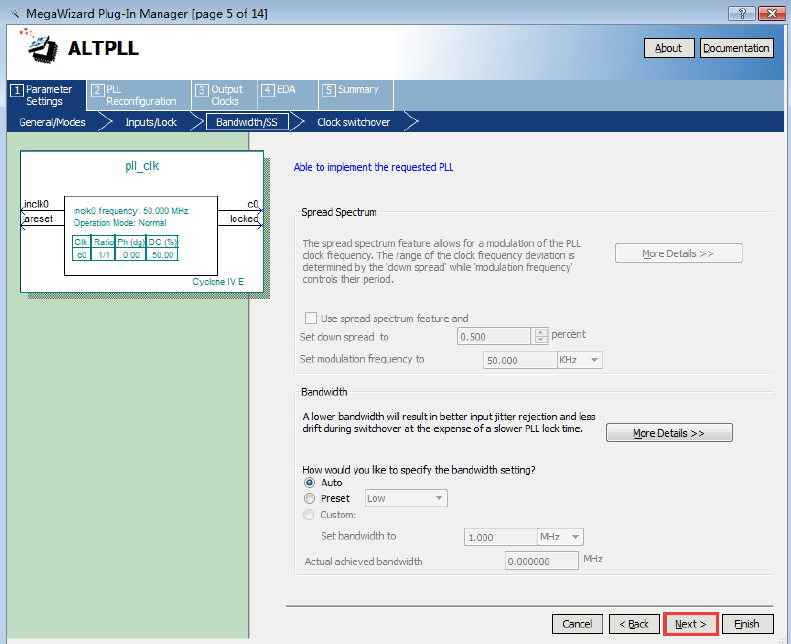

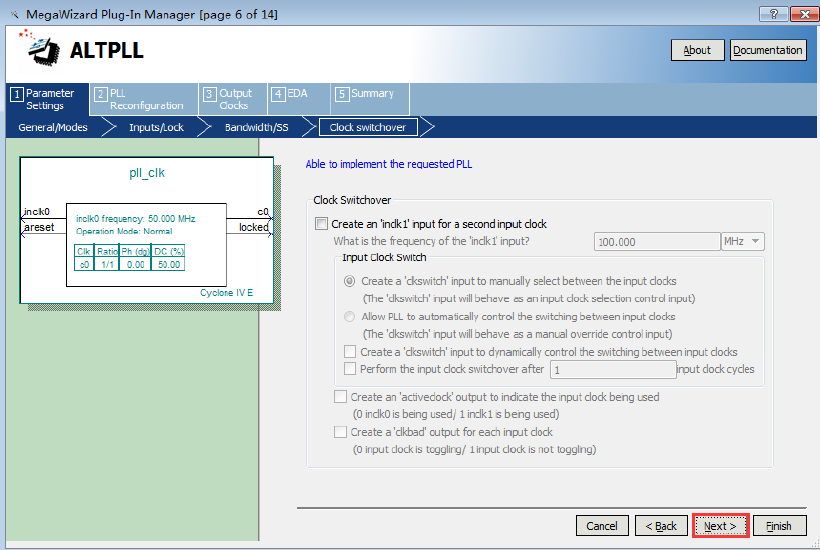

上图是时钟转换配置页面是配置另一个时钟输入源

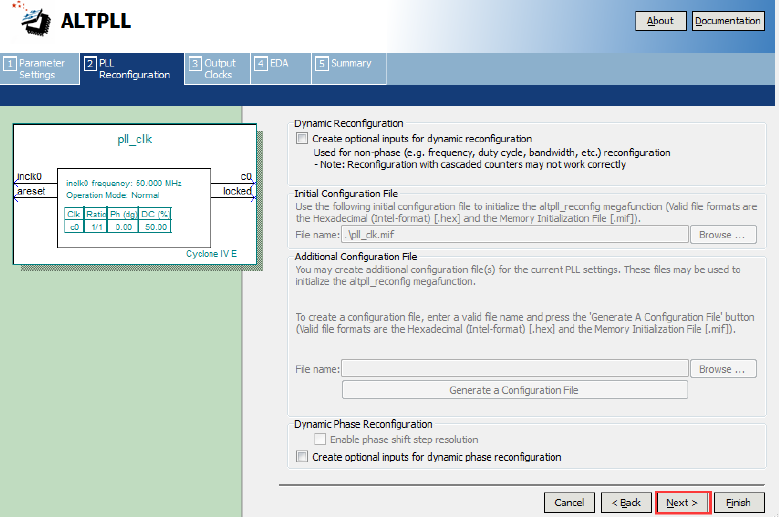

上图中的页面是选择动态配置 PLL 输出,实现在线的实时配置,我们使用的时钟输出一般都是固定频率的,所以不需要选择

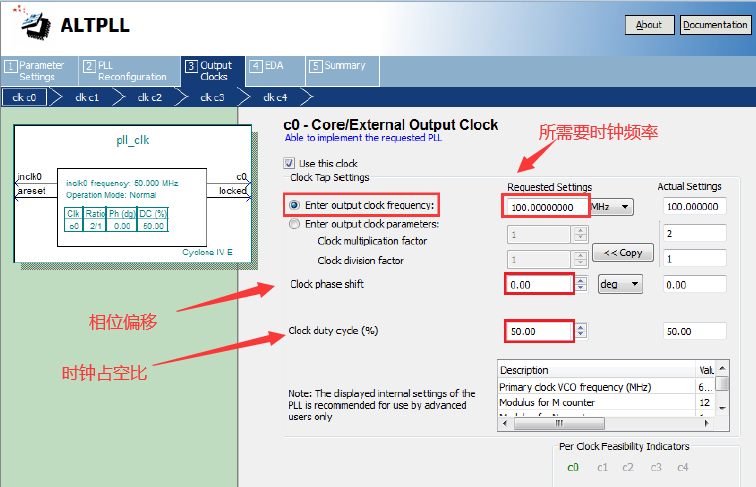

这里设置的是输出c0,还有c1…

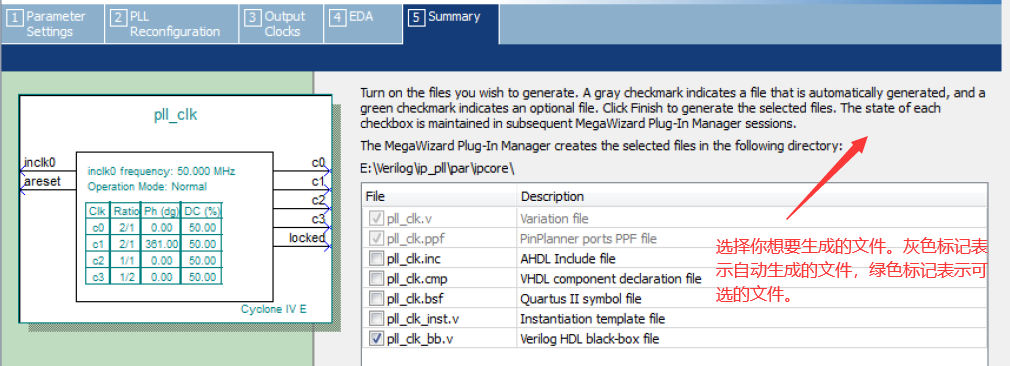

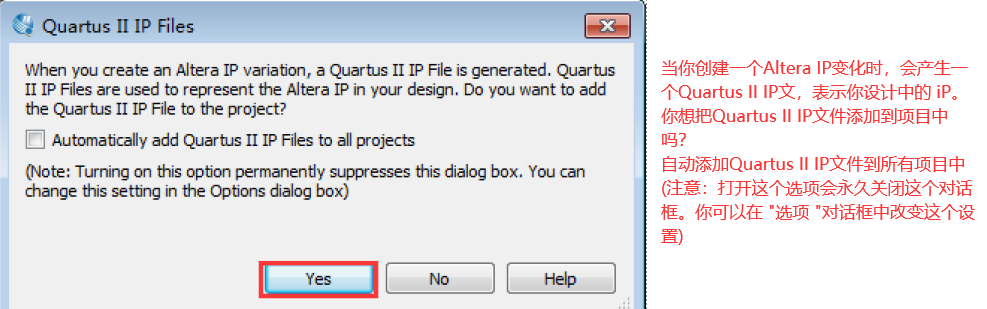

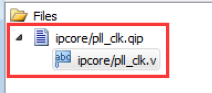

qip :Quartus IP 的缩写

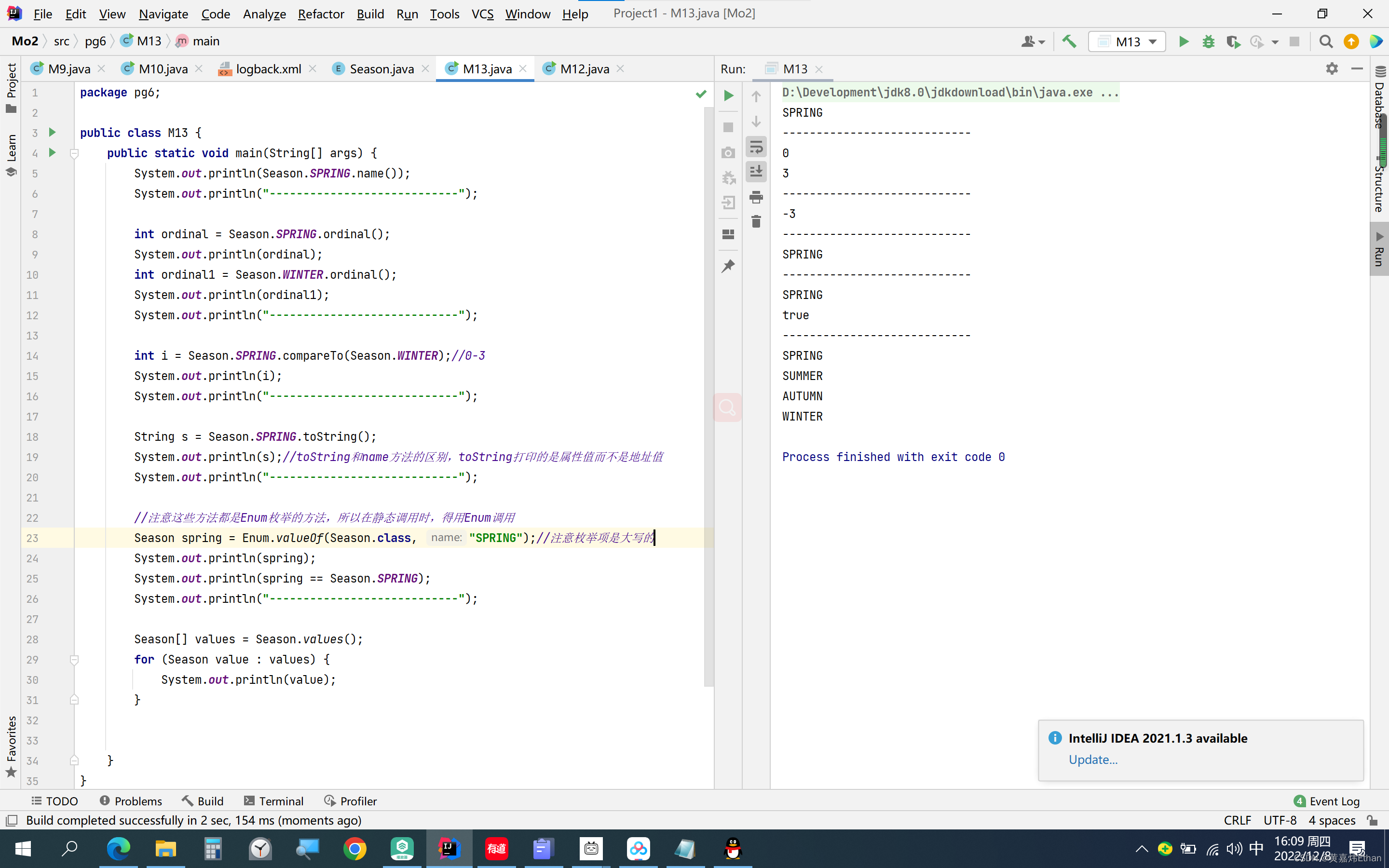

module ip_pll(

input sys_clk , //系统时钟

input sys_rst_n , //系统复位,低电平有效

output clk_100m , //100Mhz时钟频率

);

wire rst_n ; //复位信号

wire locked ; //locked信号拉高,锁相环开始稳定输出时钟

//系统复位与锁相环locked相与,作为其它模块的复位信号

assign rst_n = sys_rst_n & locked;

//锁相环

pll_clk u_pll_clk(

.areset (~sys_rst_n ), //锁相环高电平复位,所以复位信号取反

.inclk0 (sys_clk ),

.c0 (clk_100m ),

.locked (locked )

);

endmodule

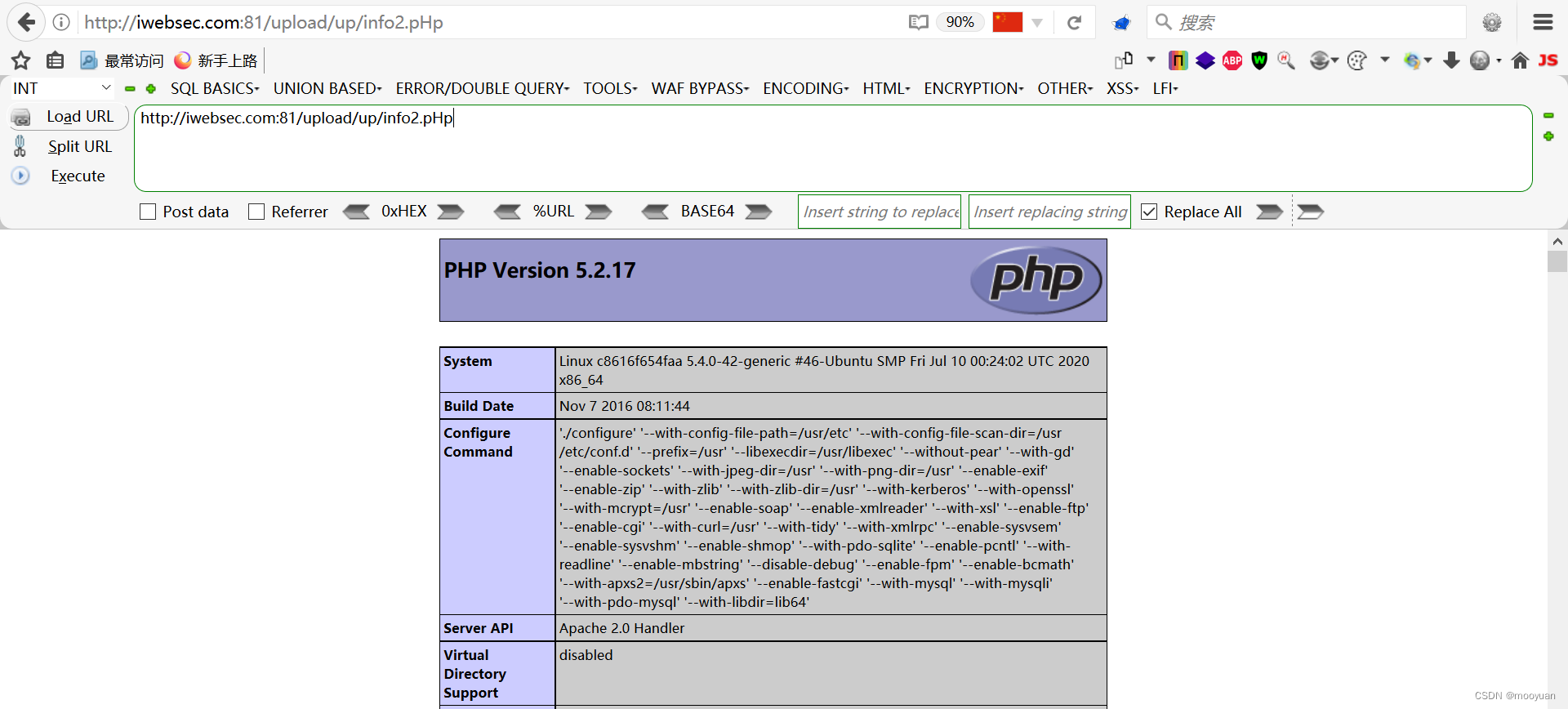

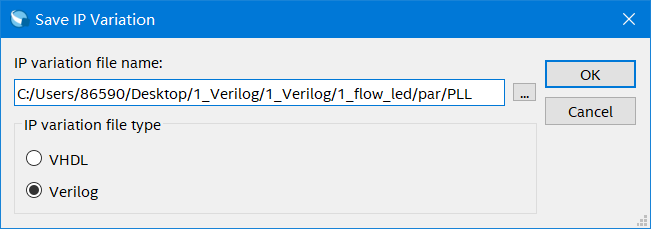

quartus 18的使用方法

像13一样填名字

感觉和quartus13很相像了

![[附源码]JAVA毕业设计文件发布系统(系统+LW)](https://img-blog.csdnimg.cn/3d20e6b5c8f6436ca0043d0b60df7f4c.png)