背板的EMC设计

- 1.背板槽位的排列

- 1.1 单板信号的互联要求

- 1.2 单板板位结构

- 1.2.1 板位结构影响

- 1.2.2 板间互联电平、驱动器件的选择

- 2.背板的EMC设计

- 2.1 接插件的信号排布与EMC设计

- 2.1.1 接插件的选型

- 2.1.2 接插件模型与针信号排布

- 2.2 阻抗匹配

- 2.3 电源、地分配

1.背板槽位的排列

1.1 单板信号的互联要求

当硬件的总体方案确定后,单板的种类、数量已定,所有送到背板上的信号也就确定下来了,在PCB设计过程中,我们要从单板槽位的位置、信号的出线方式等多方面考虑,既实现母板性能指标、又满足EMC的要求。

从信号的速率看,有高速信号与低速信号之分,高速信号通过解复用成低速:背板的板位分配要考虑到高速部分对低速部分的影响。 从EMC设计角度考虑,高速部分会通过传导或辐射的方式影响到低速部分,甚至使设计功能难以实现。要尽可能避免高速信号的镜像电流流入到低速电路的区域里,关键信号,特别是高频、高速信号走线、大电流、强信号走线要尽可能短。由此,对于背板槽位排列,高速板位与低速板位部分要分开,高速部分走线要短,高速板可适当考虑屏蔽。

例如:某产品主要分为高速收发单板XXX、XXX,管理单元处理板XXX,交叉板XXX,以及时钟板XXX,主控与支路板。分别完成复用(解复用)、帧扰码 (解码),开销处理、时钟选收与交叉连接功能。

根据各单板间的互连要求 ,系统的高速部分与低速的支路信号处理部分分开为上 、下两部分,高速的收发板布于系统高速部分的边缘板位 ,减小收发的高速信号对系统内部的干扰 ,同时注意收发板的高速部分加屏蔽。

1.2 单板板位结构

1.2.1 板位结构影响

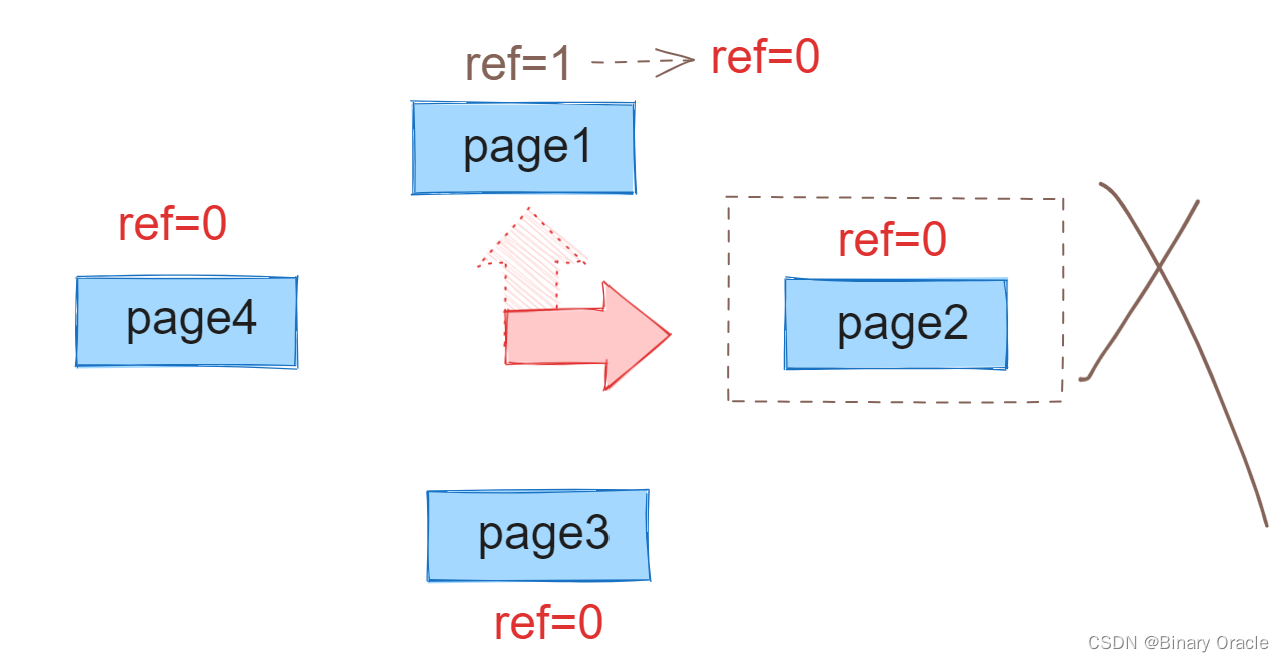

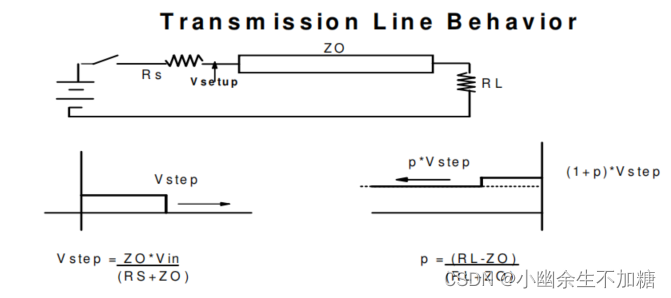

当脉冲信号从源端发出后,沿线端的信号幅度由源内阻与传输线的阻抗之间的分压确定。

当入射波到达负载端时,一些能量变会被反射回源端。反射回去的能量由反射系数来决定。而反射系数则由 传输线的阻抗和负载阻抗来决定。

反射系数值在-1到+1之间。

开路电路的反射系数为+1。当入射波到达一个开路负载端,它将以相同的相位反射回源端。在负载端,电压的幅度将会是入射波形幅度两倍。

短路电路的反射系数为-1。当入射波到达一个短路负载端时,它将反向并以与入射波相反的相位反射回源端。接收负载端的电压叠加后为零伏。

传输线上的阻抗连续的端接称为“匹配”。反射系数为零即没有反射发生。负载端的信号幅度与入射信号的幅度相等。

在信号的传输过程中,还会碰到其他的一些非连续点。例如,直角拐点,过孔,接插件以及IC的封装等可能在其他良好环境下产生波形的扰变。这些阻抗不连续的影响是由系统的速度决定的。在低速下,这些作用可能引入很小的反应。在高速下,结果会变得非常显著。

大多数情况下,驱动器是主要的噪声源,而此噪声可以通过适当的拓扑结构和终端匹配来解决。

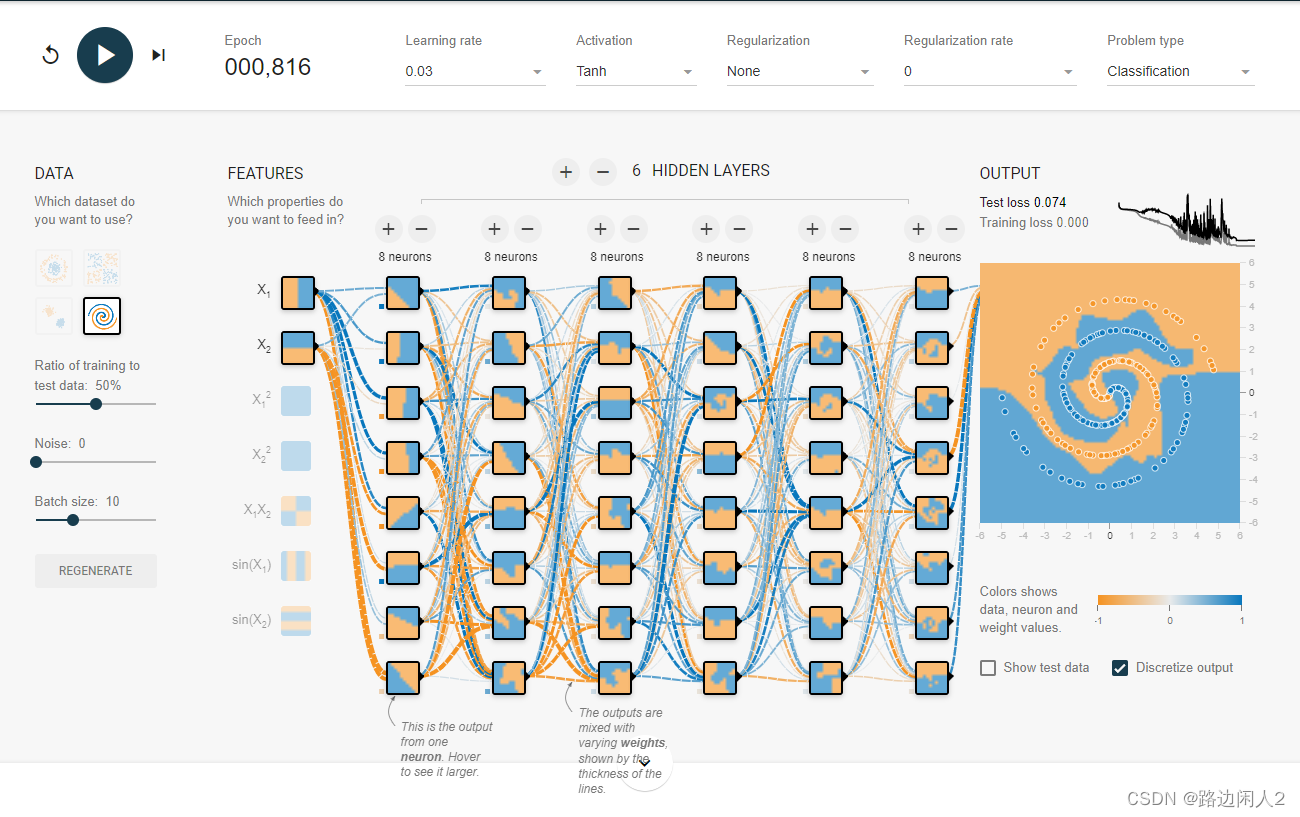

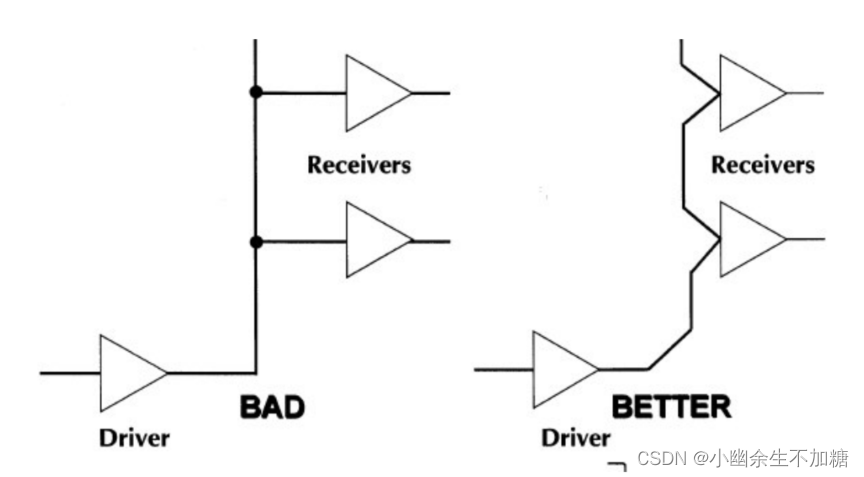

拓扑结构可以有以下几类: 点到点、树形结构、T型、星型、菊花链型。

树形结构---------较长的分支容易造成过载和铃流。

菊花链--------- 对于总线驱动方式和具有终端并联匹配的走线很好,注意尽量不走“T”

型走线。 (见图)。

星型--------- 需要有高驱动能力的缓冲器(低输出阻抗),使用串接匹配。

采用恰当的拓扑结构,可以减小反射,提高信号质量,减少EMI。

对于背板,由于主备板、保护板的存在,不可避免会出现多负载情况,如何合理的安排槽位,使得走线的拓扑结构合理,反射减小,是背板设计相当重要的话题。对于时钟线应尽量实现点对点的驱动,避免总线方的考虑,阻抗匹配原则上首先考虑在相应的单板上处理,不得已情况下考虑在背板上实现匹配,但要注意背板上的元器件应尽可能少。

1.2.2 板间互联电平、驱动器件的选择

背板信号与驱动器件在总体方案设计时就应确定。选择驱动电平要满足背板传输速率的要求,对于传输速率小于100M,含有多负载结构的,背板可选取GTL+电平,器件在满足要求下选用驱动电流小的器件,易于EMI的控制。例如,TI公司的GTL1655、GTL16923之间驱动电流相差近一倍。对于几百兆的信号速率,LVDS电平是很好的选择,其对共模干扰的抑制、匹配方式都易于满足要求,而且电流模式抗干扰能力强,差分电平摆幅小,功耗与EMI大大降低。而对于超过1GHZ的信号,一般用ECL或CML电平信号,可以在普通板材的背板上传送超过2.5G的信号速率。当然,高速背板设计时对于阻抗控制、走线约束、EMC控制等有更高的要求。对于差分信号线要求同层,并且紧邻平行走线,差分线与其他走线设计时应遵循“3W原则”、严格等长等原则,高速差分线对之间以地线隔开。

2.背板的EMC设计

2.1 接插件的信号排布与EMC设计

2.1.1 接插件的选型

现在大多部分的接插件大部分选用2mmHM连接器,2mmHM连接器为首尾拼接式设计,有A、B、C等不同型式。其中A型中部有两个定位块(Function block)起导向定位功能(与单板上连接器的定位),两块中间的腔体可装防插错销。B型完全没有定位功能。C型作为拼接的端部,有部分定位功能。在一连接器拼接组或单个连接器的使用中,必须考虑连接器定位问题。2mm连接器有列间屏蔽与外壳屏蔽两种,实际连接器使用时,应根据地针信号的排布及屏蔽要求等方面考虑选择,从EMC的角度考虑,最好选取带屏蔽外壳的。此外,AMP公司提供有专对高速信号传输使用的HS3接插件,接插件设计时已经考虑了针信号间的屏蔽,高速信号传输时接插件产生的串扰较小,信号针的使用率也较高,但价格较贵。

2.1.2 接插件模型与针信号排布

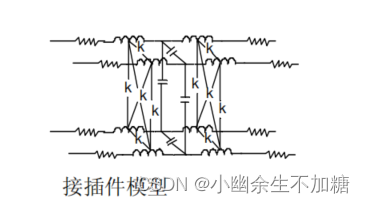

接插件的模型从原理上来看就是传输线的模型,只是信号传输没有参考的地平面,通过地针形成回流通路,因此必然存在许多信号线共用一段地回路,接插件的串扰引起的传导干扰就必须重视。

接插件针信号排布,首先确定信号分配,合理分配信号、电源、地针位置与数量。原则是减少串扰、减小辐射、保证地回路。每个信号针附近最好都有自己的回流路径。关键信号线通过地针与其他信号分隔。考虑带电插拔,对于2mmHM接插件,地插针比电源插针长。分配较长的针脚作为地和电源的连接针。推荐使用地针与信号针成梅花型的排布,按照高速信号、地的针位进行交错排列,以减小串扰。

背板信号走线避免经过密集过孔区(接插件区),密集过孔区是一个参考平面极不连续的区域。如果这样,两条走线共用地回路,产生耦合电感,耦合回路面积加大,使辐射增强。

产生的耦合电感量: L=5dln(d/w),L:inductance,nH, W:线宽,inchd: 地回路经过 过孔区的有效长度可见,电感与过孔区的宽度无关,只与长度有关,因此,从过孔区中间穿过的走线比从边缘穿过的走线影响要大。

2.2 阻抗匹配

相对于单板,背板上走线长度要长许多,因此背板阻抗控制就更为重要。然而由于背板层数较多,阻抗很难控制的与各单板一致,需要在各单板上做文章,而且如前面所述,板位分布造成的拓扑结构不同,使匹配方式也不相同。这时应注意接插件至接口器件的信号线要短,避免线头过长造成的反射影响,减少过孔、直角走线等阻抗不连续的因素出现。

2.3 电源、地分配

与单板一样,电源、地平面的分割对背板EMC的指标有很大的影响。不当的分割造成共模辐射加大。一般在背板中 使用多层板技术,信号层与地层(电源层) 交替排放,尽量避免两层信号层直接相邻。高速信号线布在与地相邻的信号层上。对于部分有相邻布线的PCB,相邻层的布线应垂直分布。

单板的电源是通过背板接入的,通过背板送至各单板。在背板上,BGND 与-48伏线必须就近平行走线或相邻平面排布,输入的一次电源如-48V,如果直接给单板供电,应有局部过载保护措施,如:单板加装保险丝。母板与单板间的电源连接处,也必须采取滤波措施,并就近放置相应的器件。对于分散供电等特殊情况,在背板上-48V不用平面层,用COPPER或粗线代替,可节省母板层数。大电流、强信号走线的距离尽可能短。 高电压、大电流信号电路与小电流,低电压的弱信号电路需完全分开。考虑带电插拔,在被插电路板上应安装带电插拔座,单板上应设置缓启动电路。在单板与母板直接通过连接器配合使用时,单板上的继电器、开关电源等对外辐射强的器件,应尽量远离母板放置,建议距单板连接器边缘10mm以上。

对于背板上BGND、PGND、GND的分割与连接,至今仍缺乏一个统一的认识。 背板的接地需要从系统的高度来考虑。现在的通常做法是插框中所有单板通过与背板的接口信号GNDPGND在背板内实现共地。各插框通过GND、PGND、BGND在机柜内实现共地,机柜再通过接地螺栓与大地相连。各产品具体的接地方法也不尽相同,缺乏统一的规范。从EMC的角度,希望背板上不分PGND与GND,将其合在一起。具体效果正在实验从EMC考虑,带屏蔽的2mm连接器,在其周围15mm以内的地方,禁止放置敏感器件; 母板表面层是完整的屏蔽地平面,即上面不布其他任何信号线。电源与地之间同样需要使它们的回路面积尽可能小。 为减小干扰,一条传输线到地平面的距离应该小于到相邻的传输线的距离。保持地平面完整,会使大部分布线的回流面积减小。

屏蔽层:

需要注意的地方:

1)高速PCB中,考虑到电源平面的边缘效应,所有的电源平面必须小于相邻地平面,向内缩进20H,即保证电源层边缘距相邻地层边缘的距离大于20倍的电源层与地层之间的垂直距离。为了更好地实行20H规则,就要使控制电源和地平面间的厚度。 遵从20H规则会使PCB的电源层与地层间的电容的自谐振频率提高约2-3倍。

- 对于母板上的信号走线,特别是时钟信号线及其他高速信号线离地平面边缘(垂直方向上)至少保持3W以上的距离,尽量使板上的信号走线构成的回路面积尽可能小。这个回路既包括地回路也包括电源回路。

3)不同类型的信号线尽可能间隔开一些,关键信号线周围要有地屏蔽走线,当做回流或保护线。地屏蔽走线要两头接地,且中间部位也要过孔接地,接地过孔间距最好小于入/20 (入 是传输信号的波长),且不相等。除差分线和线对外,地屏蔽走线最好不要共用,也就是说,通常采取的两根信号线之间只加一根地屏蔽线的办法并不能完全消除信号线之间的干扰。

4)为更好的进行EMC控制,可以参照CPCI背板的设计,背板周边设禁止布线区,背板边缘布一圈地并通过一圈金属化孔与子架连接,这样可进一步减小对外辐射。