1、使用正点原子的达芬奇开发板进行第一个FPGA程序设计。

2、启动vivado 2019.2。

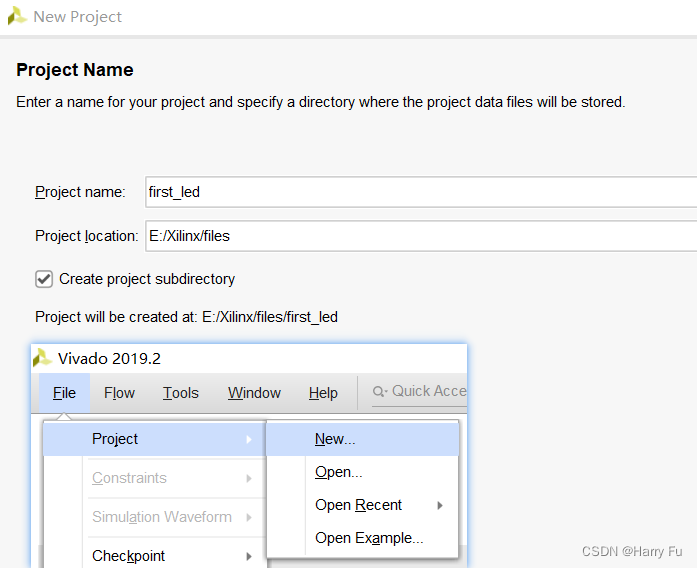

3、 新建工程。

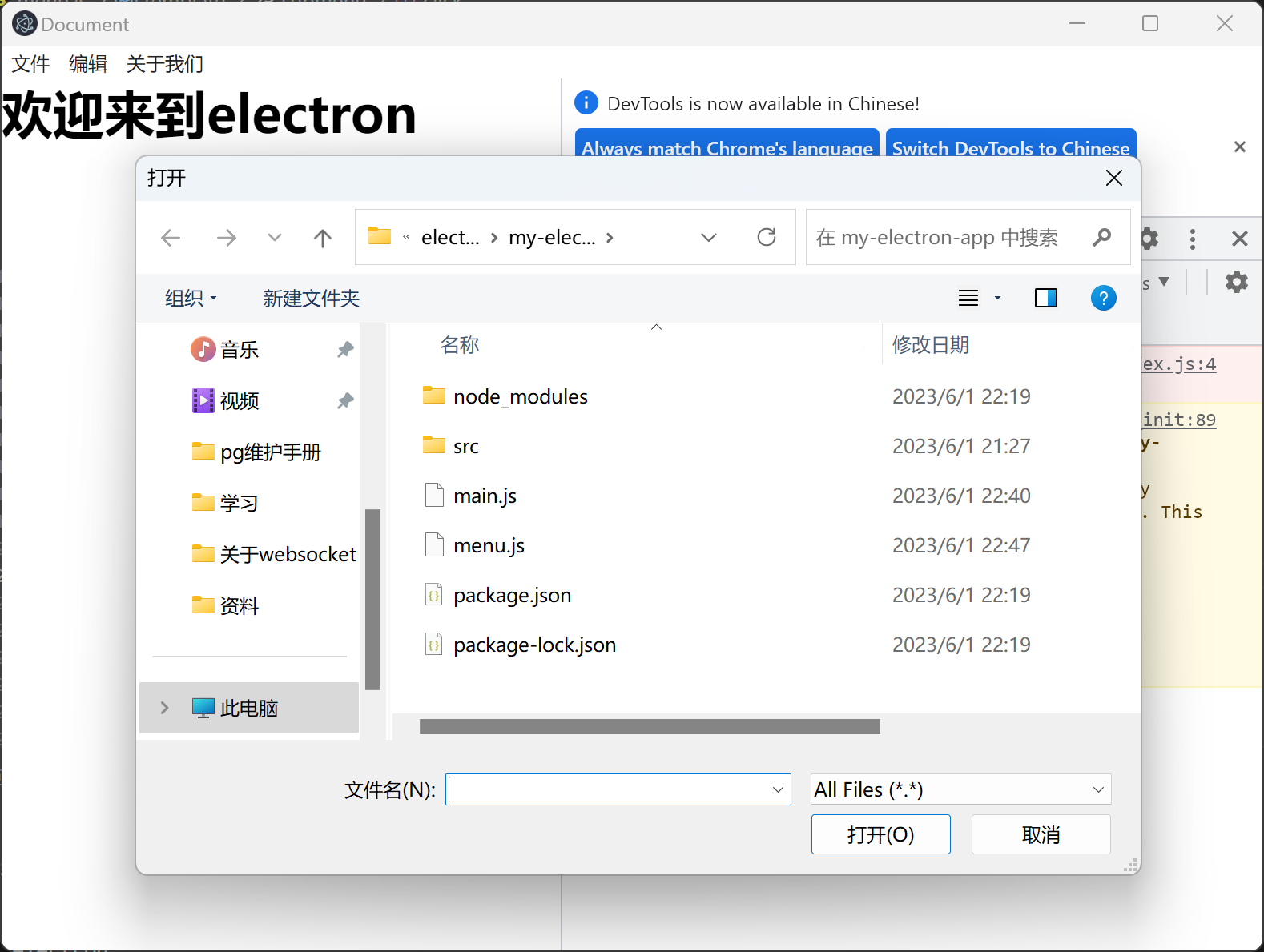

File--Project--New,选择RTL Project(寄存器传输级)。

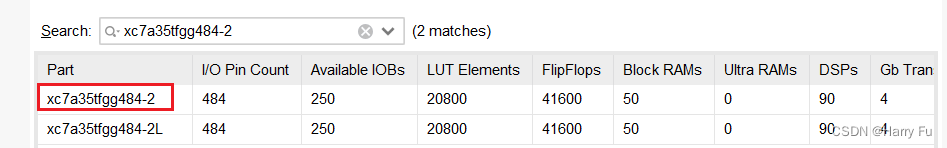

4、选择器件。

add sources点击next,

add constraints点击next,

选择xc7a35tfgg484-2,next,finish。

5、新建源文件。

右键Add Sources,选择Add or create design sources,next,create file,文件名led,finish。

6、编写源文件。

6、编写源文件。

led.v

`timescale 1ns/1ps

module led(

input sys_clk,

input sys_rst_n,

output [1:0] led

);

reg [25:0] cnt;

assign led = (cnt<26'd2500_0000) ? 2'b01 : 2'b10;

always @ (posedge sys_clk or negedge sys_rst_n) begin

if(!sys_rst_n)

cnt <= 26'd0;

else if(cnt < 26'd5000_0000)

cnt <= cnt + 1'b1;

else

cnt <= 26'd0;

end

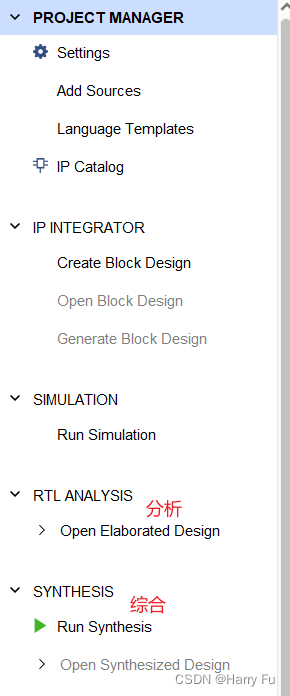

endmodule7、分析和综合。

8、新建约束文件。

右键Add Sources,选择Add or create constraint sources,next,create file,文件名led,finish。

led.xdc

create_clock -name clk -period 20 [get_ports sys_clk]

set_property -dict {PACKAGE_PIN R4 IOSTANDARD LVCMOS33} [get_ports sys_clk]

set_property -dict {PACKAGE_PIN U2 IOSTANDARD LVCMOS33} [get_ports sys_rst_n]

set_property -dict {PACKAGE_PIN R2 IOSTANDARD LVCMOS33} [get_ports {led[0]}]

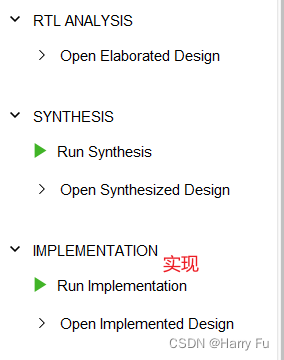

set_property -dict {PACKAGE_PIN R3 IOSTANDARD LVCMOS33} [get_ports {led[1]}]9、实现。

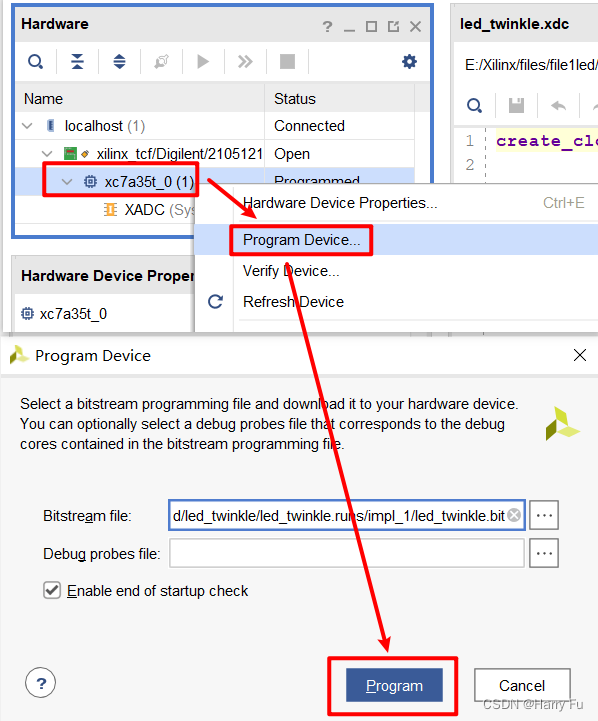

10、生成并下载比特流。

Generate Bitstream生成比特流。

Open Hardware Manager打开硬件管理,Auto Connect自动连接,右键Program Device编程器件。