一:要点

1.如果两片AD,四路输出做了同步化处理之后,一定只用同步化模块读时钟(一片AD的时钟)去上传数据,到DDR3模块。

2.ADS42和LTC2208的ADC的数据伴随时钟都来源与输入的采样时钟(有些采样时钟可以做分频处理)

3.数据溢出标志的含义:当模拟电压输入超过ADC芯片电压的范围就会产生在溢出标志位上

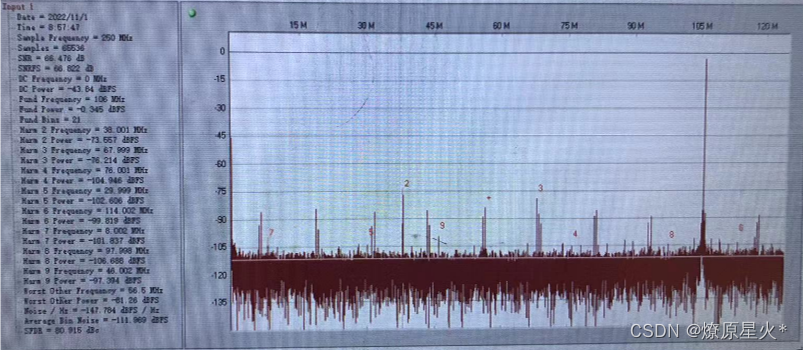

4.ADI的分析软件中的fund power指标就功率(幅度)0dBFS为满幅(一般2vpp),但是考虑到满幅度后可能会溢出导致指标异常常,所以回退到-1dBFS为满幅时 来看指标是否满足客户要求。——此时有可能信号源的幅度为10dbm

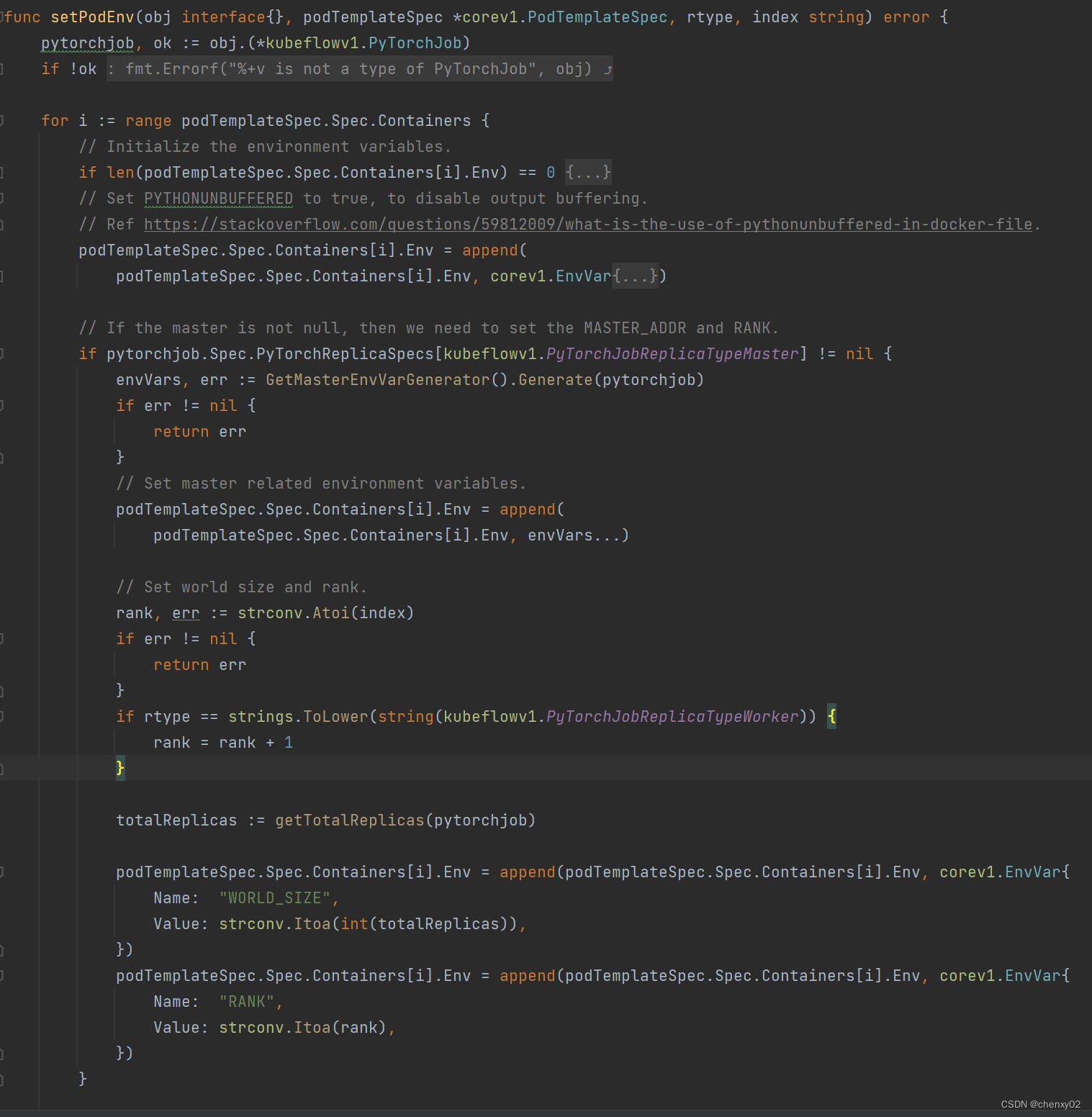

5.在进行数据验证时,也可以使用测试模式,对收发数据进行验证以保证系统的正确性。另外,还可以对输入时钟进行延时调节或者通过SelectIO的delay、delayctrl功能对时钟信号进行微调(实际工程采用对数据进行微调 ),以满足时序要求。

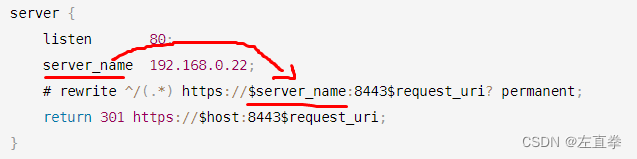

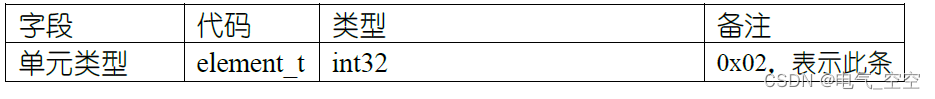

6.ADS42LB69数据格式配置为“DDR LVDS Interface Timing”。只需配置 Register 15 为“0X01h”。

7.此款ADC的指标如下:

双通道

14 和 16 位分辨率

最大时钟速率:250MSPS

支持高阻抗输入的模拟输入缓冲器

支持 1 分频,2 分频和 4 分频的灵活输入时钟缓冲器

2VPP 和 2.5VPP 差分满量程输入(SPI 可编程)

双倍数据速率 (DDR)或四倍数据速率 (QDR)低压差分信令 (LVDS)接口

功耗:820mW/通道

间隙抖动:85 fs

通道隔离(指的时两个模拟通道的隔离度):100dB